Intel

£

Advanced+ Boot Block Flash Memory (C3)

Datasheet 39

8.0 AC Characteristics

8.1 AC Read Characteristics

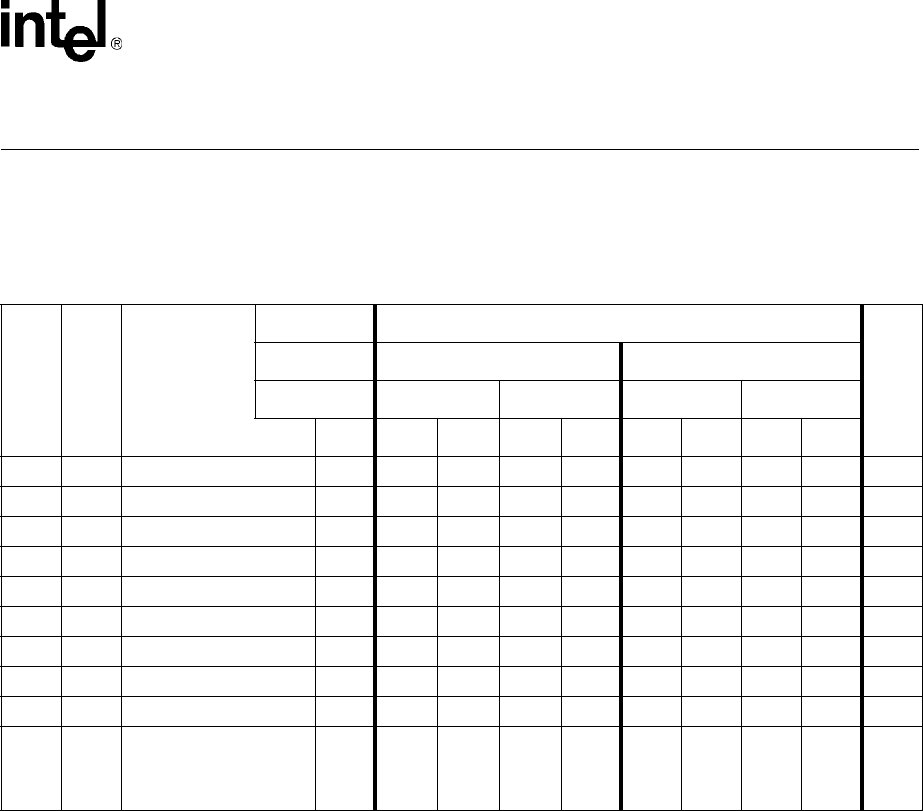

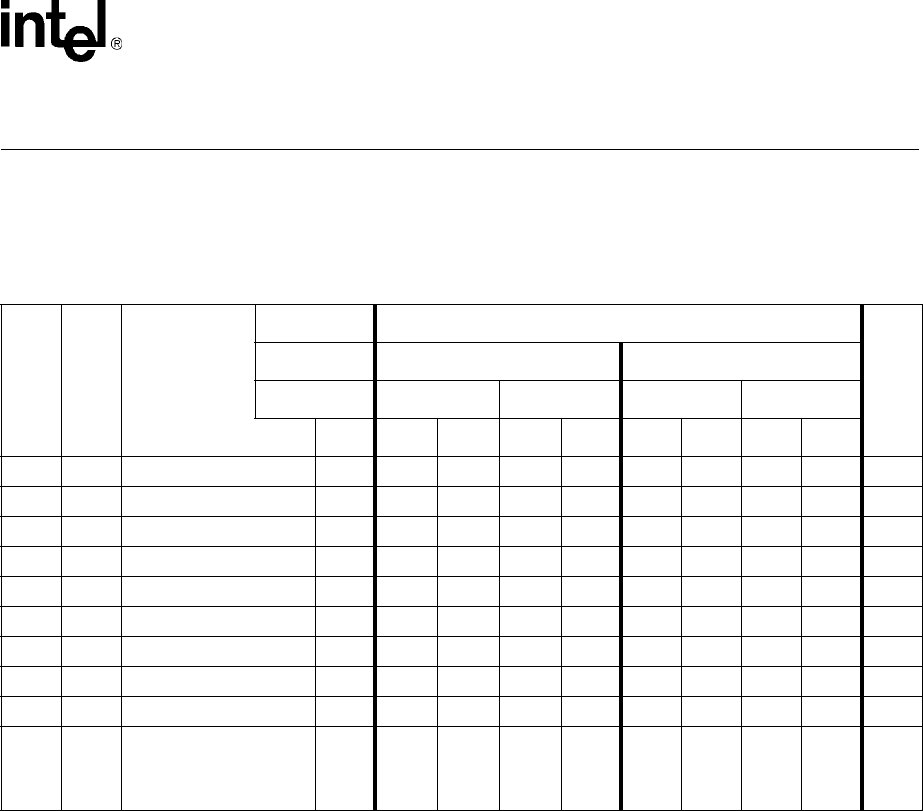

Table 13. Read Operations—8 Mbit Density

#Sym Parameter

Density 8 Mbit

Unit

Product 90 ns 110 ns

V

CC

3.0V–3.6V 2.7V–3.6V 3.0V–3.6V 2.7V–3.6V

Note Min Max Min Max Min Max Min Max

R1 t

AVAV

Read Cycle Time 3,4 80 90 100 110 ns

R2 t

AVQV

Address to Output Delay 3,4 80 90 100 110 ns

R3 t

ELQV

CE# to Output Delay 1,3,4 80 90 100 110 ns

R4 t

GLQV

OE# to Output Delay 1,3,4 30 30 30 30 ns

R5 t

PHQV

RP# to Output Delay 3,4 150 150 150 150 ns

R6 t

ELQX

CE# to Output in Low Z 2,3,4 0 0 0 0 ns

R7 t

GLQX

OE# to Output in Low Z 2,3,4 0 0 0 0 ns

R8 t

EHQZ

CE#toOutputinHighZ 2,3,4 20 20 20 20 ns

R9 t

GHQZ

OE#toOutputinHighZ 2,3,4 20 20 20 20 ns

R10 t

OH

Output Hold from

Address, CE#, or OE#

Change, Whichever

Occurs First

2,3,4 0 0 0 0 ns

NOTES:

1.OE#maybedelayeduptot

ELQV–

t

GLQV

after the falling edge of CE# without impact on t

ELQV

.

2. Sampled, but not 100% tested.

3. See Figure 8, “Read Operation Waveform” on page 42.

4. See Figure 11, “AC Input/Output Reference Waveform” on page 49 for timing measurements and maximum allowable input

slew rate.