TAS5518C

8-ChannelDigitalAudioPWMProcessor

SLES238A–SEPTEMBER2008–REVISEDJULY2009

www.ti.com

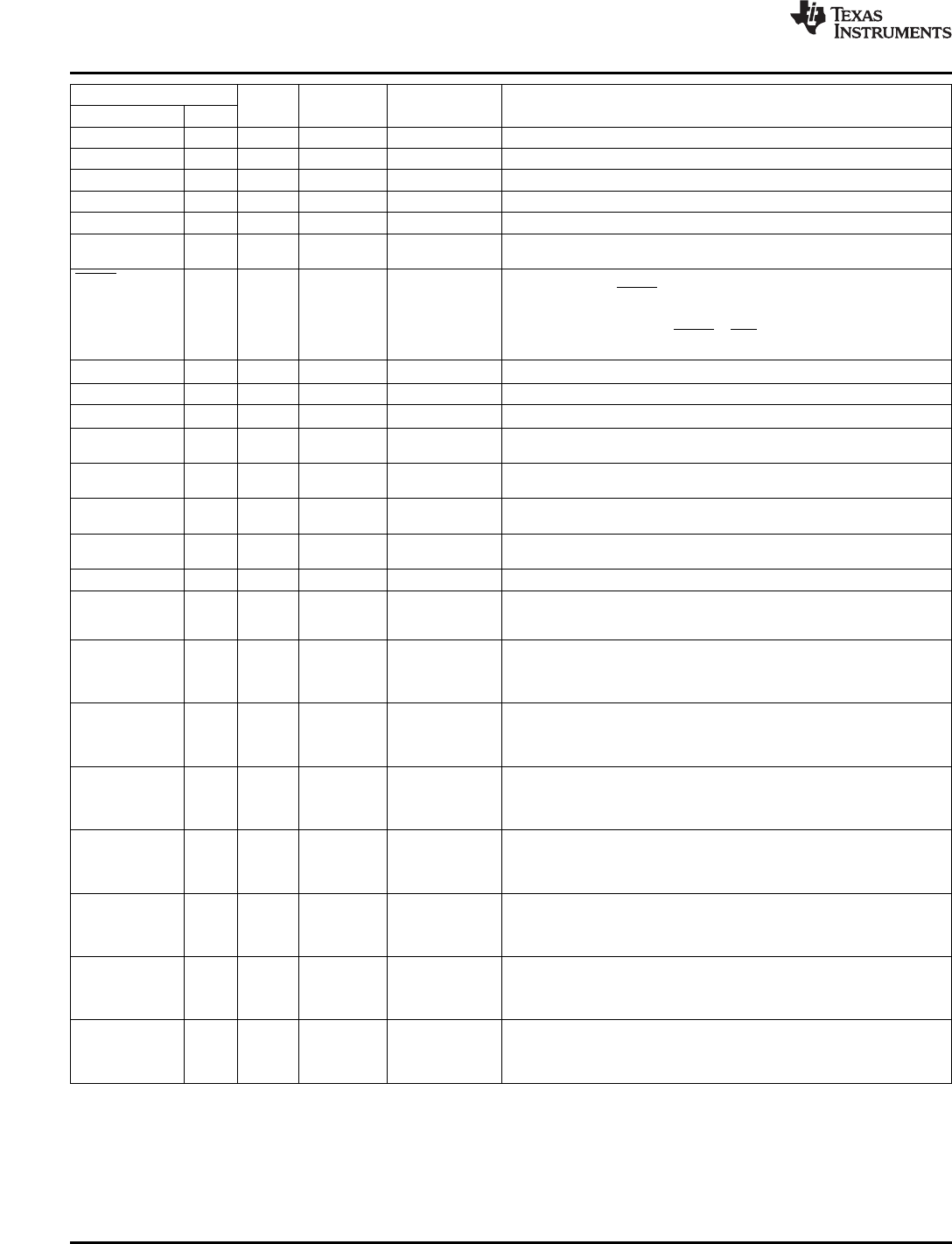

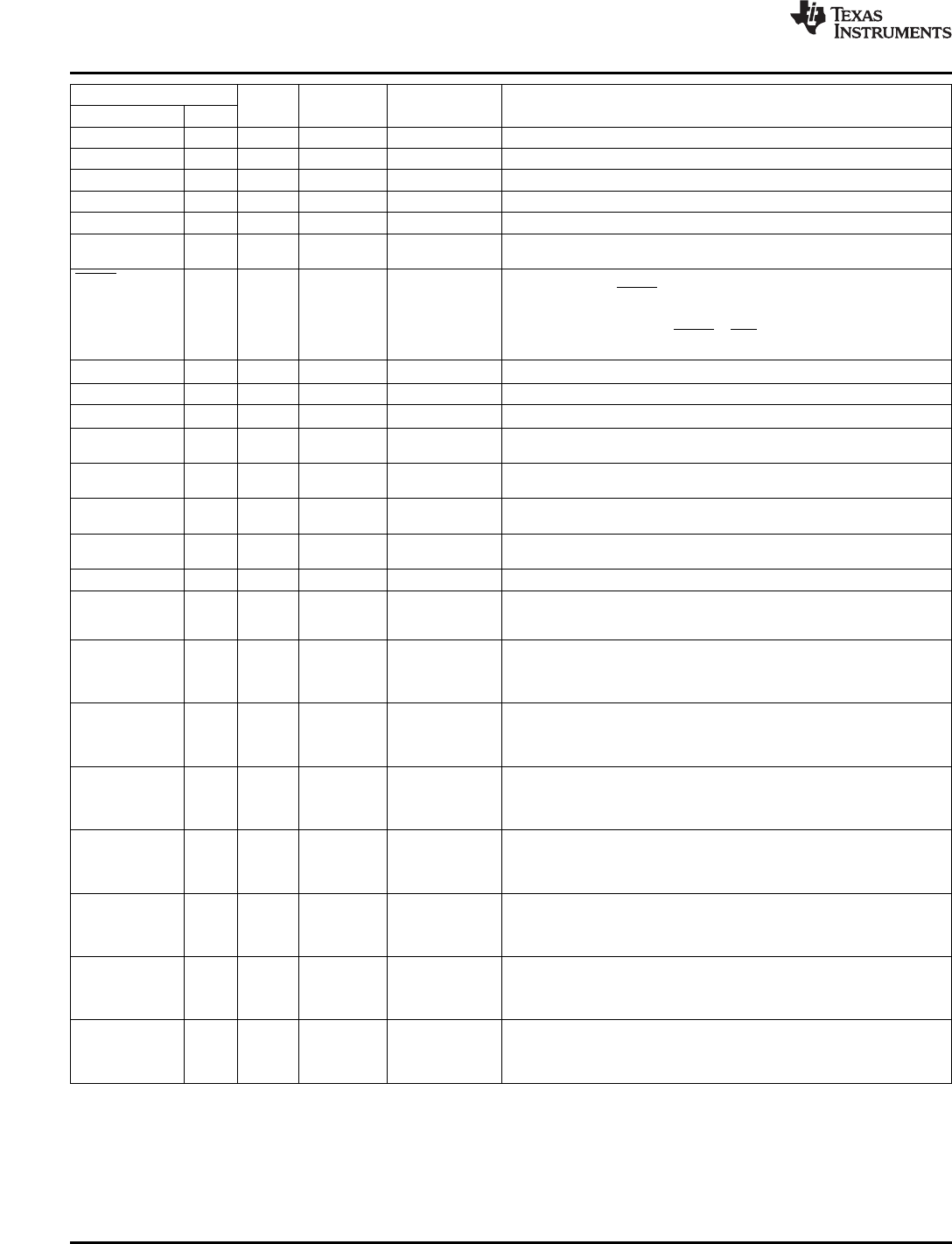

TERMINAL

5-V

TYPE

(1)

TERMINATION

(2)

DESCRIPTION

TOLERANT

NAMENO.

PWM_P_447DOPWM4output(differential+)

PWM_P_556DOPWM5output(lineoutL)(differential+)

PWM_P_658DOPWM6output(lineoutR)(differential+)

PWM_P_750DOPWM7output(differential+)

PWM_P_852DOPWM8output(differential+)

RESERVED21,22,Connecttodigitalground

23,64

RESET 11DI5VPullupSystemresetinput,active-low.Asystemresetisgeneratedbyapplyingalogic

lowtothisterminal.RESETisanasynchronouscontrolsignalthatrestoresthe

TAS5518Ctoitsdefaultconditions,setsthevalidoutputlow,andplacesthe

PWMinthehard-mutestate(M-state).Mastervolumeisimmediatelysettofull

attenuation.OnthereleaseofRESET,ifPDNishigh,thesystemperformsa4-

to5-msdeviceinitializationandsetsthevolumeatmute.

SCL25DI5V

I

2

Cserial-controlclockinput/output

SCLK27DI5VSerial-audiodataclock(shiftclock)input

SDA24DIO5V

I

2

Cserial-controldata-interfaceinput/output

SDIN131DI5VPulldownSerial-audiodatainput1isoneoftheserial-datainputports.SDIN1supports

fourdiscrete(stereo)dataformatsandiscapableofinputtingdataat64f

S

.

SDIN230DI5VPulldownSerial-audiodatainput2isoneoftheserial-datainputports.SDIN2supports

fourdiscrete(stereo)dataformatsandiscapableofinputtingdataat64f

S

.

SDIN329DI5VPulldownSerial-audiodatainput3isoneoftheserial-datainputports.SDIN3supports

fourdiscrete(stereo)dataformatsandiscapableofinputtingdataat64f

S

.

SDIN428DI5VPulldownSerial-audiodatainput4isoneoftheserial-datainputports.SDIN4supports

fourdiscrete(stereo)dataformatsandiscapableofinputtingdataat64f

S

.

VALID39DOOutputindicatingvalidityofPWMoutputs,active-high

VBGAP10PBand-gapvoltagereference.Apinoutoftheinternallyregulated1.2-Vreference.

Typicallyhasa1-nFlow-ESRcapacitorbetweenVBGAPandAVSS_PLL.This

terminalmustnotbeusedtopowerexternaldevices.

VR_DIG33PVoltagereferencefor1.8-Vdigitalcoresupply.Apinoutoftheinternally

regulated1.8-Vpowerusedbydigitalcorelogic.A4.7-µFlow-ESRcapacitor

(3)

shouldbeconnectedbetweenthisterminalandDVSS.Thisterminalmustnot

beusedtopowerexternaldevices.

VR_DPLL17PVoltagereferencefor1.8-VdigitalPLLsupply.Apinoutoftheinternally

regulated1.8-VpowerusedbydigitalPLLlogic.A0.1-µFlow-ESRcapacitor

(3)

shouldbeconnectedbetweenthisterminalandDVSS_CORE.Thisterminal

mustnotbeusedtopowerexternaldevices.

VR_PWM48PVoltagereferencefor1.8-VdigitalPWMcoresupply.Apinoutoftheinternally

regulated1.8-VpowerusedbydigitalPWMcorelogic.A0.1-µFlow-ESR

capacitor

(3)

shouldbeconnectedbetweenthisterminalandDVSS_PWM.This

terminalmustnotbeusedtopowerexternaldevices.

VRA_PLL1PVoltagereferencefor1.8-VPLLanalogsupply.Apinoutoftheinternally

regulated1.8-VpowerusedbyPLLlogic.A0.1-µFlow-ESRcapacitor

(3)

should

beconnectedbetweenthisterminalandAVSS_PLL.Thisterminalmustnotbe

usedtopowerexternaldevices.

VRD_PLL7PVoltagereferencefor1.8-VPLLdigitalsupply.Apinoutoftheinternally

regulated1.8-VpowerusedbyPLLlogic.A0.1-µFlow-ESRcapacitor

(3)

should

beconnectedbetweenthisterminalandAVSS_PLL.Thisterminalmustnotbe

usedtopowerexternaldevices.

XTL_IN20AIXTL_OUTandXTL_INaretheonlyLVCMOSterminalsonthedevice.They

provideareferenceclockfortheTAS5518Cviauseofanexternal

fundamental-modecrystal.XTL_INisthe1.8-Vinputportfortheoscillator

circuit.A13.5-MHzcrystal(HCM49)isrecommended.

XTL_OUT19AOXTL_OUTandXTL_INaretheonlyLVCMOSterminalsonthedevice.They

provideareferenceclockfortheTAS5518Cviauseofanexternal

fundamental-modecrystal.XTL_OUTisthe1.8-Voutputdrivetothecrystal.A

13.5-MHzcrystal(HCM49)isrecommended.

(3)Ifdesired,low-ESRcapacitancevaluescanbeimplementedbyparallelingtwoormoreceramiccapacitorsofequalvalue.Paralleling

capacitorsofequalvalueprovidesanextendedhigh-frequencysupplydecoupling.Thisapproachavoidsthepotentialofproducing

parallelresonancecircuitsthathavebeenobservedwhenparallelingcapacitorsofdifferentvalues.

Description 16SubmitDocumentationFeedback

Not Recommended For New Designs