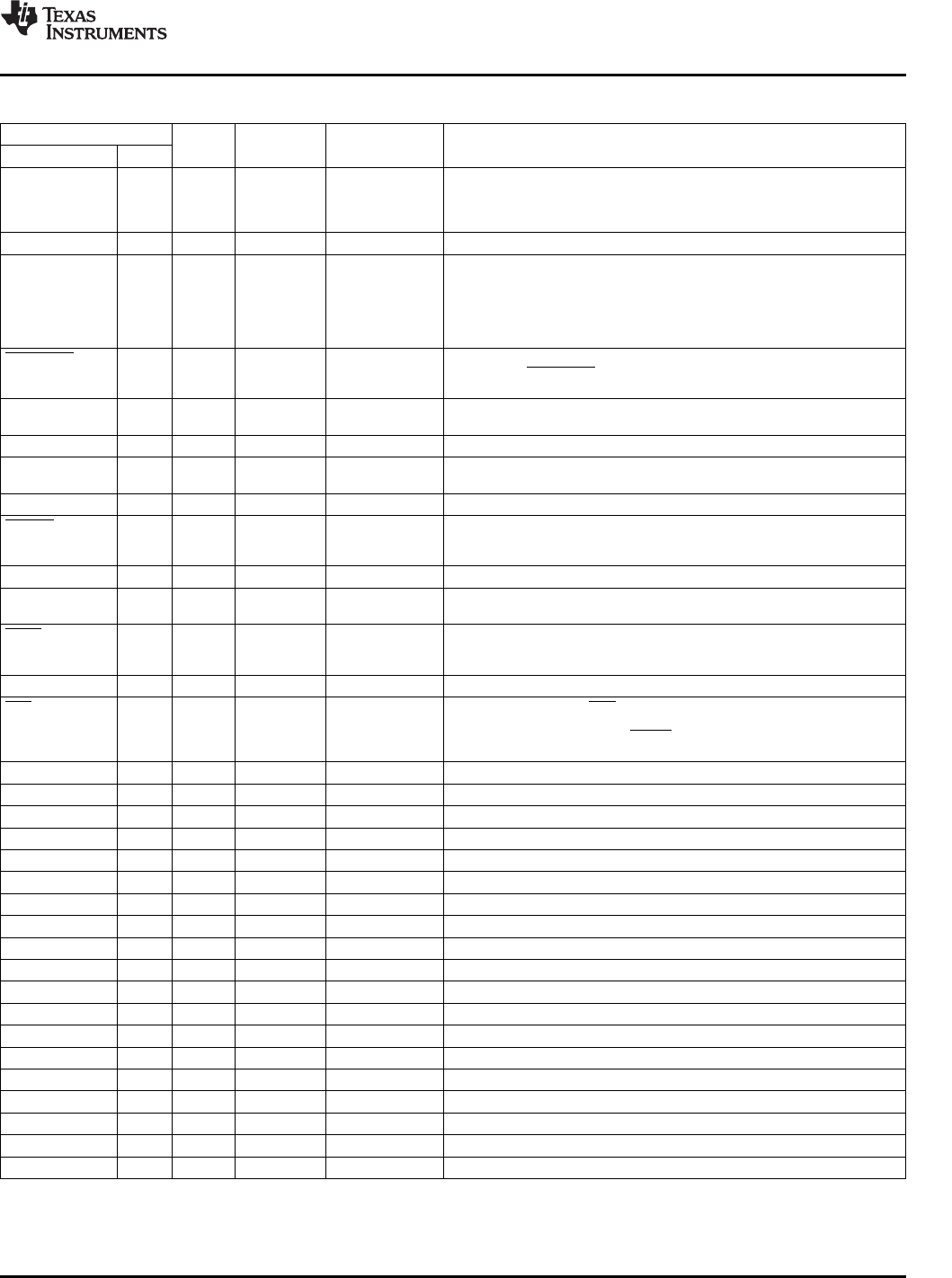

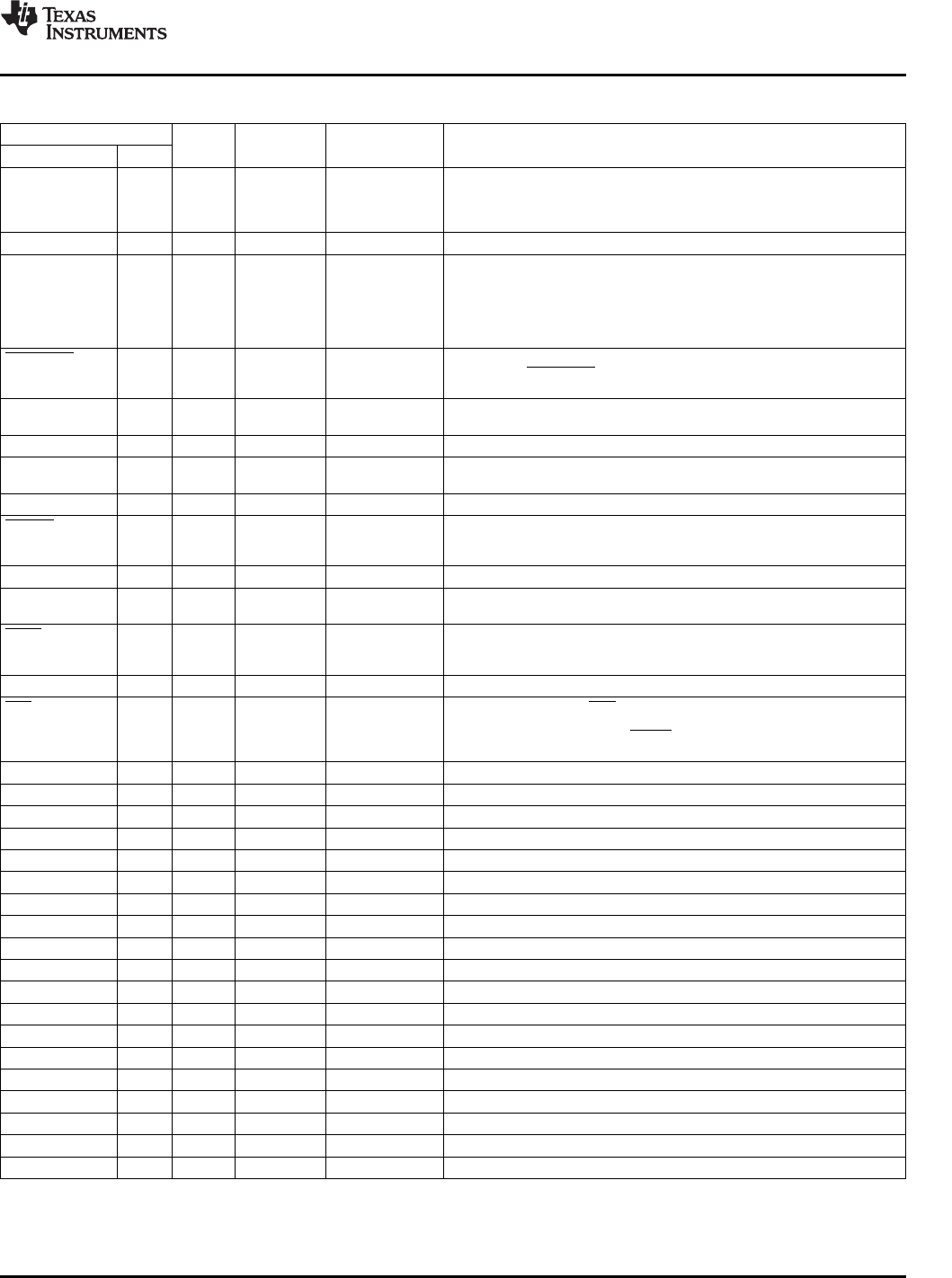

2.1.3TerminalDescriptions

TAS5518C

8-ChannelDigitalAudioPWMProcessor

www.ti.com

SLES238A–SEPTEMBER2008–REVISEDJULY2009

TERMINAL

5-V

TYPE

(1)

TERMINATION

(2)

DESCRIPTION

TOLERANT

NAMENO.

AVDD_PLL9P3.3-VanalogpowersupplyforPLL.Thisterminalcanbeconnectedtothesame

powersourceusedtodrivepowerterminalDVDD;buttoachievelowPLLjitter,

thisterminalshouldbebypassedtoAVSS_PLLwitha0.1-µFlow-ESR

capacitor.

AVSS5,6PAnalogground

AVSS_PLL8PAnaloggroundforPLL.Thisterminalshouldreferencethesamegroundas

terminalDVSS;buttoachievelowPLLjitter,groundnoiseatthisterminalmust

beminimized.TheavailabilityoftheAVSSterminalallowsadesignertouse

optimizingtechniquessuchasstargroundconnections,separategroundplanes,

orotherquietground-distributiontechniquestoachieveaquietgroundreference

atthisterminal.

BKND_ERR37DIPullupActive-low.Aback-enderrorsequenceisgeneratedbyapplyinglogiclowtothis

terminal.TheBKND_ERRresultsinnochangetoanysystemparameters,with

allH-bridgedrivesignalsgoingtoahard-mutestate(M-state).

DVDD15,36P3.3-Vdigitalpowersupply.Itisrecommendedthatdecouplingcapacitorsof

0.1µFand10µFbemountedclosetothispin(seeapplicationschematics).

DVDD_PWM54P3.3-VdigitalpowersupplyforPWM

DVSS16,34,PDigitalground

35,38

DVSS_PWM53PDigitalgroundforPWM

HP_SEL12DI5VPullupHeadphonein/outselector.Whenalogiclowisapplied,theheadphoneis

selected(speakersareoff).Whenalogichighisapplied,speakersareselected

(headphoneisoff).

LRCLK26DI5VSerial-audiodataleft/rightclock(sampling-rateclock)

MCLK63DI5VPulldownMCLKisa3.3-Vmasterclockinput.Theinputfrequencyofthisclockcanrange

from4MHzto50MHz.

MUTE14DI5VPullupSoftmuteofoutputs,active-low(mutedsignal=alogiclow,normaloperation=

alogichigh).Themutecontrolprovidesanoiselessvolumeramptosilence.

Releasingmuteprovidesanoiselessramptopreviousvolume.

OSC_CAP18AOOscillatorcapacitor

PDN13DI5VPullupPowerdown,active-low.PDNpowersdownalllogicandstopsallclocks

wheneveralogiclowisapplied.Theinternalparametersarepreservedthrough

apower-downcycle,aslongasRESETisnotactive.Thedurationforsystem

recoveryfrompowerdownis100ms.

PLL_FLT_RET2AOPLLexternalfilterreturn

PLL_FLTM3AOPLLnegativeinput.ConnectedtoPLL_FLT_RETviaanRCnetwork

PLL_FLTP4AIPLLpositiveinput.ConnectedtoPLL_FLT_RETviaanRCnetwork

PSVC32OPower-supplyvolumecontrolPWMoutput

PWM_HPML59DOPWMleft-channelheadphone(differential–)

PWM_HPMR61DOPWMright-channelheadphone(differential–)

PWM_HPPL60DOPWMleft-channelheadphone(differential+)

PWM_HPPR62DOPWMright-channelheadphone(differential+)

PWM_M_140DOPWM1output(differential–)

PWM_M_242DOPWM2output(differential–)

PWM_M_344DOPWM3output(differential–)

PWM_M_446DOPWM4output(differential–)

PWM_M_555DOPWM5output(lineoutL)(differential–)

PWM_M_657DOPWM6output(lineoutR)(differential–)

PWM_M_749DOPWM7output(differential–)

PWM_M_851DOPWM8output(differential–)

PWM_P_141DOPWM1output(differential+)

PWM_P_243DOPWM2output(differential+)

PWM_P_345DOPWM3output(differential+)

(1)Type:A=analog;D=3.3-Vdigital;P=power/ground/decoupling;I=input;O=output

(2)Allpullupsare20-µAweakpullupsandallpulldownsare20-µAweakpulldowns.Thepullupsandpulldownsareincludedtoensure

properinputlogiclevelsiftheterminalsareleftunconnected(pullups→logic-1input;pulldowns→logic-0input).Devicesthatdrive

inputswithpullupsmustbeabletosink20µAwhilemaintainingalogic-0drivelevel.Devicesthatdriveinputswithpulldownsmustbe

abletosource20µAwhilemaintainingalogic-1drivelevel.

SubmitDocumentationFeedbackDescription15

Not Recommended For New Designs