7.20DRC2ControlRegister,Channel8(0x97)

7.21DRC1DataRegisters(0x98–0x9C)

TAS5518C

8-ChannelDigitalAudioPWMProcessor

SLES238A–SEPTEMBER2008–REVISEDJULY2009

www.ti.com

Notethattheremustbea10-msdelaybetweenawritetoregister0x96andawritetoregister0x97.

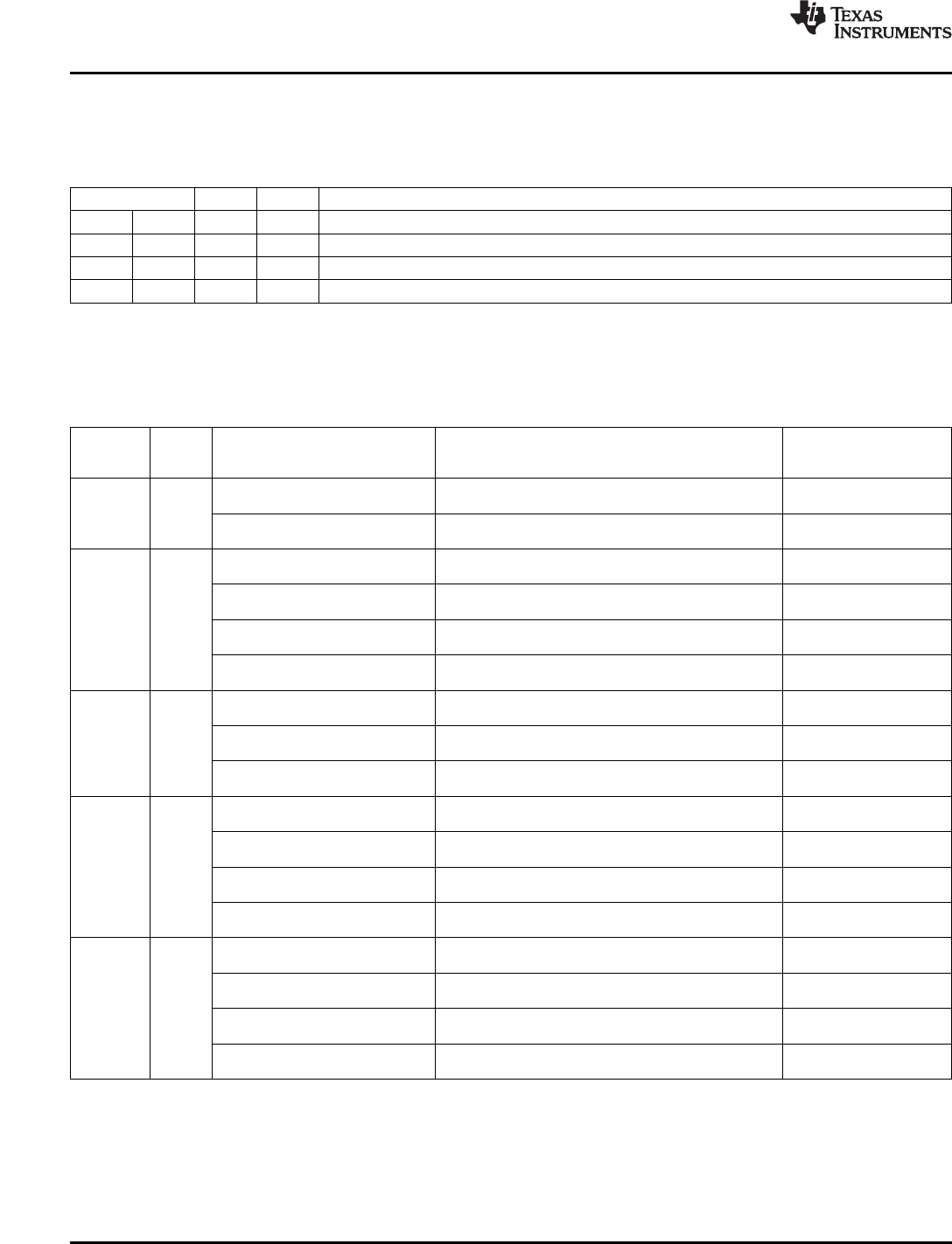

Table7-21.Channel-8DRC2ControlRegisterFormat

D31–D2D1D0FUNCTION

0000Channel8(noder):noDRC

0001Channel8(noder):pre-volumeDRC

0010Channel8(noder):post-volumeDRC

0011Channel8(noder):noDRC

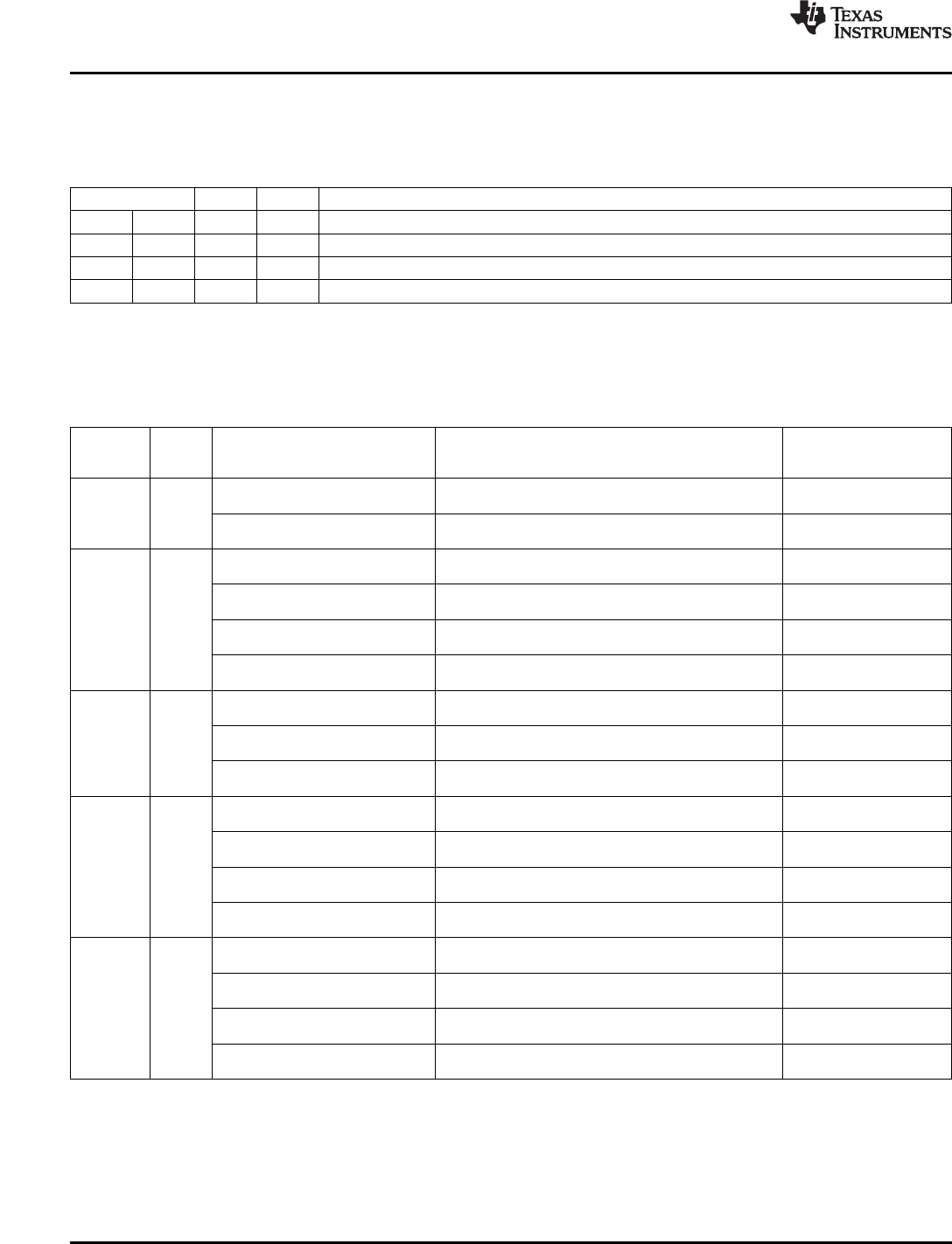

DRC1appliestochannels1,2,3,4,5,6,and7.

Table7-22.DRC1DataRegisterFormat

I

2

C

TOTAL

REGISTERNAMEDESCRIPTIONOFCONTENTSDEFAULTSTATE

SUB-

BYTES

ADDRESS

Channel1,2,3,4,5,6,and7DRC1u[31:28],E[27:24],E[23:16],E[15:8],E[7:0]0x00,0x00,0x88,0x3F

energy

0x988

Channel1,2,3,4,5,6,and7DRC1u[31:28],1–E[27:24],1–E[23:16],1–E[15:8],1–E[7:0]0x00,0x7F,0x77,0xC0

(1–energy)

Channel1,2,3,4,5,6,and7DRC1u[31:24],u[23:16],T1[15:8],T1[7:0]0x00,0x00,0x00,0x00

thresholdupper16bits(T1)

Channel1,2,3,4,5,6,and7DRC1T1[31:24],T1[23:16],T1[15:8],T1[7:0]0x0B,0x20,0xE2,0xB2

thresholdlower32bits(T1)

0x9916

Channel1,2,3,4,5,6,and7DRC1u[31:24],u[23:16],T2[15:8],T2[7:0]0x00,0x00,0x00,0x00

thresholdupper16bits(T2)

Channel1,2,3,4,5,6,and7DRC1T2[31:24],T2[23:16],T2[15:8],T2[7:0]0x06,0xF9,0xDE,0x58

thresholdlower32bits(T2)

Channel1,2,3,4,5,6,and7DRC1u[31:28],k0[27:24],k0[23:16],k0[15:8],k0[7:0]0x00,0x40,0x00,0x00

slope(k0)

Channel1,2,3,4,5,6,and7DRC1u[31:28],k1[27:24],k1[23:16],k1[15:8],k1[7:0]0x0F,0xC0,0x00,0x00

0x9A12

slope(k1)

Channel1,2,3,4,5,6,and7DRC1u[31:28],k2[27:24],k2[23:16],k2[15:8],k2[7:0]0x0F,0x90,0x00,0x00

slope(k2)

Channel1,2,3,4,5,6,and7DRC1u[31:24],u[23:16],O1[15:8],O1[7:0]0x00,0x00,0xFF,0xFF

offset-1upper16bits(O1)

Channel1,2,3,4,5,6,and7DRC1O1[31:24],O1[23:16],O1[15:8],O1[7:0]0xFF,0x82,0x30,0x98

offset-1lower32bits(O1)

0x9B16

Channel1,2,3,4,5,6,and7DRC1u[31:24],u[23:16],O2[15:8],O2[7:0]0x00,0x00,0x00,0x00

offset-2upper16bits(O2)

Channel1,2,3,4,5,6,and7DRC1O2[31:24],O2[23:16],O2[15:8],O2[7:0]0x01,0x95,0xB2,0xC0

offset-2lower32bits(O2)

Channel1,2,3,4,5,6,and7DRC1u[31:28],A[27:24],A[23:16],A[15:8],A[7:0]0x00,0x00,0x88,0x3F

attack

Channel1,2,3,4,5,6,and7DRC1u[31:28],1–A[27:24],1–A[23:16],1–A[15:8],1–A[7:0]0x00,0x7F,0x77,0xC0

(1–attack)

0x9C16

Channel1,2,3,4,5,6,and7DRC1u[31:28],D[27:24],D[23:16],D[15:8],D[7:0]0x00,0x00,0x00,0x56

decay

Channel1,2,3,4,5,6,and7DRC1u[31:28],1–D[27:24],1–D[23:16],1–D[15:8],1–D[7:0]0x00,0x3F,0xFF,0xA8

(1–decay)

Serial-ControlInterfaceRegisterDefinitions 86SubmitDocumentationFeedback

Not Recommended For New Designs