5.2Single-andMultiple-ByteTransfers

5.3Single-ByteWrite

A6 A5 A4 A3 A2 A1 A0

R/W

ACK A7 A6 A5 A4 A3 A2 A1 A0 ACK D7 D6 D5 D4 D3 D2 D1 D0 ACK

Start

Condition

Stop

Condition

Acknowledge Acknowledge Acknowledge

I CDevice Addressand

2

Read/WriteBit

Subaddress DataByte

T0036-01

TAS5518C

8-ChannelDigitalAudioPWMProcessor

SLES238A–SEPTEMBER2008–REVISEDJULY2009

www.ti.com

Theserial-controlinterfacesupportsbothsingle-byteandmultiple-byteread/writeoperationsforstatus

registersandthegeneralcontrolregistersassociatedwiththePWM.However,fortheDAPdata

processingregisters,theserial-controlinterfacesupportsonlymultiple-byte(four-byte)read/write

operations.

Duringmultiple-bytereadoperations,theTAS5518Crespondswithdata,abyteatatime,startingatthe

subaddressassigned,aslongasthemasterdevicecontinuestorespondwithacknowledges.Ifa

particularsubaddressdoesnotcontain32bits,theunusedbitsarereadaslogic0.

Duringmultiple-bytewriteoperations,theTAS5518Ccomparesthenumberofbytestransmittedtothe

numberofbytesthatarerequiredforeachspecificsubaddress.Ifawritecommandisreceivedfora

biquadsubaddress,theTAS5518Cexpectstoreceivefive32-bitwords.Iffewerthanfive32-bitdata

wordshavebeenreceivedwhenastopcommand(oranotherstartcommand)isreceived,thedata

receivedisdiscarded.Similarly,ifawritecommandisreceivedforamixercoefficient,theTAS5518C

expectstoreceiveone32-bitword.

SupplyingasubaddressforeachsubaddresstransactionisreferredtoasrandomI

2

Caddressing.The

TAS5518CalsosupportssequentialI

2

Caddressing.Forwritetransactions,ifasubaddressisissued

followedbydataforthatsubaddressandthe15subaddressesthatfollow,asequentialI

2

Cwrite

transactionhastakenplace,andthedataforall16subaddressesissuccessfullyreceivedbythe

TAS5518C.ForI

2

Csequentialwritetransactions,thesubaddressthenservesasthestartaddressandthe

amountofdatasubsequentlytransmitted,beforeastoporstartistransmitted,determineshowmany

subaddressesarewritten.Asistrueforrandomaddressing,sequentialaddressingrequiresthata

completesetofdatabetransmitted.Ifonlyapartialsetofdataiswrittentothelastsubaddress,thedata

forthelastsubaddressisdiscarded.However,allotherdatawrittenisaccepted;onlytheincompletedata

isdiscarded.

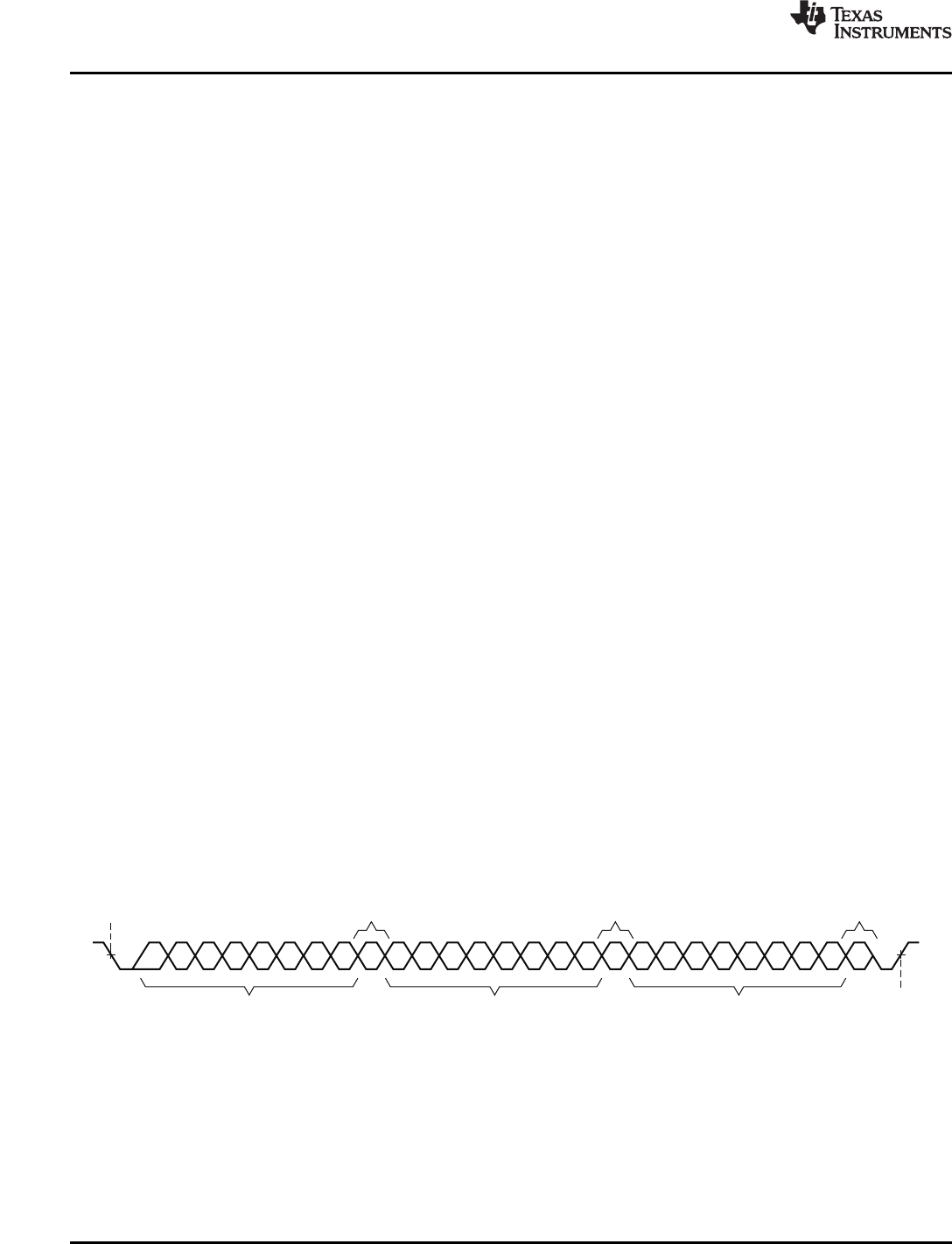

AsshowninFigure5-2,asingle-byte,data-writetransferbeginswiththemasterdevicetransmittingastart

conditionfollowedbytheI

2

Cdeviceaddressandtheread/writebit.Theread/writebitdeterminesthe

directionofthedatatransfer.Forawritedatatransfer,theread/writebitisa0.Afterreceivingthecorrect

I

2

Cdeviceaddressandtheread/writebit,theTAS5518Cdevicerespondswithanacknowledgebit.Next,

themastertransmitstheaddressbyteorbytescorrespondingtotheTAS5518Cinternalmemoryaddress

beingaccessed.Afterreceivingtheaddressbyte,theTAS5518Cagainrespondswithanacknowledgebit.

Next,themasterdevicetransmitsthedatabytetobewrittentothememoryaddressbeingaccessed.After

receivingthedatabyte,theTAS5518Cagainrespondswithanacknowledgebit.Finally,themaster

devicetransmitsastopconditiontocompletethesingle-byte,data-writetransfer.

Figure5-2.Single-ByteWriteTransfer

64SubmitDocumentationFeedback

I

2

CSerial-ControlInterface(SlaveAddresses0x36and0x37)

Not Recommended For New Designs