MPC5200B Data Sheet, Rev. 1

Electrical and Thermal Characteristics

Freescale Semiconductor30

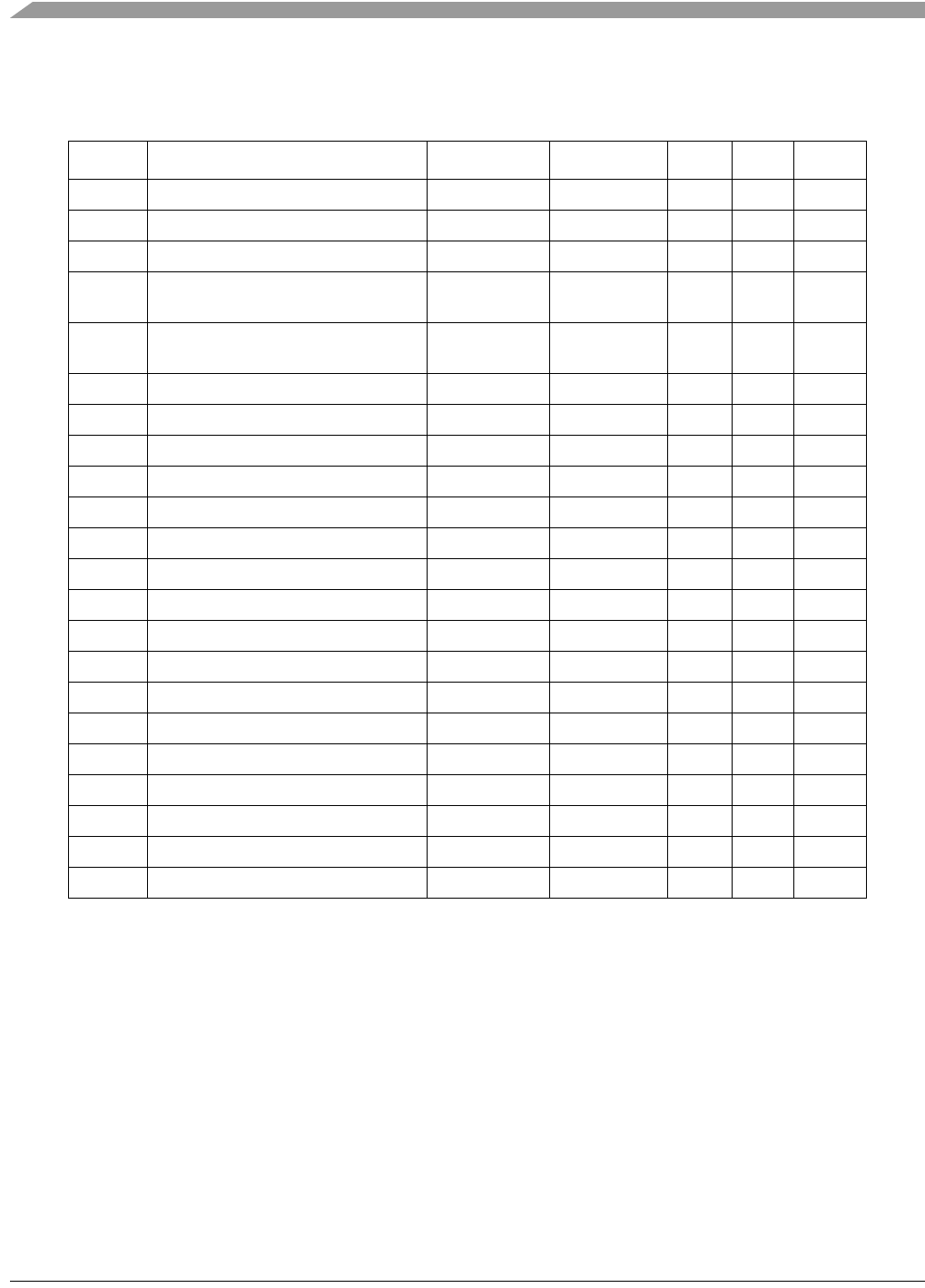

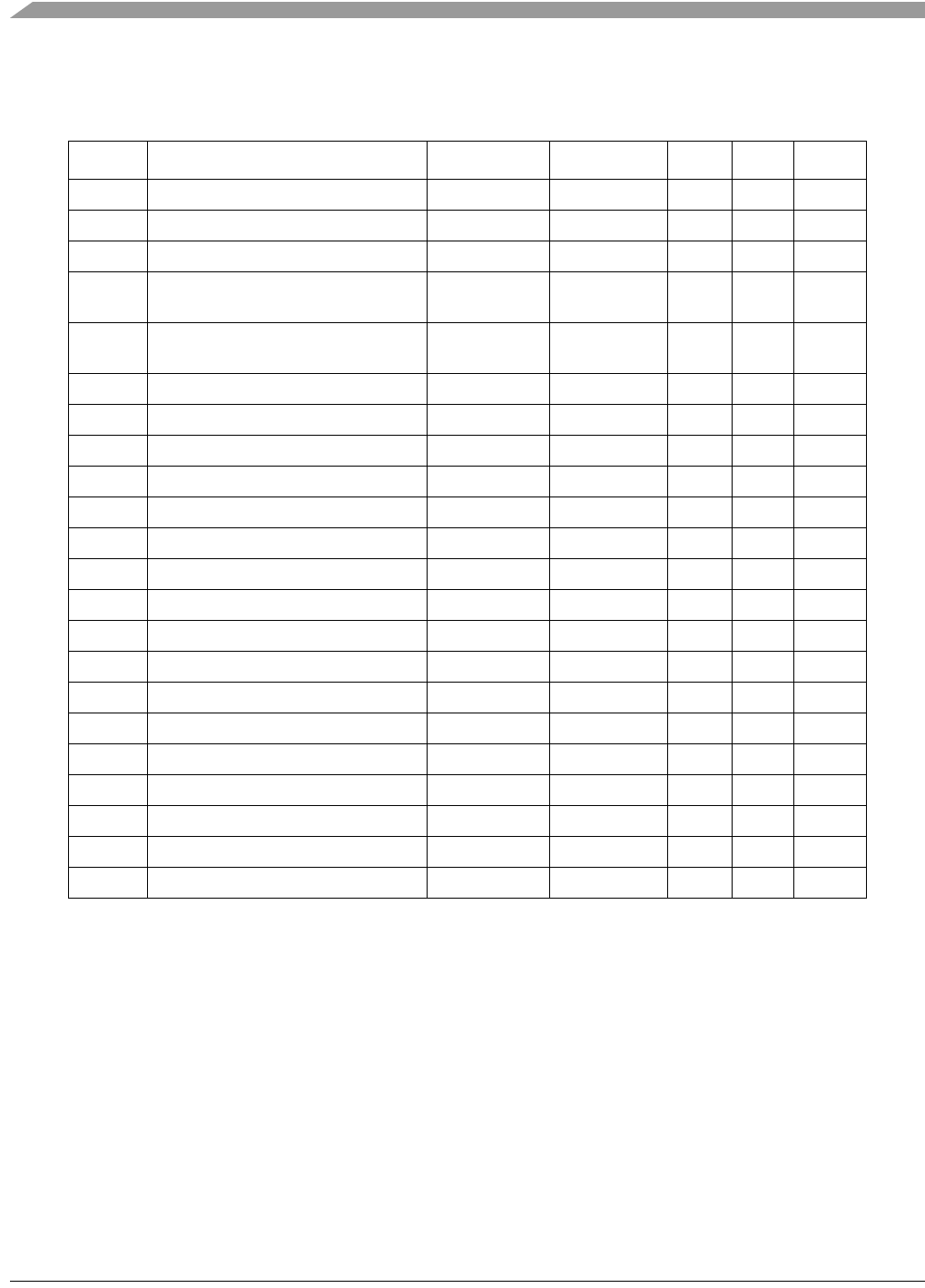

3.3.7.3 MUXed Mode

NOTES:S

1. ACK can shorten the CS pulse width.

Wait States (WS) can be programmed in the Chip Select X Register, Bit field WaitP and WaitX. It can be specified from 0 -

65535.

2. ACK is input and can be used to shorten the CS pulse width.

3. Deadcycles are only used, if no arbitration to an other module (ATA or PCI) of the shared local bus happens. If arbitration

happens the bus can be driven within 4 IPB clocks by an other modules.

Table 26. MUXed Mode Timing

Sym Description Min Max Units Notes SpecID

t

CSA

PCI CLK to CS assertion 4.6 10.6 ns A7.39

t

CSN

PCI CLK to CS negation 2.9 7.0 ns A7.40

t

ALEA

PCI CLK to ALE assertion - 3.6 ns A7.41

t

1

ALE assertion before Address, Bank,

TSIZ assertion

- 5.7 ns A7.42

t

2

CS assertion before Address, Bank,

TSIZ negation

- -1.2 ns A7.43

t

3

CS assertion before Data wr valid - -1.2 ns A7.44

t

4

Data wr hold after CS negation t

IPBIck

- ns A7.45

t

5

Data rd setup before CS negation 8.5 - ns A7.46

t

6

Data rd hold after CS negation 0 (DC+1)*t

PCIck

ns

(1),(3)

A7.47

t

7

ALE pulse width - t

PCIck

ns A7.48

t

TSA

CS assertion after TS assertion - 6.9 ns A7.49

t

8

TS pulse width - t

PCIck

ns A7.50

t

9

CS pulse width (2+WS)*t

PCIck

(2+WS)*t

PCIck

ns A7.51

t

OEA

OE assertion before CS assertion - 4.7 ns A7.52

t

OEN

OE negation before CS negation - 5.9 ns A7.53

t

10

RW assertion before ALE assertion t

IPBIck

- ns A7.54

t

11

RW negation after CS negation - t

PCIck

ns A7.55

t

12

ACK assertion after CS assertion t

IPBIck

-ns

(2)

A7.56

t

13

ACK negation after CS negation - t

PCIck

ns

(2)

A7.57

t

14

ALE negation to CS assertion - t

PCIck

ns A7.58

t

15

ACK change before PCI clock - 2.0 ns

(2)

A7.59

t

16

ACK change after PCI clock - 4.4 ns

(2)

A7.60