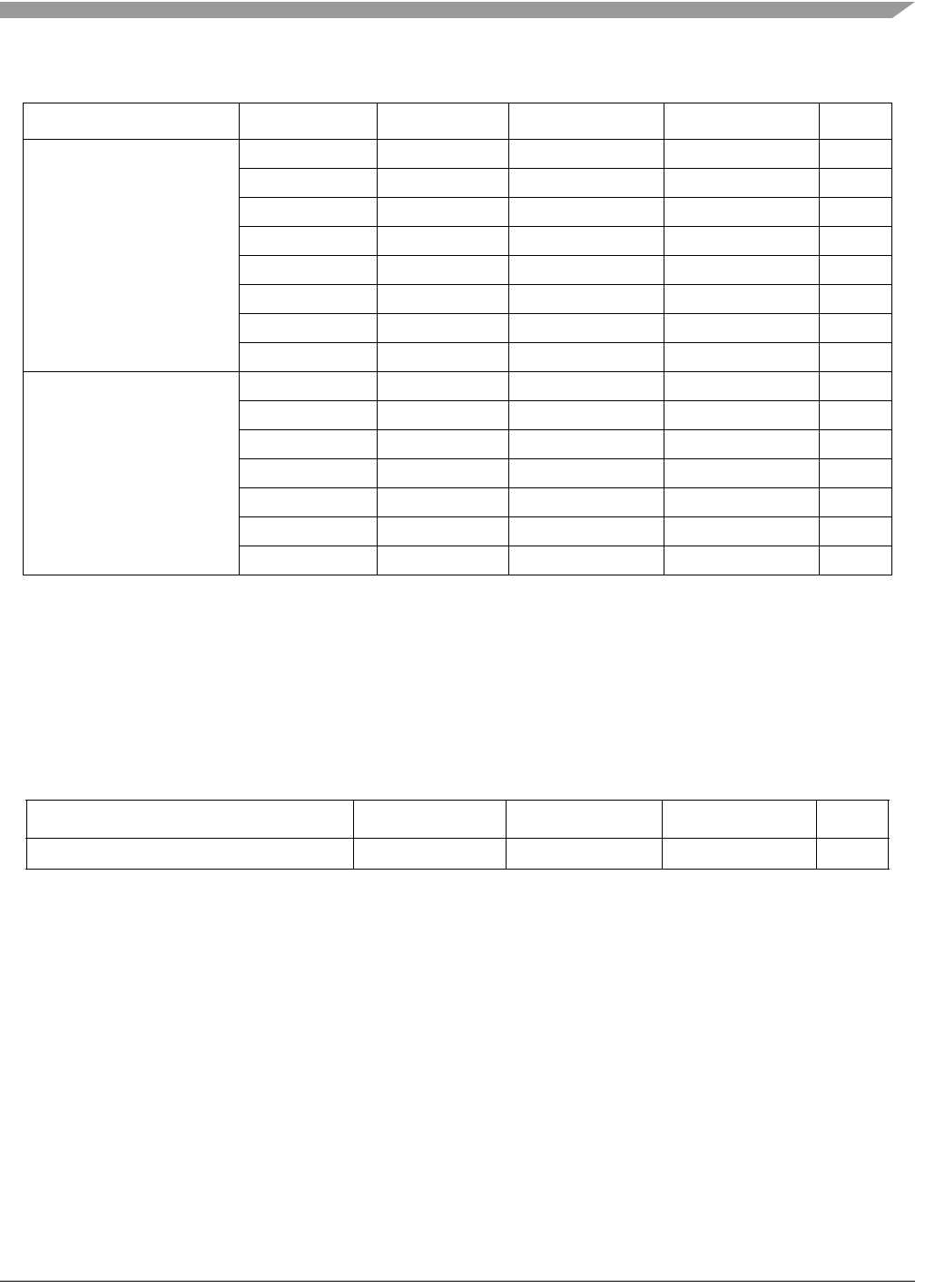

Electrical and Thermal Characteristics

MPC5200B Data Sheet, Rev. 1

Freescale Semiconductor 19

NOTES:

1) The frequency of IP_CLK depends on register settings in Clock Distribution Module. See the MPC5200B User Manual [1].

2) The interrupt latency descriptions in the table above are related to non competitive, non masked but enabled external

interrupt sources. Take care of interrupt prioritization which may increase the latencies.

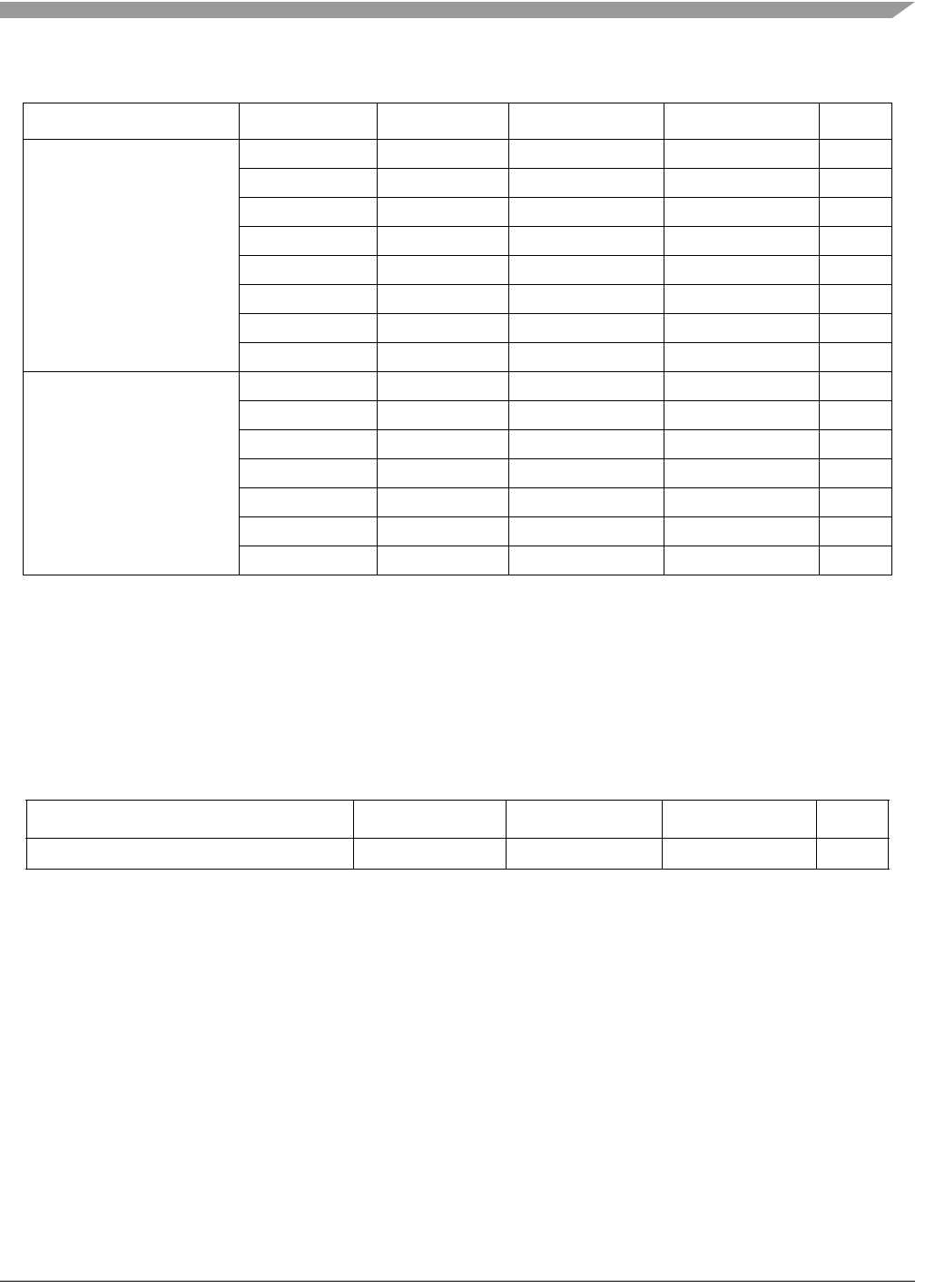

Since all external interrupt signals are synchronized into the internal processor bus clock domain, each of

these signals has to exceed a minimum pulse width of more than one IP_CLK cycle.

NOTES:

1) The frequency of the IP_CLK depends on the register settings in Clock Distribution Module. See the MPC5200B User

Manual [1] for further information.

2) If the same interrupt occurs a second time while its interrupt service routine has not cleared the former one, the second

interrupt will not be recognized at all.

Besides synchronization, prioritization, and mapping the latency of an external interrupt to the start of its

associated interrupt service routine also depends on the following conditions: To get a minimum interrupt

service response time, it is recommended to enable the instruction cache and set up the maximum core

clock, XL bus, and IP bus frequencies (depending on board design and programming). In addition, it is

advisable to execute an interrupt handler, which has been implemented in assembly code.

Standard GPIO Interrupts GPIO_PSC3_4 12 IP_CLK normal (int) A4.6

GPIO_PSC3_5 12 IP_CLK normal (int) A4.7

GPIO_PSC3_8 12 IP_CLK normal (int) A4.8

GPIO_USB_9 12 IP_CLK normal (int) A4.9

GPIO_ETHI_4 12 IP_CLK normal (int) A4.10

GPIO_ETHI_5 12 IP_CLK normal (int) A4.11

GPIO_ETHI_6 12 IP_CLK normal (int) A4.12

GPIO_

ETHI_7

12 IP_CLK normal (int) A4.13

GPIO WakeUp Interrupts GPIO_

PSC1_4

12 IP_CLK normal (int) A4.15

GPIO_PSC2_4 12 IP_CLK normal (int) A4.16

GPIO_PSC3_9 12 IP_CLK normal (int) A4.17

GPIO_ETHI_8 12 IP_CLK normal (int) A4.18

GPIO_IRDA_0 12 IP_CLK normal (int) A4.19

DGP_IN0 12 IP_CLK normal (int) A4.20

DGP_IN1 12 IP_CLK normal (int) A4.21

Table 17. Minimum Pulse Width for External Interrupts to be Recognized

Name Min Pulse Width Max Pulse Width Reference Clock SpecID

All external interrupts (IRQs, GPIOs) > 1 clock cycle — IP_CLK A4.22

Table 16. External Interrupt Latencies (continued)

Interrupt Type Pin Name Clock Cycles Reference Clock Core Interrupt SpecID