MPC5200B Data Sheet, Rev. 1

Electrical and Thermal Characteristics

Freescale Semiconductor54

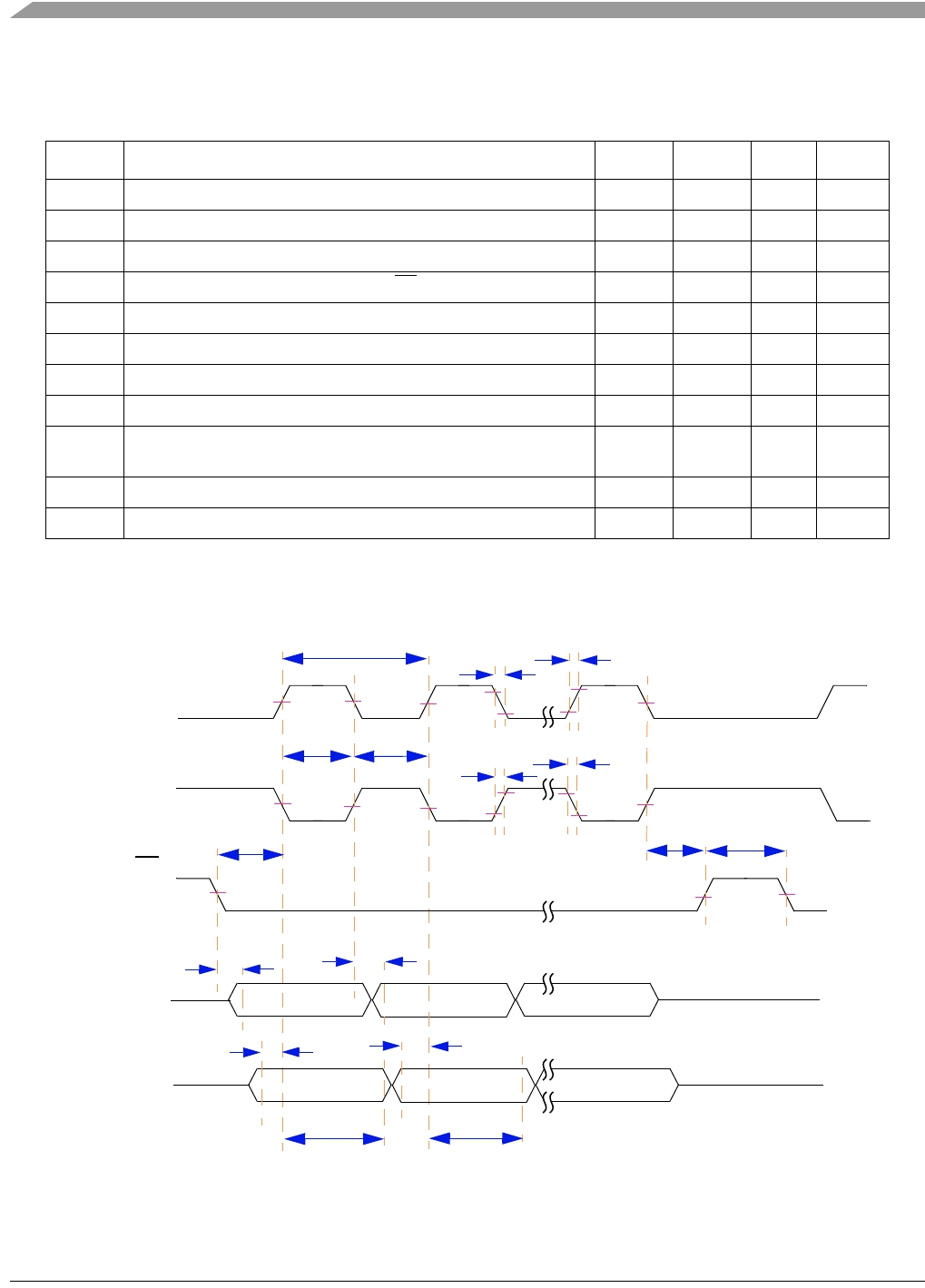

3.3.15.4 SPI Mode

NOTE

Output timing is specified at a nominal 50 pF load.

Figure 41. Timing Diagram — SPI Master Mode, Format 0 (CPHA = 0)

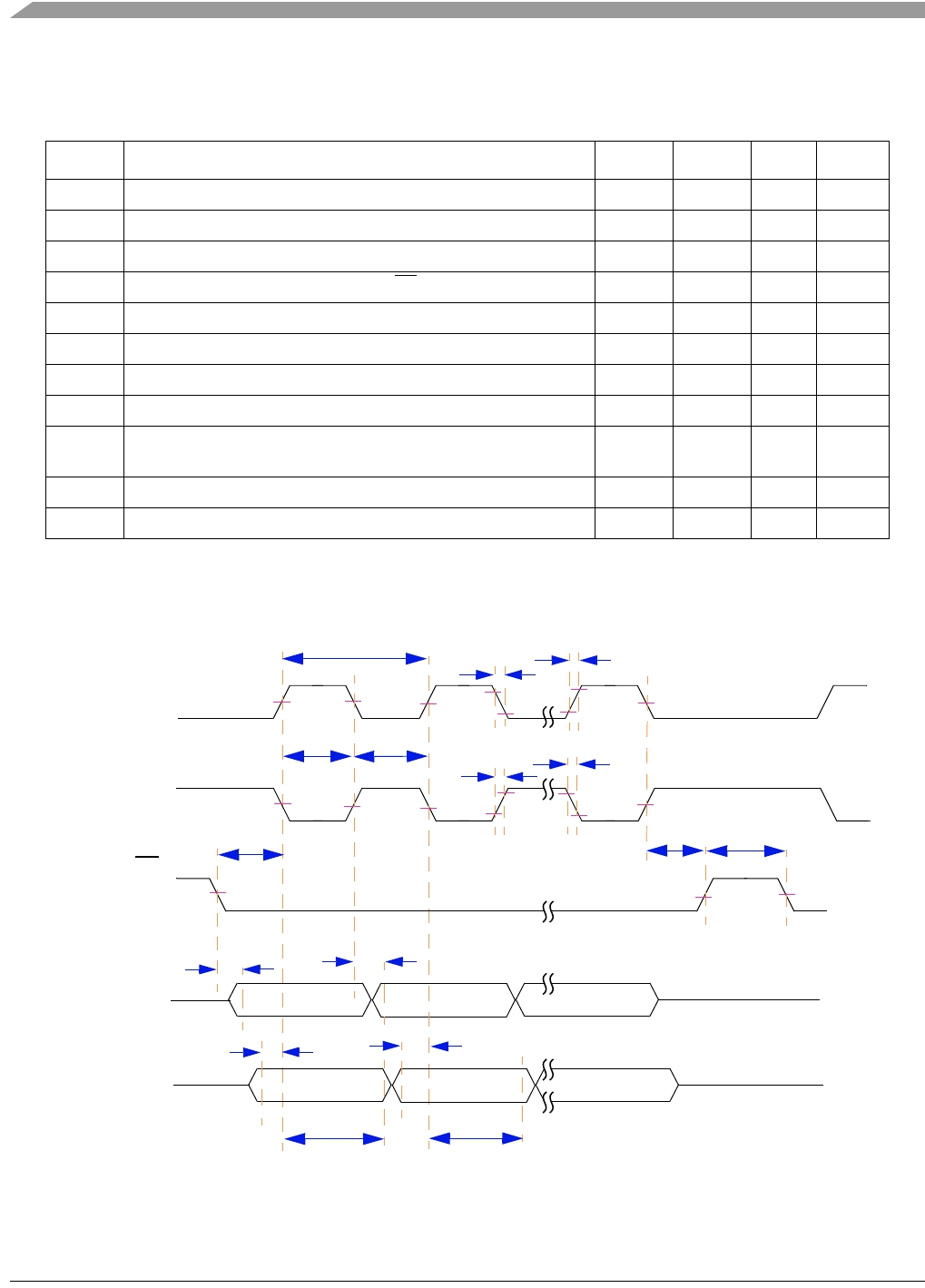

Table 46. Timing Specifications — SPI Master Mode, Format 0 (CPHA = 0)

Sym Description Min Max Units SpecID

1 SCK cycle time, programable in the PSC CCS register 30.0 — ns A15.26

2 SCK pulse width, 50% SCK duty cycle 15.0 — ns A15.27

3 Slave select clock delay, programable in the PSC CCS register 30.0 — ns A15.28

4 Output Data valid after Slave Select (SS) — 8.9 ns A15.29

5 Output Data valid after SCK — 8.9 ns A15.30

6 Input Data setup time 6.0 — ns A15.31

7 Input Data hold time 1.0 — ns A15.32

8 Slave disable lag time — 8.9 ns A15.33

9 Sequential Transfer delay, programable in the PSC CTUR / CTLR

register

15.0 — ns A15.34

10 Clock falling time — 7.9 ns A15.35

11 Clock rising time — 7.9 ns A15.36

SCK

(CLKPOL=0)

SCK

(CLKPOL=1)

MOSI

Output

Output

Output

SS

Output

MISO

Input

1

22

8

9

3

4

5

6

6

7

7

11

10

10

11