MPC5200B Data Sheet, Rev. 1

Electrical and Thermal Characteristics

Freescale Semiconductor48

NOTE

Output timing is specified at a nominal 50 pF load.

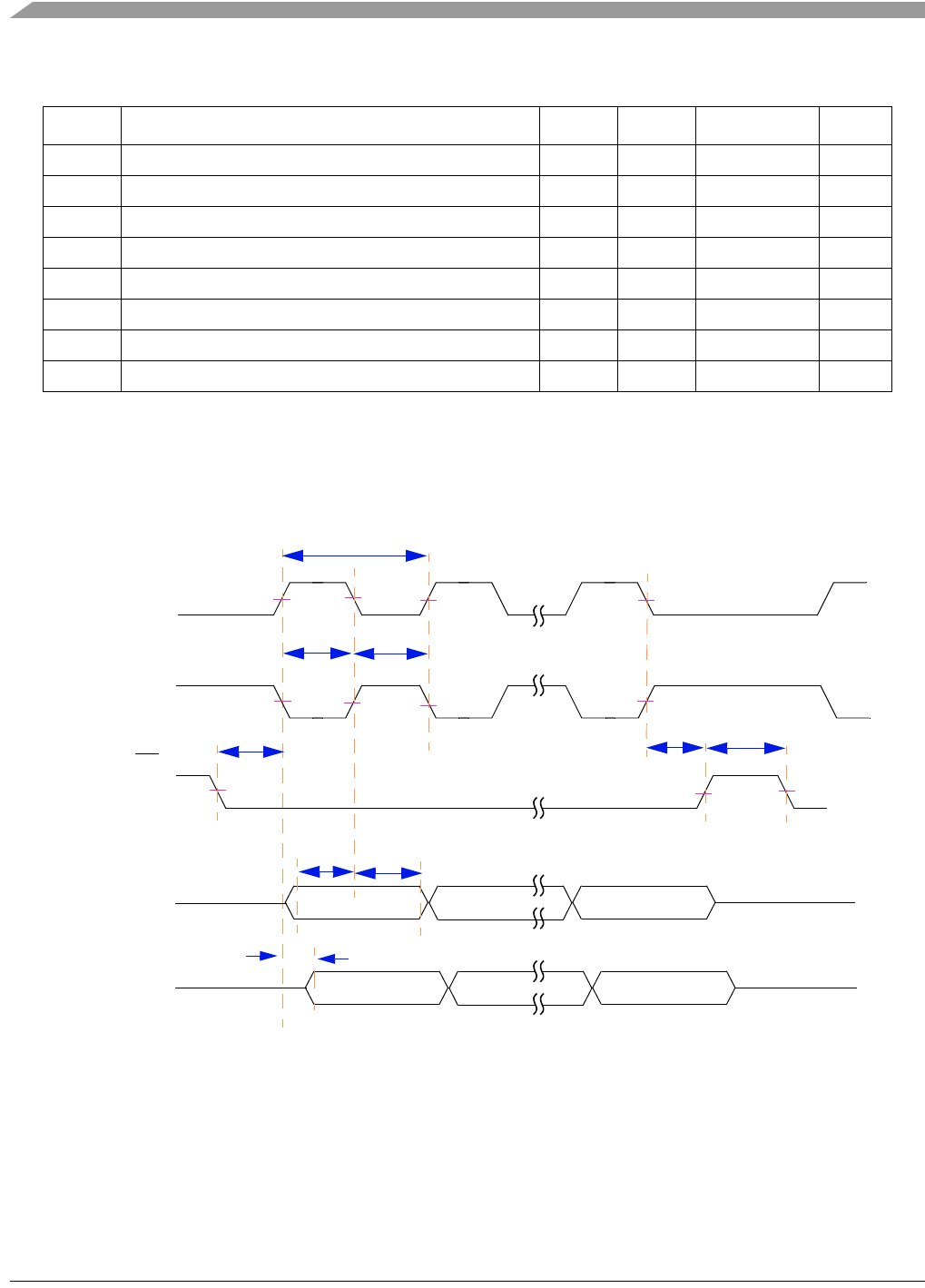

Figure 35. Timing Diagram — SPI Slave Mode, Format 1 (CPHA = 1)

3.3.12 MSCAN

The CAN functions are available as RX and TX pins at normal IO pads (I

2

C1+GPTimer or PSC2). There

is no filter for the WakeUp dominant pulse. Any High-to-Low edge can cause WakeUp, if configured.

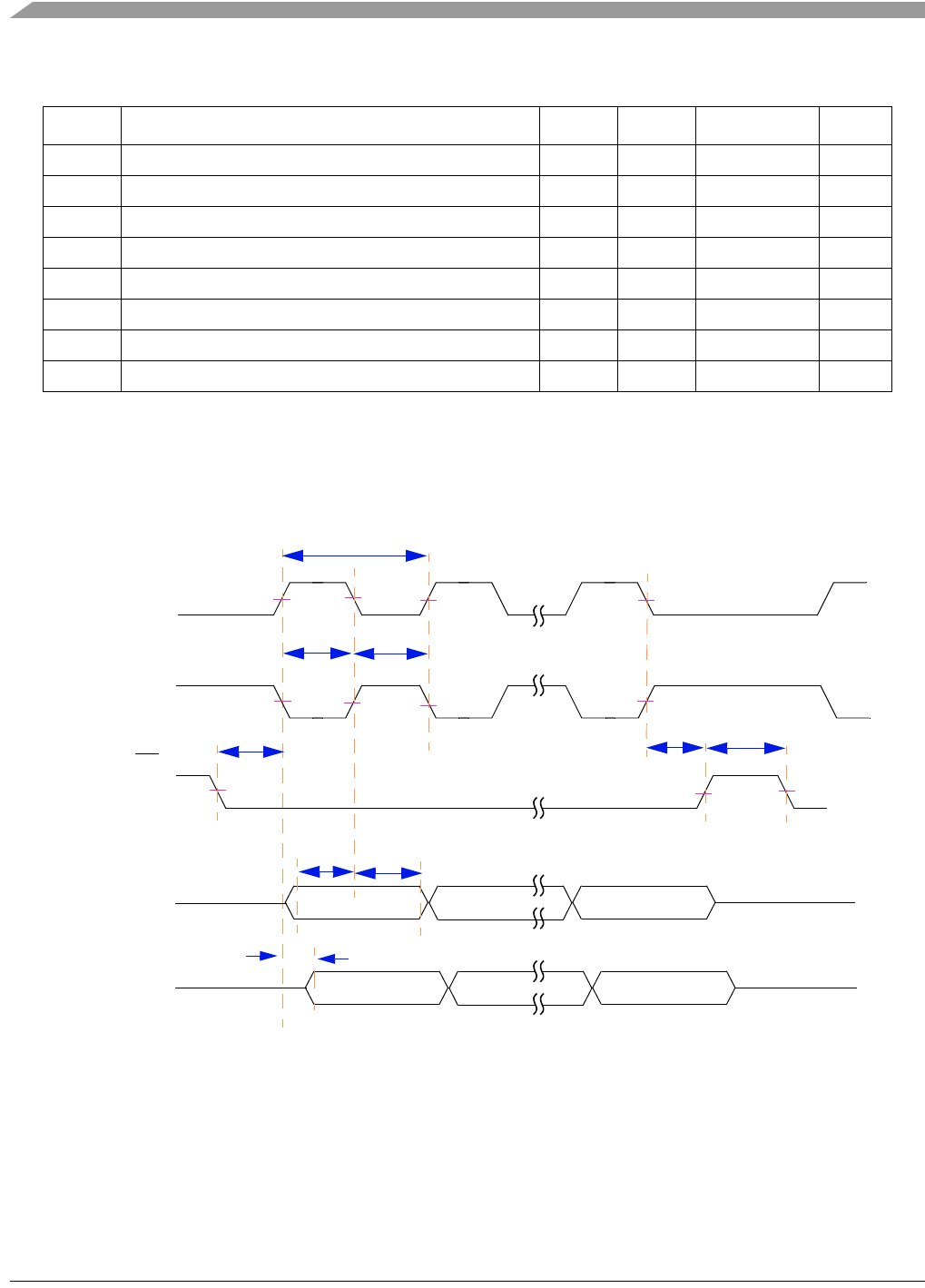

Table 39. Timing Specifications — SPI Slave Mode, Format 1 (CPHA = 1)

Sym Description Min Max Units SpecID

1 Cycle time 4 1024 IP-Bus Cycle

(1)

NOTES:

1

Inter Peripheral Clock is defined in the MPC5200B User Manual [1].

A11.31

2 Clock high or low time 2 512 IP-Bus Cycle

(1)

A11.32

3 Slave select to clock delay 15.0 — ns A11.33

4 Output data valid — 50.0 ns A11.34

5 Input Data setup time 50.0 — ns A11.35

6 Input Data hold time 0.0 — ns A11.36

7 Slave disable lag time 15.0 — ns A11.37

8 Sequential Transfer delay 1 — IP-Bus Cycle

(1)

A11.38

SCK

(CLKPOL=0)

SCK

(CLKPOL=1)

MOSI

Input

Input

Input

SS

Input

MISO

Output

1

22

7

8

3

4

6

5