MPC5200B Data Sheet, Rev. 1

Electrical and Thermal Characteristics

Freescale Semiconductor42

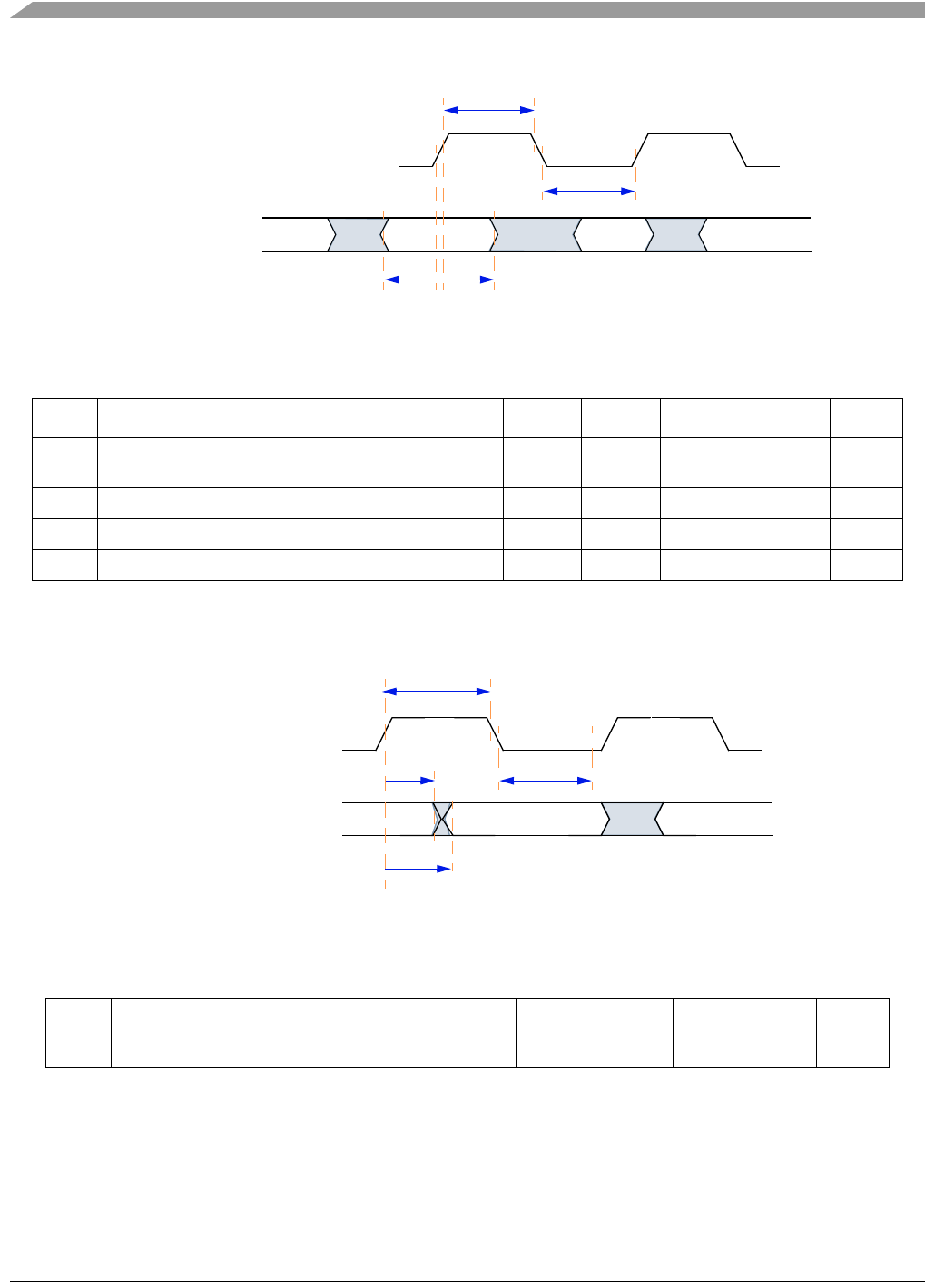

Figure 27. Ethernet Timing Diagram—MII Rx Signal

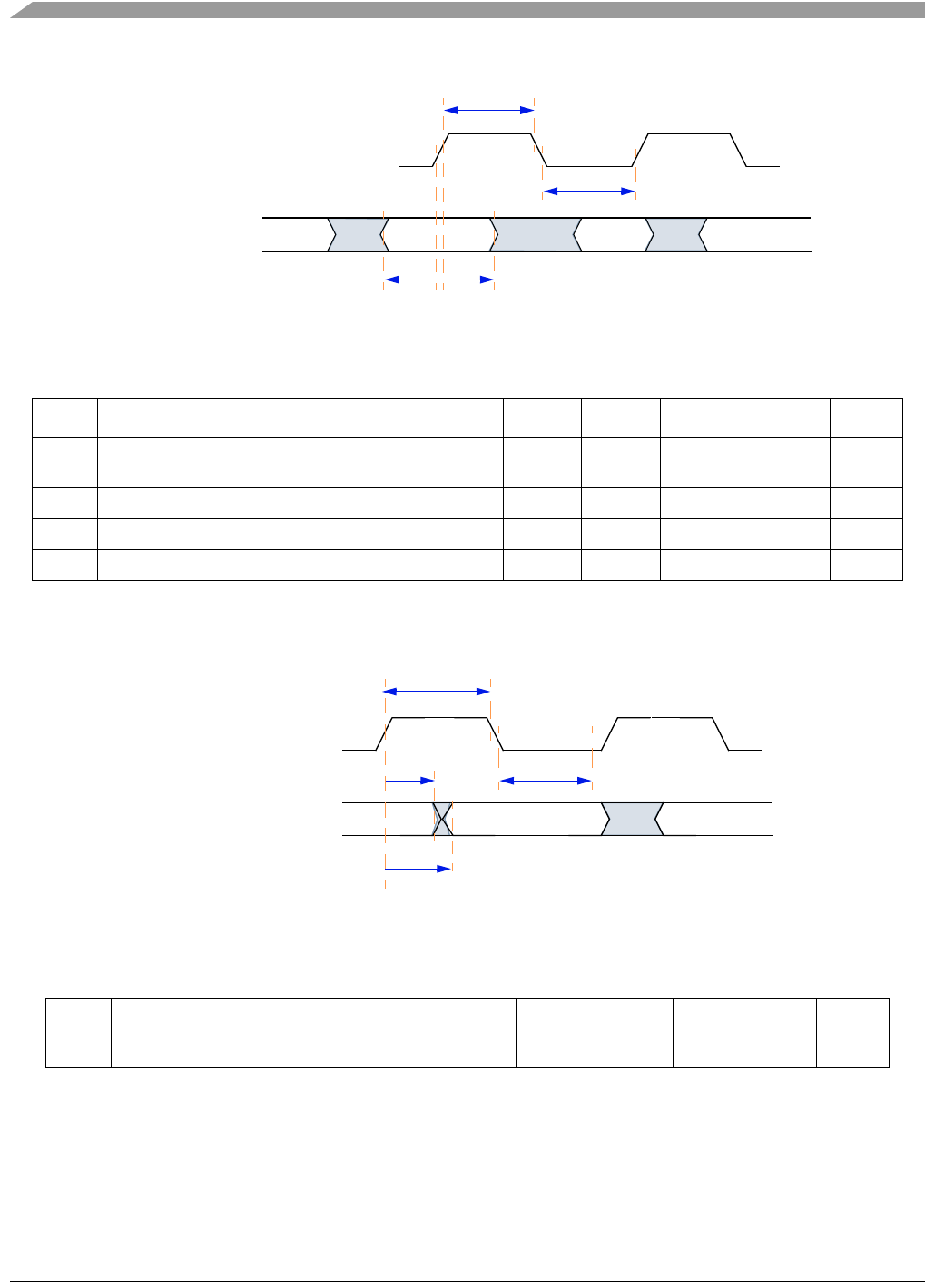

Figure 28. Ethernet Timing Diagram—MII Tx Signal

Table 32. MII Tx Signal Timing

Sym Description Min Max Unit SpecID

t

5

TX_CLK rising edge to TXD[3:0], TX_EN, TX_ER

invalid

5— ns A9.5

t

6

TX_CLK rising edge to TXD[3:0], TX_EN, TX_ER valid — 25 ns A9.6

t

7

TX_CLK pulse width high 35% 65% TX_CLK Period

(1)

NOTES:

1

The TX_CLK frequency shall be 25% of the nominal transmit frequency, e.g., a PHY operating at 100 Mb/s must

provide a TX_CLK frequency of 25 MHz and a PHY operating at 10 Mb/s must provide a TX_CLK frequency of 2.5

MHz. See the IEEE 802.3 Specification [6].

A9.7

t

8

TX_CLK pulse width low 35% 65% TX_CLK Period

(1)

A9.8

Table 33. MII Async Signal Timing

Sym Description Min Max Unit SpecID

t

9

CRS, COL minimum pulse width 1.5 — TX_CLK Period A9.9

t

4

t

3

t

1

t

2

RX_CLK (Input)

RXD[3:0] (inputs)

RX_DV

RX_ER

t

8

t

7

t

5

TX_CLK (Input)

TXD[3:0] (Outputs)

TX_EN

TX_ER

t

6