104 S29GLxxxN MirrorBitTM Flash Family 27631A4 May 13, 2004

Advance Information

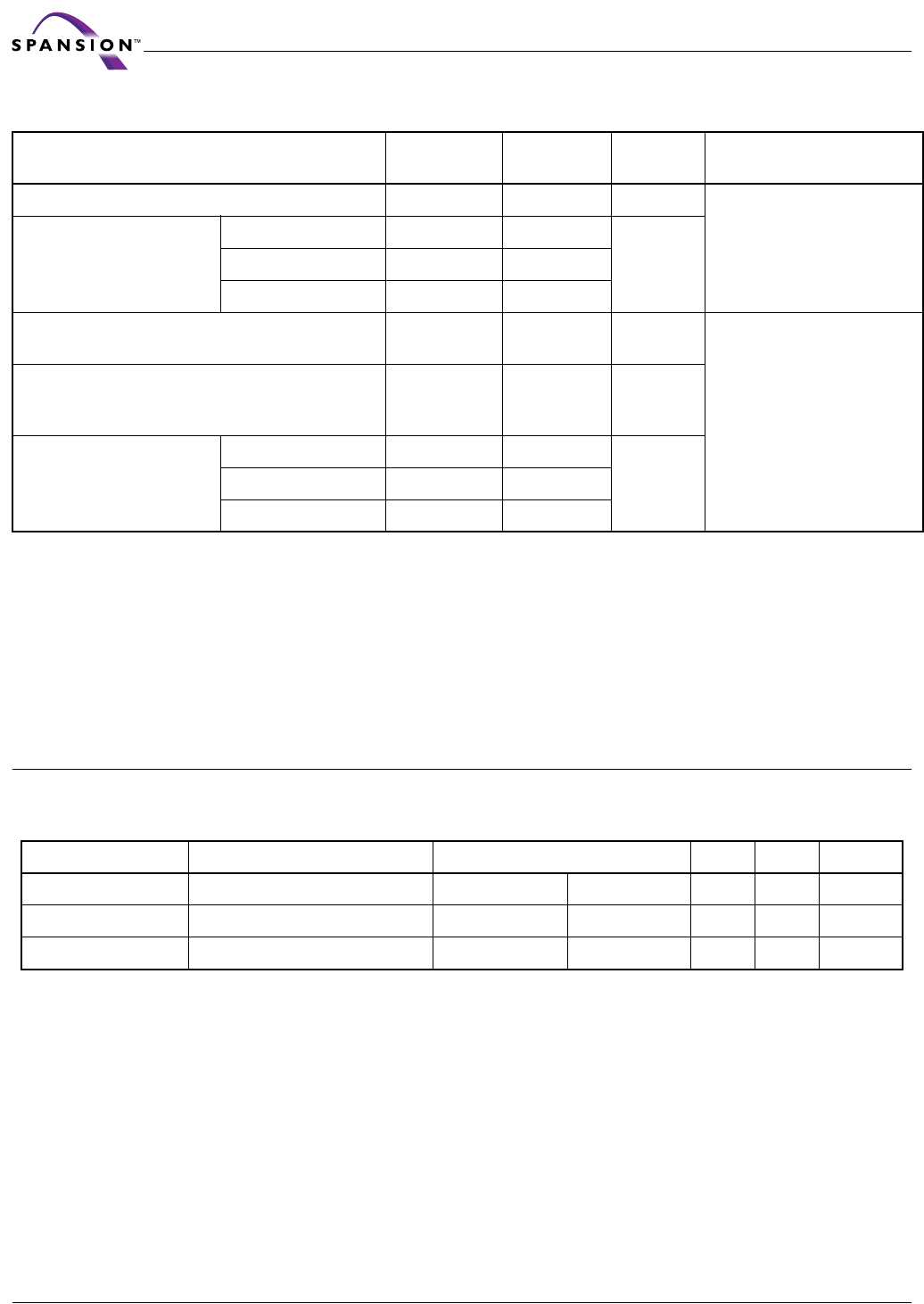

Erase And Programming Performance

Notes:

1. Typical program and erase times assume the following conditions: 25°C, 3.0 V V

CC

, 10,000 cycles, checkerboard

pattern.

2. Under worst case conditions of 90°C, V

CC

= 3.0 V, 1,000,000 cycles.

3. Effective write buffer specification is based upon a 16-word write buffer operation.

4. The typical chip programming time is considerably less than the maximum chip programming time listed, since most

words program faster than the maximum program times listed.

5. In the pre-programming step of the Embedded Erase algorithm, all bits are programmed to 00h before erasure.

6. System-level overhead is the time required to execute the two- or four-bus-cycle sequence for the program

command. See Table 17 for further information on command definitions.

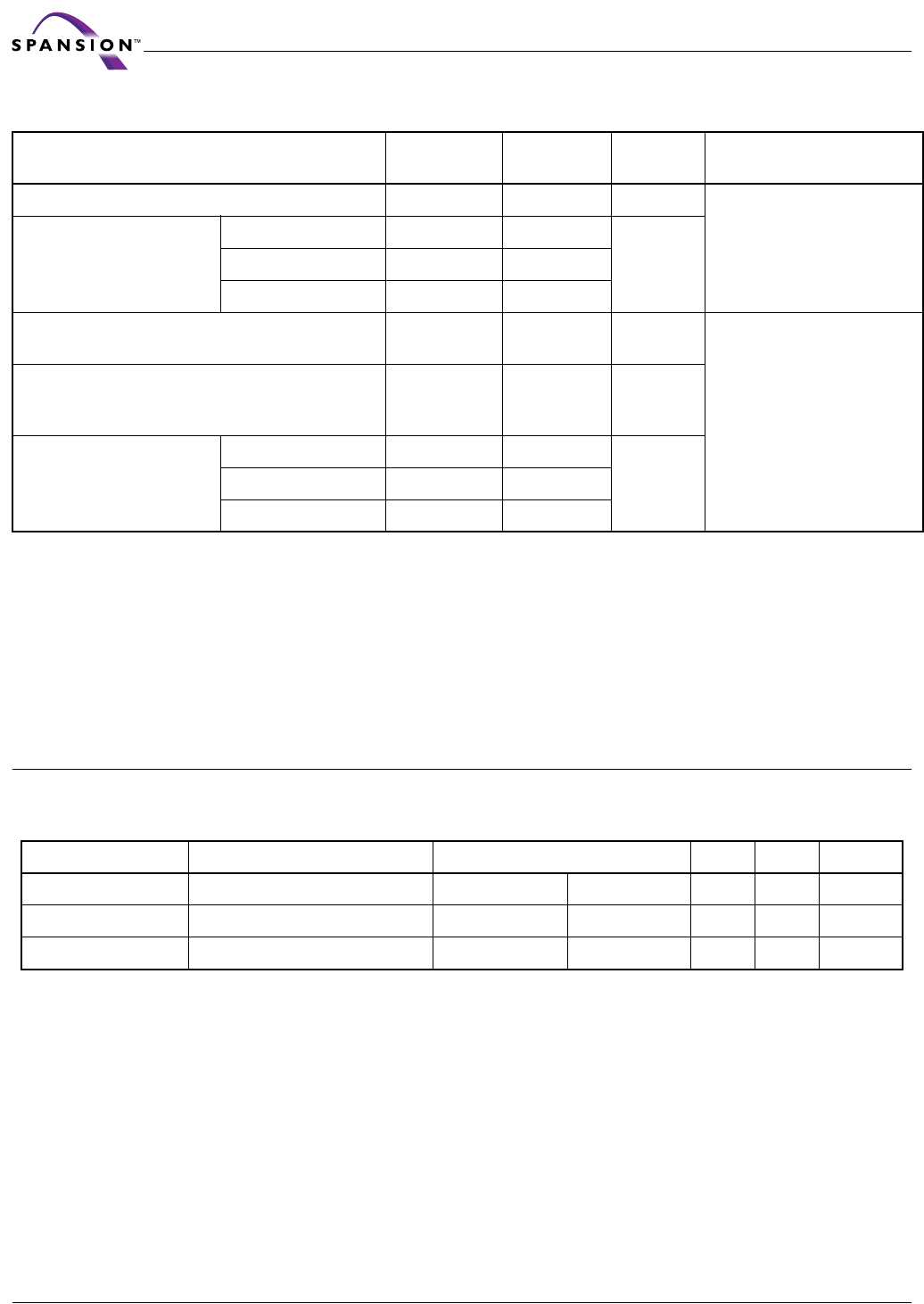

TSOP Pin and BGA Package Capacitance

Notes:

1. Sampled, not 100% tested.

2. Test conditions T

A

= 25°C, f = 1.0 MHz.

Parameter

Typ

(Note 1)

Max

(Note 2) Unit Comments

Sector Erase Time 1 3.5 sec

Excludes 00h programming

prior to erasure (Note 5)

Chip Erase Time

S29GL128N 128 256

secS29GL256N 256 512

S29GL512N 512 1024

Total Write Buffer Time

(Note 3)

240 µs

Excludes system level

overhead (Note 6)

Total Accelerated Effective

Write Buffer Programming

Time (Note 3)

200 µs

Chip Program Time

S29GL128N 123

secS29GL256N 246

S29GL512N 492

Parameter Symbol Parameter Description Test Setup Typ Max Unit

C

IN

Input Capacitance V

IN

= 0 TSOP 6 7.5 pF

C

OUT

Output Capacitance V

OUT

= 0 TSOP 8.5 12 pF

C

IN2

Control Pin Capacitance V

IN

= 0 TSOP 7.5 9 pF