May 13, 2004 27631A4 S29GLxxxN MirrorBitTM Flash Family 99

Advance Information

AC Characteristics

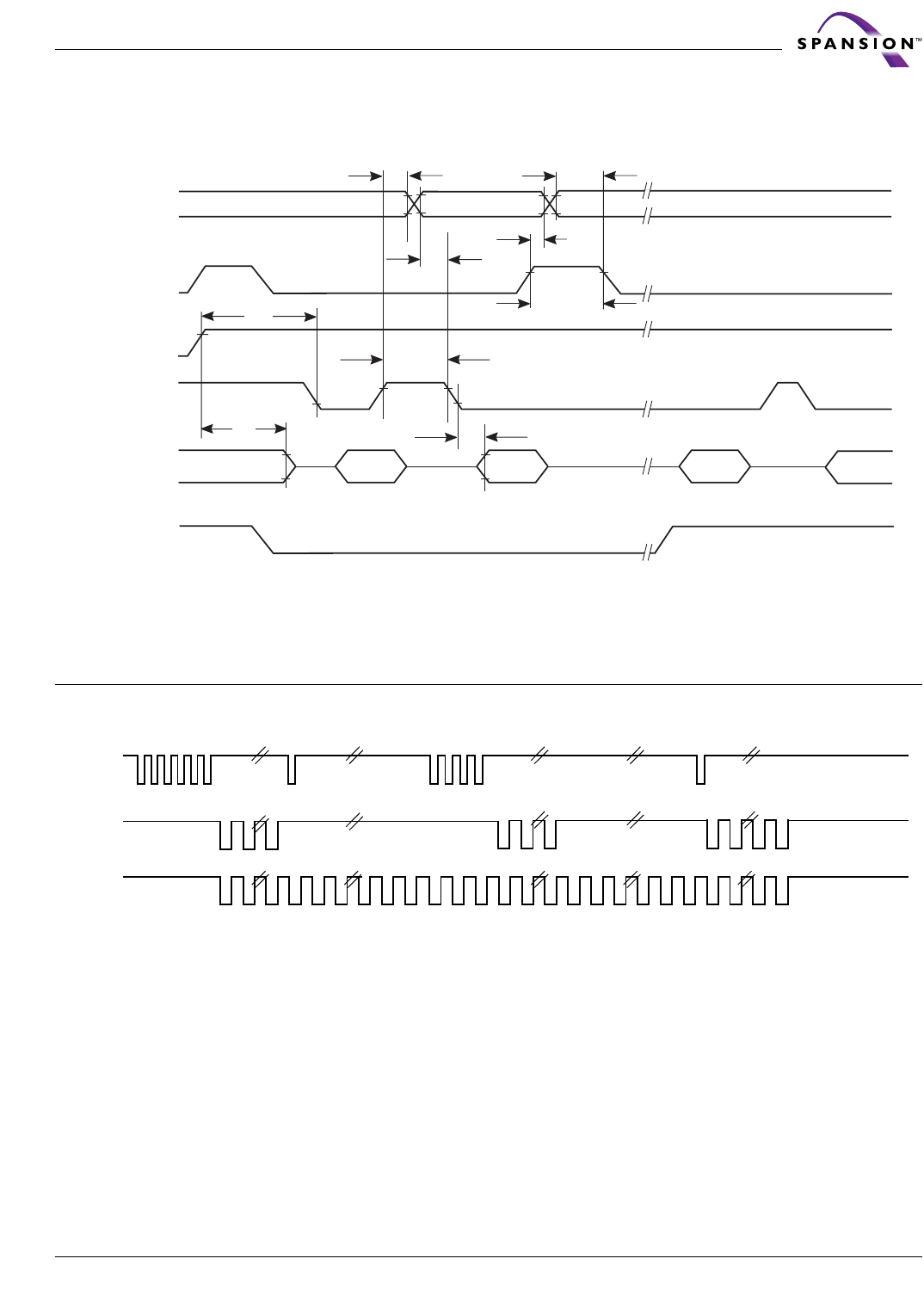

OE#

CE#

WE#

Addresses

t

OEH

t

DH

t

AHT

t

ASO

t

OEPH

t

OE

Valid Data

(first read) (second read) (stops toggling)

t

CEPH

t

AHT

t

AS

DQ2 and DQ6 Valid Data

Valid

Status

Valid

Status

Valid

Status

RY/BY#

Note: VA = Valid address; not required for DQ6. Illustration shows first two status cycle after command

sequence, last status read cycle, and array data read cycle

Figure 18. Toggle Bit Timings (During Embedded Algorithms)

Note: DQ2 toggles only when read at an address within an erase-suspended sector. The system may use OE#

or CE# to toggle DQ2 and DQ6.

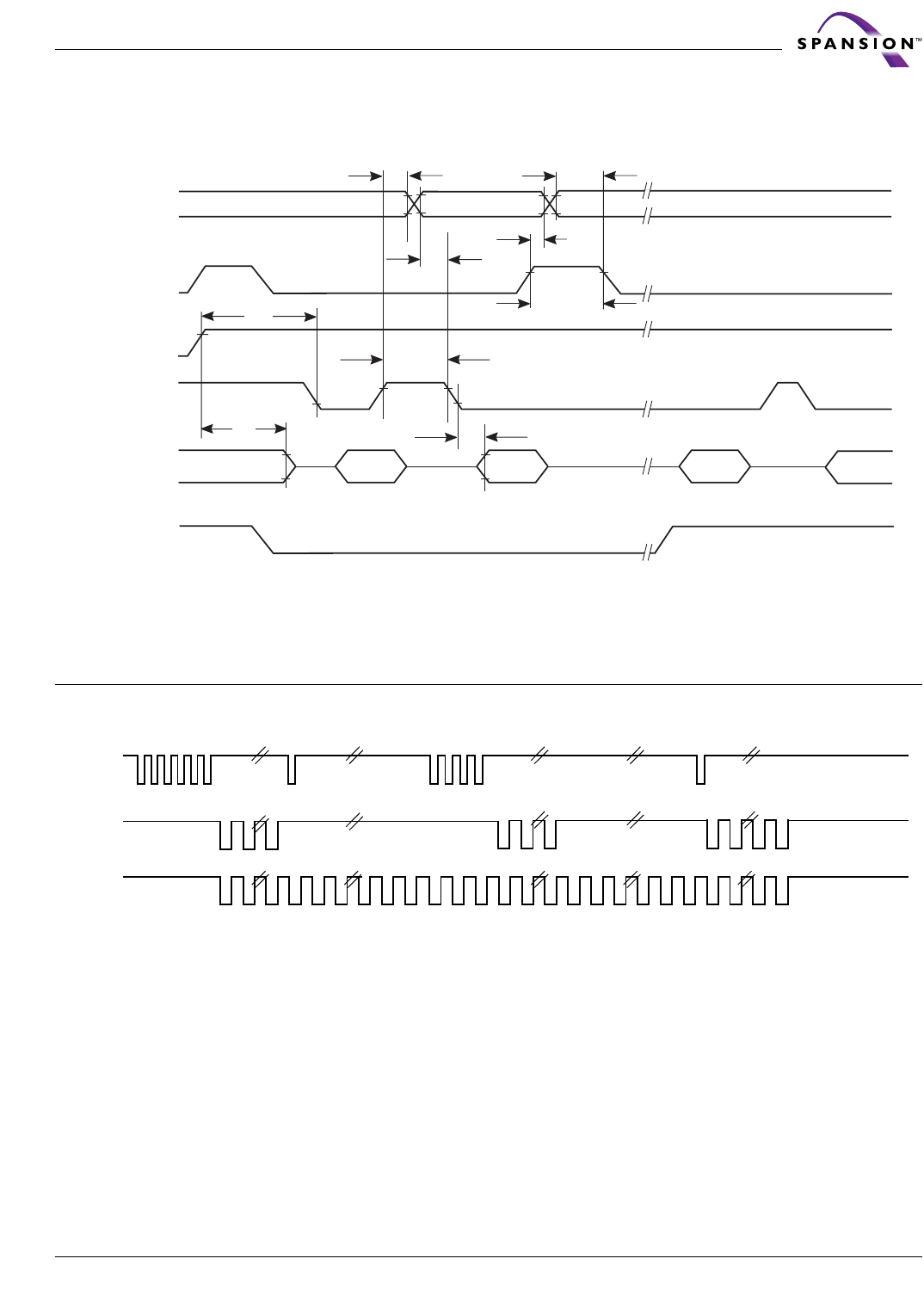

Figure 19. DQ2 vs. DQ6

Enter

Erase

Erase

Erase

Enter Erase

Suspend Program

Erase Suspend

Read

Erase Suspend

Read

Erase

WE#

DQ6

DQ2

Erase

Complete

Erase

Suspend

Suspend

Program

Resume

Embedded

Erasing