90 S29GLxxxN MirrorBitTM Flash Family 27631A4 May 13, 2004

Advance Information

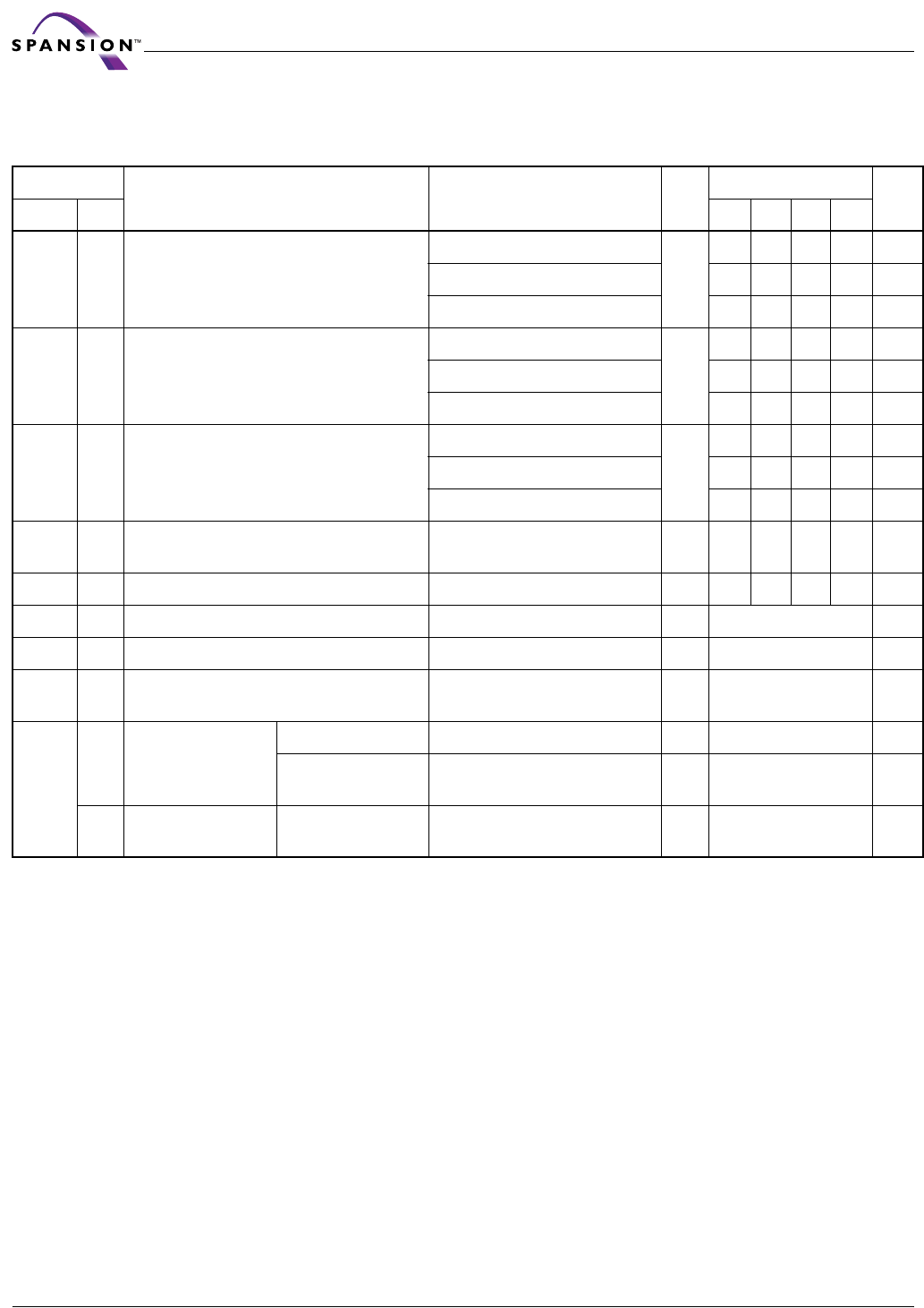

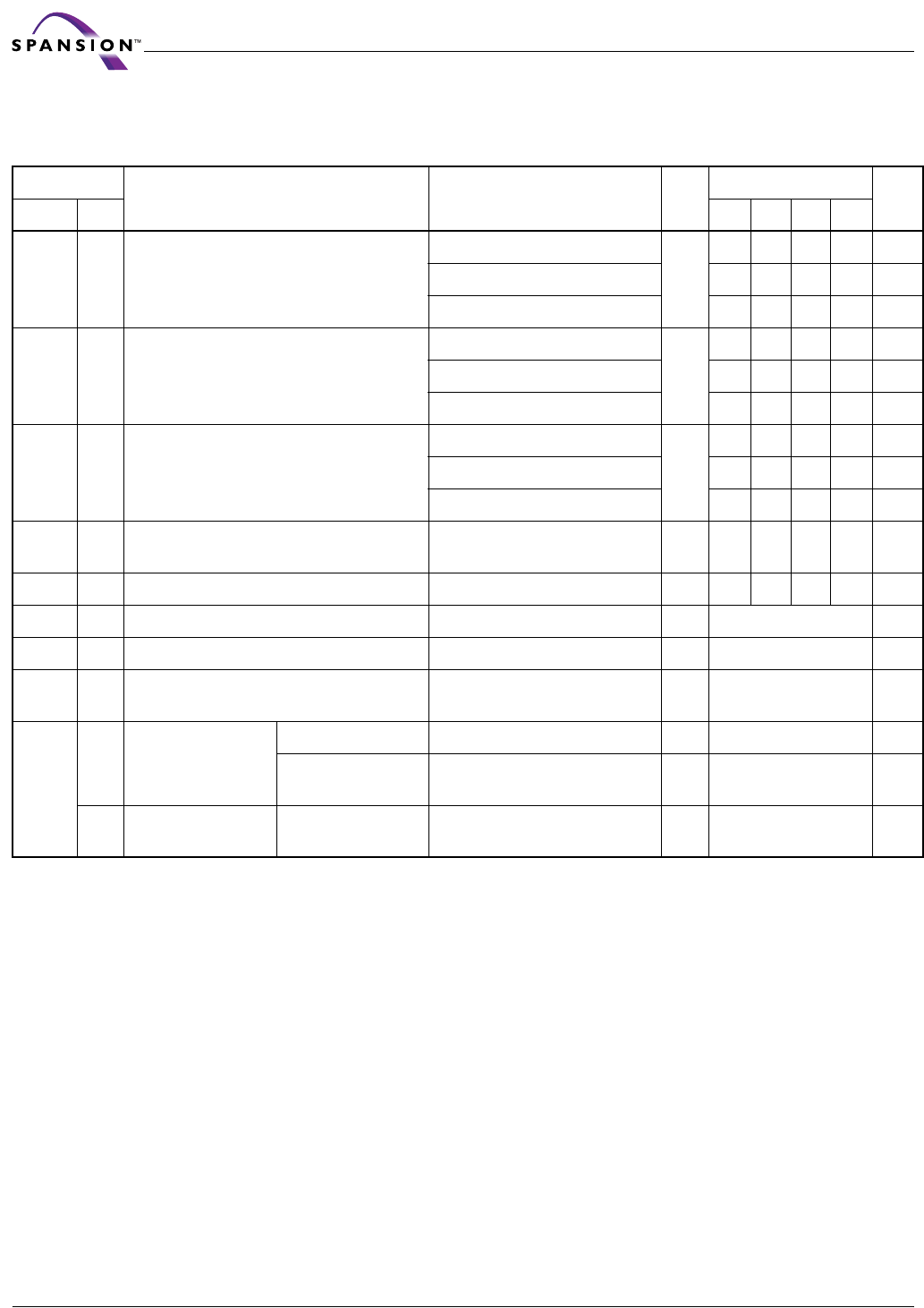

AC Characteristics

Read-Only Operations–S29GL128N Only

Notes:

1. Not 100% tested.

2. CE#, OE# = V

IL

3. OE# = V

IL

4. See Figure 9 and Table 15 for test specifications.

5. Unless otherwise indicated, AC specifications for 80 ns and 90 ns speed options are tested with V

IO

= V

CC

= 3 V. AC

specifications for 90 ns and 100 ns speed options are tested with V

IO

= 1.8 V and V

CC

= 3.0 V.

Parameter

Description

Test Setup

Speed Options

JEDEC Std. 80 90 90 100 Unit

t

AVAV

t

RC

Read Cycle Time

V

IO

= V

CC

= 3 V

Min

80 90 ns

V

IO

= 2.5 V, V

CC

= 3 V (Note 1) 90 100

V

IO

= 1.8 V, V

CC

= 3 V 90 100 ns

t

AVQV

t

ACC

Address to Output Delay (Note 2)

V

IO

= V

CC

= 3 V

Max

80 90 ns

V

IO

= 2.5 V, V

CC

= 3 V (Note 1) 90 100

V

IO

= 1.8 V, V

CC

= 3 V 90 100 ns

t

ELQV

t

CE

Chip Enable to Output Delay (Note 3)

V

IO

= V

CC

= 3 V

Max

80 90 ns

V

IO

= 2.5 V, V

CC

= 3 V (Note 1) 90 100

V

IO

= 1.8 V, V

CC

= 3 V 90 100 ns

t

PAC

C

Page Access Time Max 25 25 35 35 ns

t

GLQV

t

OE

Output Enable to Output Delay Max 25 25 35 35 ns

t

EHQZ

t

DF

Chip Enable to Output High Z (Note 1) Max 20 ns

t

GHQZ

t

DF

Output Enable to Output High Z (Note 1) Max 20 ns

t

AXQX

t

OH

Output Hold Time From Addresses, CE#

or OE#, Whichever Occurs First

Min 0 ns

t

OEH

Output Enable Hold

Time (Note 1)

Read Min 0 ns

Toggle and

Data# Polling

Min 10 ns

tCEH

Chip Enable Hold

Time

Read Min 35 ns