52 S29GLxxxN MirrorBitTM Flash Family 27631A4 May 13, 2004

Advance Information

that the ACC function and unlock bypass modes are not available when the SecSi

Sector is enabled.

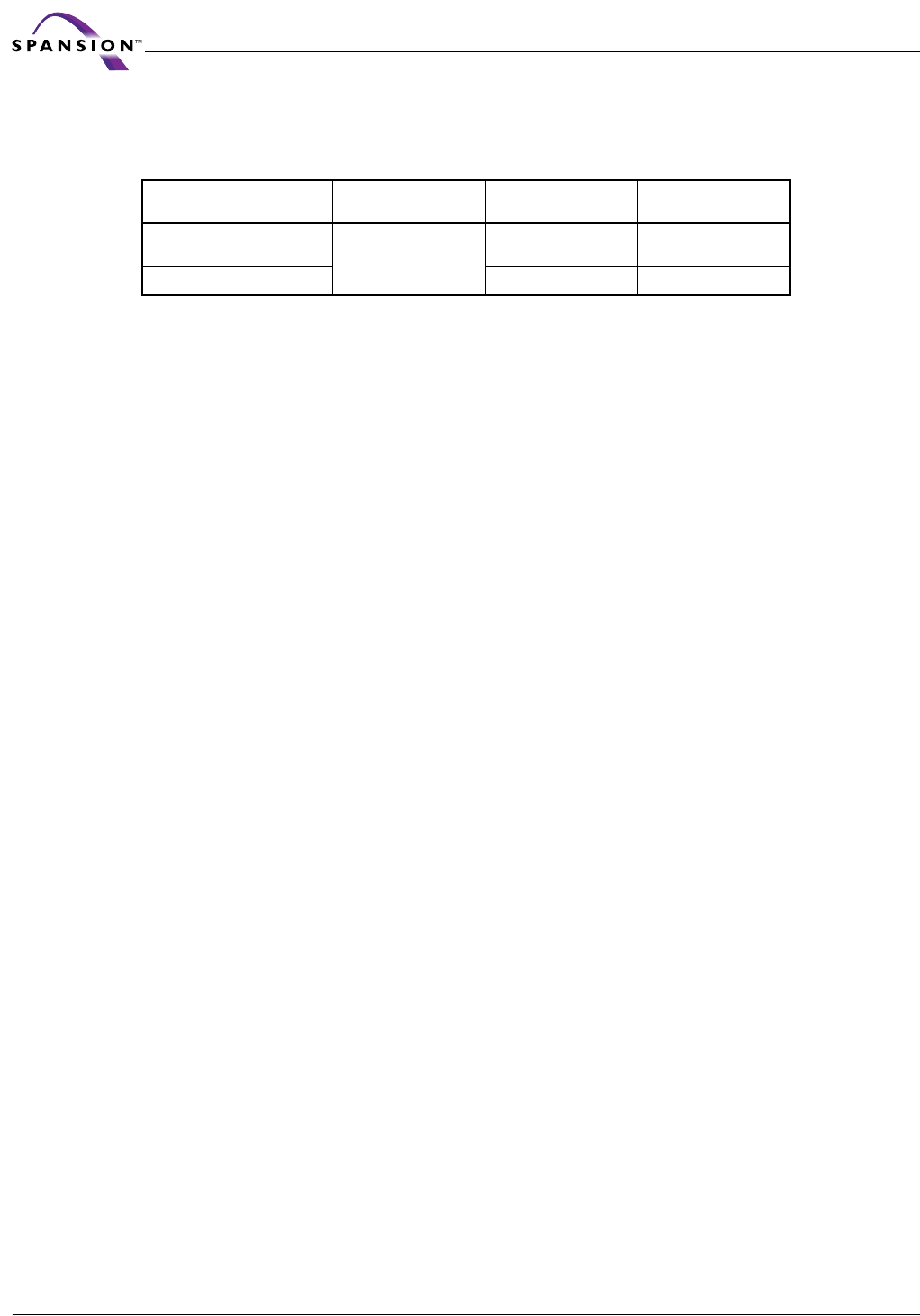

The SecSi sector address space in this device is allocated as follows:

The system accesses the SecSi Sector through a command sequence (see “Write

Protect (WP#)”). After the system has written the Enter SecSi Sector command

sequence, it may read the SecSi Sector by using the addresses normally occupied

by the first sector (SA0). This mode of operation continues until the system issues

the Exit SecSi Sector command sequence, or until power is removed from the de-

vice. On power-up, or following a hardware reset, the device reverts to sending

commands to sector SA0.

Customer Lockable: SecSi Sector NOT Programmed or Protected

At the Factory

Unless otherwise specified, the device is shipped such that the customer may

program and protect the 256-byte SecSi sector.

The system may program the SecSi Sector using the write-buffer, accelerated

and/or unlock bypass methods, in addition to the standard programming com-

mand sequence. See Command Definitions.

Programming and protecting the SecSi Sector must be used with caution since,

once protected, there is no procedure available for unprotecting the SecSi Sector

area and none of the bits in the SecSi Sector memory space can be modified in

any way.

The SecSi Sector area can be protected using one of the following procedures:

Write the three-cycle Enter SecSi Sector Region command sequence, and

then follow the in-system sector protect algorithm as shown in Figure 2, ex-

cept that RESET# may be at either V

IH

or V

ID

. This allows in-system protec-

tion of the SecSi Sector without raising any device pin to a high voltage. Note

that this method is only applicable to the SecSi Sector.

To verify the protect/unprotect status of the SecSi Sector, follow the algo-

rithm shown in Figure 1.

Once the SecSi Sector is programmed, locked and verified, the system must write

the Exit SecSi Sector Region command sequence to return to reading and writing

within the remainder of the array.

Factory Locked: SecSi Sector Programmed and Protected At the

Factory

In devices with an ESN, the SecSi Sector is protected when the device is shipped

from the factory. The SecSi Sector cannot be modified in any way. An ESN Factory

Locked device has an 16-byte random ESN at addresses 000000h–000007h.

Please contact your sales representative for details on ordering ESN Factory

Locked devices.

Customers may opt to have their code programmed by the factory through the

ExpressFlash service (Express Flash Factory Locked). The devices are then

shipped from the factory with the SecSi Sector permanently locked. Contact your

sales representative for details on using the ExpressFlash service.

SecSi Sector Address Range Customer Lockable ESN Factory Locked

ExpressFlash

Factory Locked

000000h–000007h

Determined by customer

ESN

ESN or determined by

customer

000008h–00007Fh Unavailable Determined by customer