5−2

signaling are the ExCA interrupt and general control register (ExCA offset 03h/43h/803h, see Section 5.4) and the

ExCA card status-change interrupt configuration register (05h/45h/805h, see Section 5.6).

Access to I/O mapped 16-bit PC cards is available to the host system via two ExCA I/O windows. These are regions

of host I/O address space into which the card I/O space is mapped. These windows are defined by start, end, and

offset addresses programmed in the ExCA registers described in this section. I/O windows have byte granularity.

Access to memory mapped 16-bit PC Cards is available to the host system via five ExCA memory windows. These

are regions of host memory space into which the card memory space is mapped. These windows are defined by start,

end, and offset addresses programmed in the ExCA registers described in this section. Table 5−1 identifies each

ExCA register and its respective ExCA offset. Memory windows have 4-Kbyte granularity.

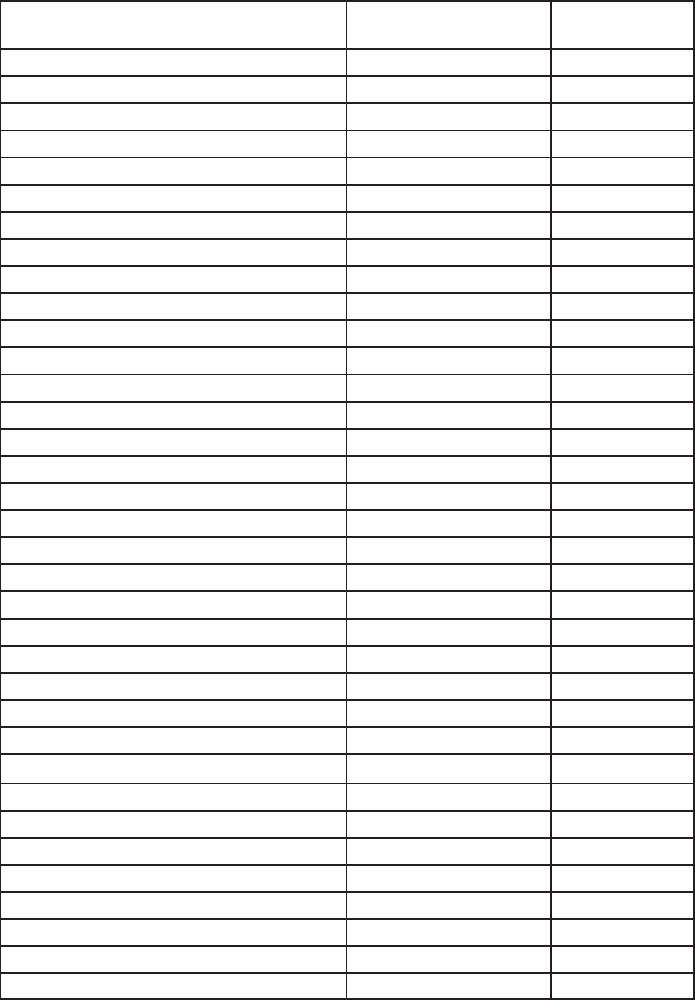

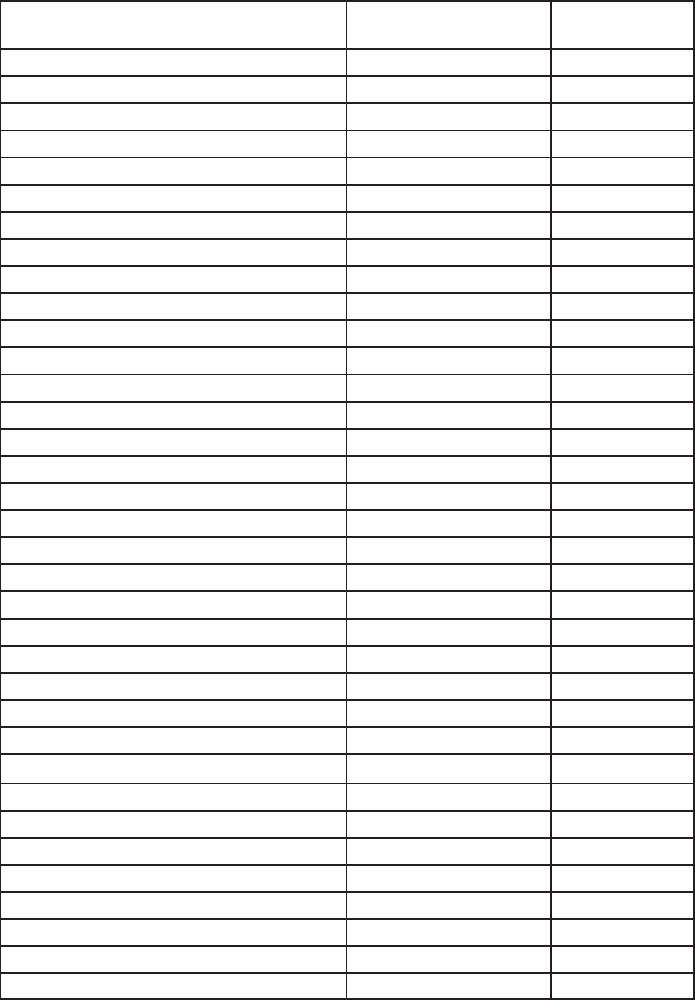

Table 5−1. ExCA Registers and Offsets

EXCA REGISTER NAME

PCI MEMORY ADDRESS

OFFSET (HEX)

ExCA OFFSET

(HEX)

Identification and revision 800 00

Interface status 801 01

Power control 802 02

Interrupt and general control 803 03

Card status change 804 04

Card status-change interrupt configuration 805 05

Address window enable 806 06

I / O window control 807 07

I / O window 0 start-address low byte 808 08

I / O window 0 start-address high byte 809 09

I / O window 0 end-address low byte 80A 0A

I / O window 0 end-address high byte 80B 0B

I / O window 1 start-address low byte 80C 0C

I / O window 1 start-address high byte 80D 0D

I / O window 1 end-address low byte 80E 0E

I / O window 1 end-address high byte 80F 0F

Memory window 0 start-address low byte 810 10

Memory window 0 start-address high byte 811 11

Memory window 0 end-address low byte 812 12

Memory window 0 end-address high byte 813 13

Memory window 0 offset-address low byte 814 14

Memory window 0 offset-address high byte 815 15

Card detect and general control 816 16

Reserved 817 17

Memory window 1 start-address low byte 818 18

Memory window 1 start-address high byte 819 19

Memory window 1 end-address low byte 81A 1A

Memory window 1 end-address high byte 81B 1B

Memory window 1 offset-address low byte 81C 1C

Memory window 1 offset-address high byte 81D 1D

Global control 81E 1E

Reserved 81F 1F

Memory window 2 start-address low byte 820 20

Memory window 2 start-address high byte 821 21

Memory window 2 end-address low byte 822 22