4−21

4.37 Power-Management Capabilities Register

This register contains information on the capabilities of the PC Card function related to power management. The

CardBus bridge supports the D0, D1, D2, and D3 power states. See Table 4−13 for a complete description of the

register contents.

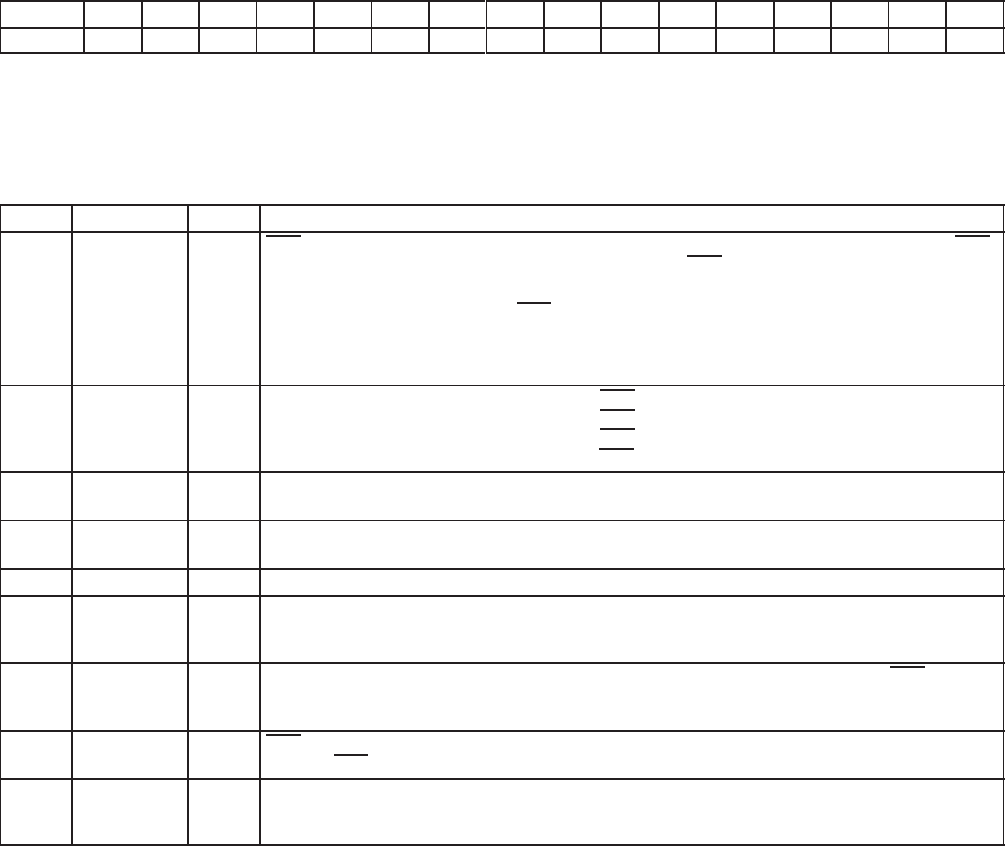

Bit 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Default 1 1 1 1 1 1 1 0 0 0 0 1 0 0 1 0

Register: Power-management capabilities

Offset: A2h

Type: Read/Write, Read-only

Default: FE12h

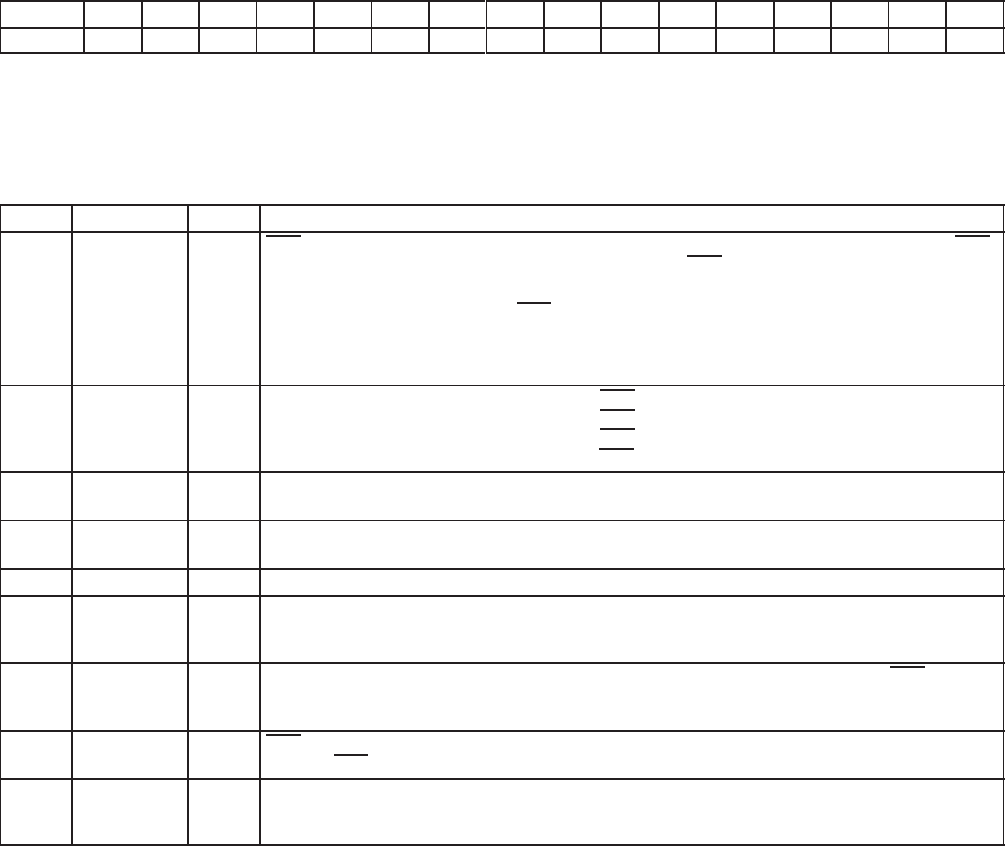

Table 4−13. Power-Management Capabilities Register Description

BIT SIGNAL TYPE FUNCTION

PME support. This 5-bit field indicates the power states from which the controller function may assert PME.

A 0b for any bit indicates that the function cannot assert the PME

signal while in that power state. These

five bits return 11111b when read. Each of these bits is described below:

15 PME_Suppor

RW

Bit 15 defaults to 1b indicating the PME signal can be asserted from the D3

cold

state. This bit is R/W

because wake-up support from D3

cold

is contingent on the system providing an auxiliary power source to

the V

CC

terminals. If the system designer chooses not to provide an auxiliary power source to the V

CC

terminals for D3

cold

wake-up support, then BIOS should write a 0b to this bit.

14−11 PME_Support R

Bit 14 contains the value 1b, indicating that the PME signal can be asserted from D3

hot

state.

Bit 13 contains the value 1b, indicating that the PME

signal can be asserted from D2 state.

Bit 12 contains the value 1b, indicating that the PME

signal can be asserted from D1 state.

Bit 11 contains the value 1b, indicating that the PME

signal can be asserted from the D0 state.

10 D2_Support R

D2 support. Bit 10 returns a 1b when read, indicating that the CardBus function supports the D2 device

power state.

9 D1_Support R

D1 support. Bit 9 returns a 1b when read, indicating that the CardBus function supports the D1 device

power state.

8−6 RSVD R Reserved. Bits 8−6 return 000b when read.

5 DSI R

Device-specific initialization. Bit 5 returns 1b when read, indicating that the CardBus controller function

requires special initialization (beyond the standard PCI configuration header) before the generic-class

device driver is able to use it.

4 AUX_PWR R

Auxiliary power source. Bit 4 is tied to bit 15. When bit 4 is set, it indicates that support for PME in D3

cold

requires auxiliary power supplied by the system by way of a proprietary delivery vehicle. When bit 4 is 0b,

it indicates that the function supplies its own auxiliary power source.

3 PMECLK R

PME clock. Bit 3 returns 0b when read, indicating that no host bus clock is required for the controller to

generate PME

.

2−0 VERSION R

Version. Bits 2−0 return 010b when read, indicating that the power-management registers (PCI offsets

A4h−A7h, see Sections 4.38−4.40) are defined in the PCI Bus Power Management Interface Specification

version 1.1.