MT9126 Preliminary Information

8-44

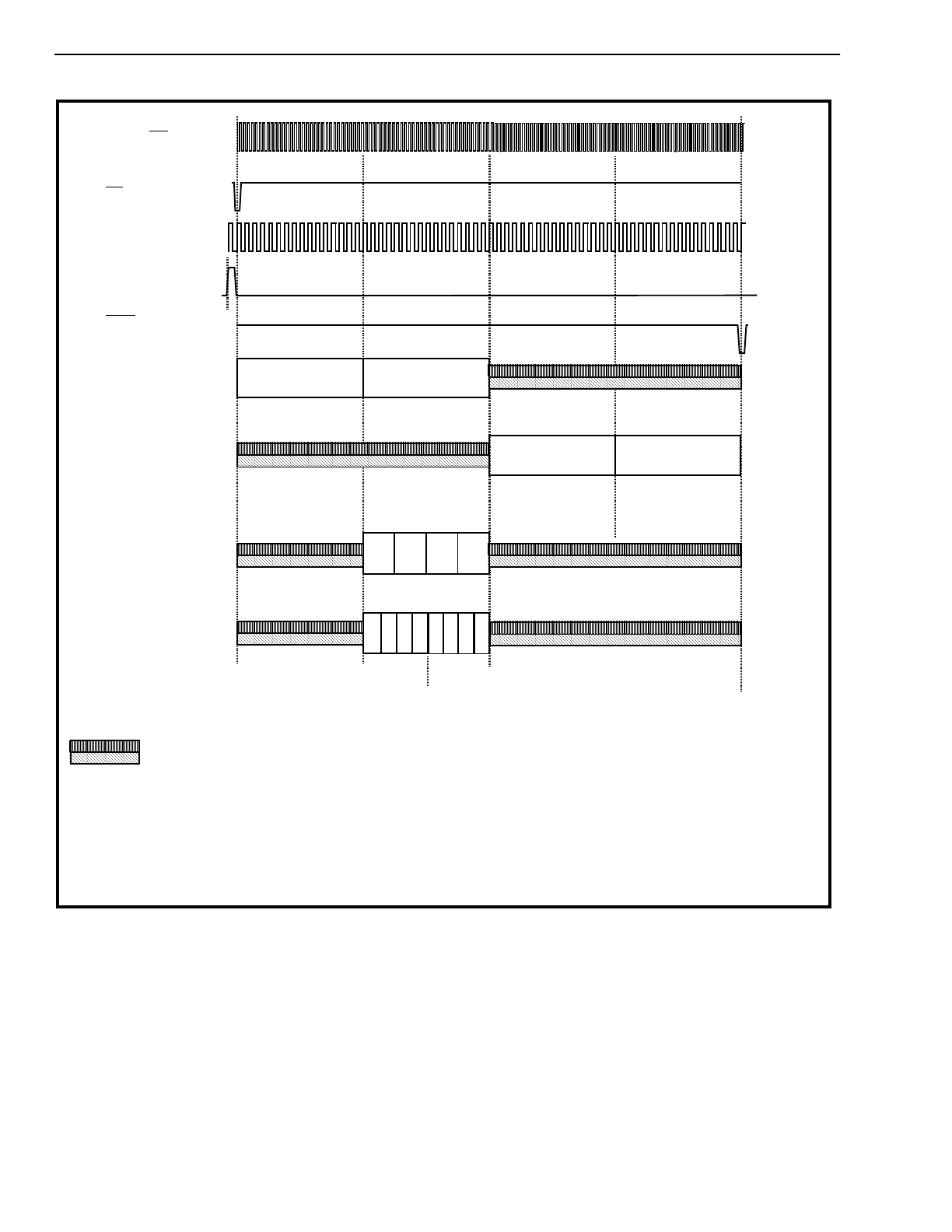

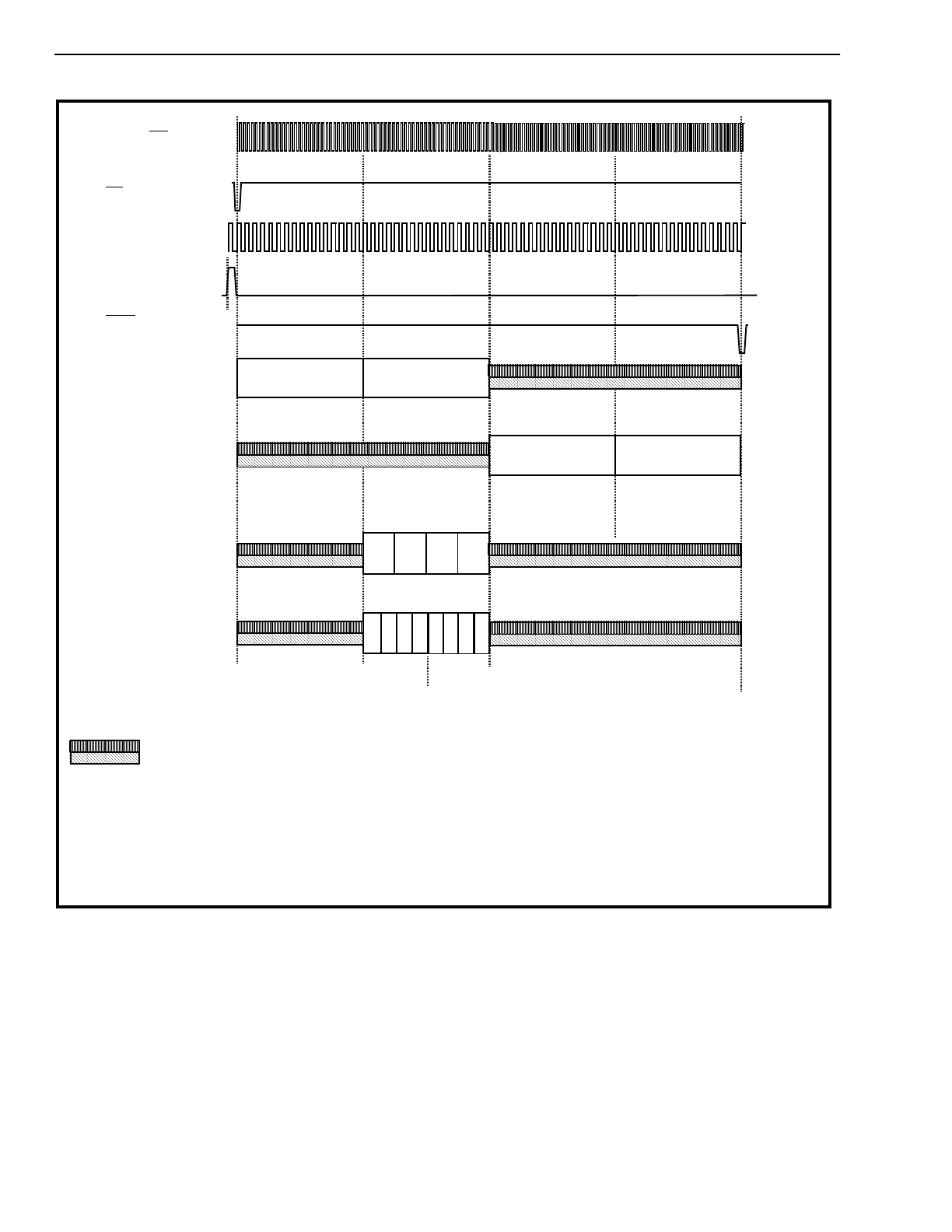

Figure 8 - ST-BUS 16-bit Linear PCM Relative Timing

MCLK (C4i)

F0i

C2o

ADPCMi/o

Note: D &C channels not supported in this mode.

SEL operated for

PCMi/o1

PCMi/o2

SSS 12 11 10 9 8 7 6 5 4 3 2 1 0 SSS 12 11 10 9 8 7 6 5 4 3 2 1 0

SSS 12 11 10 9 8 7 6 5 4 3 2 1 0

SSS 12 11 10 9 8 7 6 5 4 3 2 1 0

B1 B2

B3

B4

ADPCMi/o

(32/24 kb/s)

(16 kb/s)

F0od/ENB2

EN1

(output)

bit 4 = x at 24 kbit/s

B

1

12

SEL = 1

SEL = 0

B

2

B

3

B

4

12 12 12

B

1

12

B

2

B

3

B

4

12 12 12

1234 1234 1234 1234

B1 B2

B3

B4

16kb/s only

outputs = High impedance

inputs = don’t care

X = undetermined logic level output; don’t care input

Two frame delay from data input to data output

Outputs high impedance outside of channel boundaries