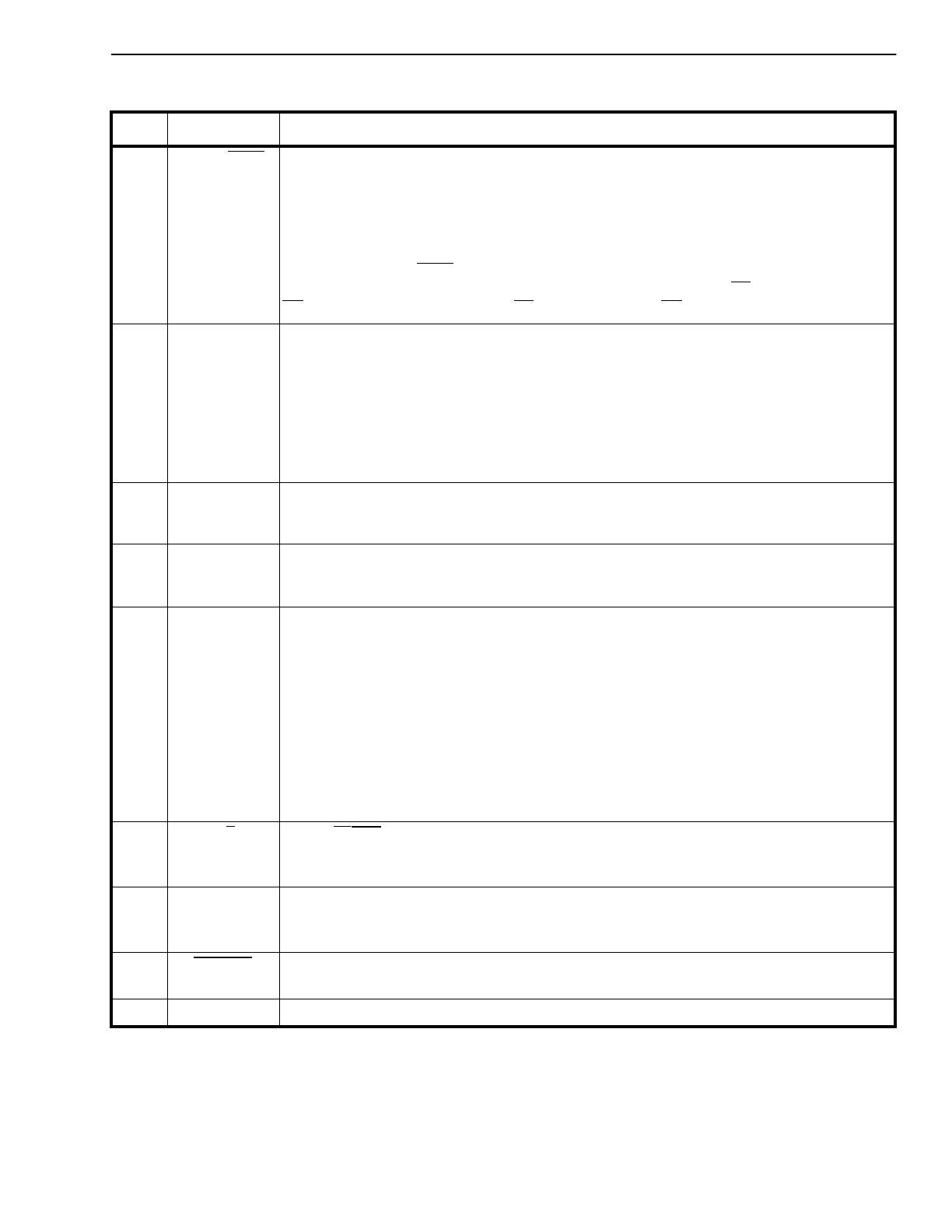

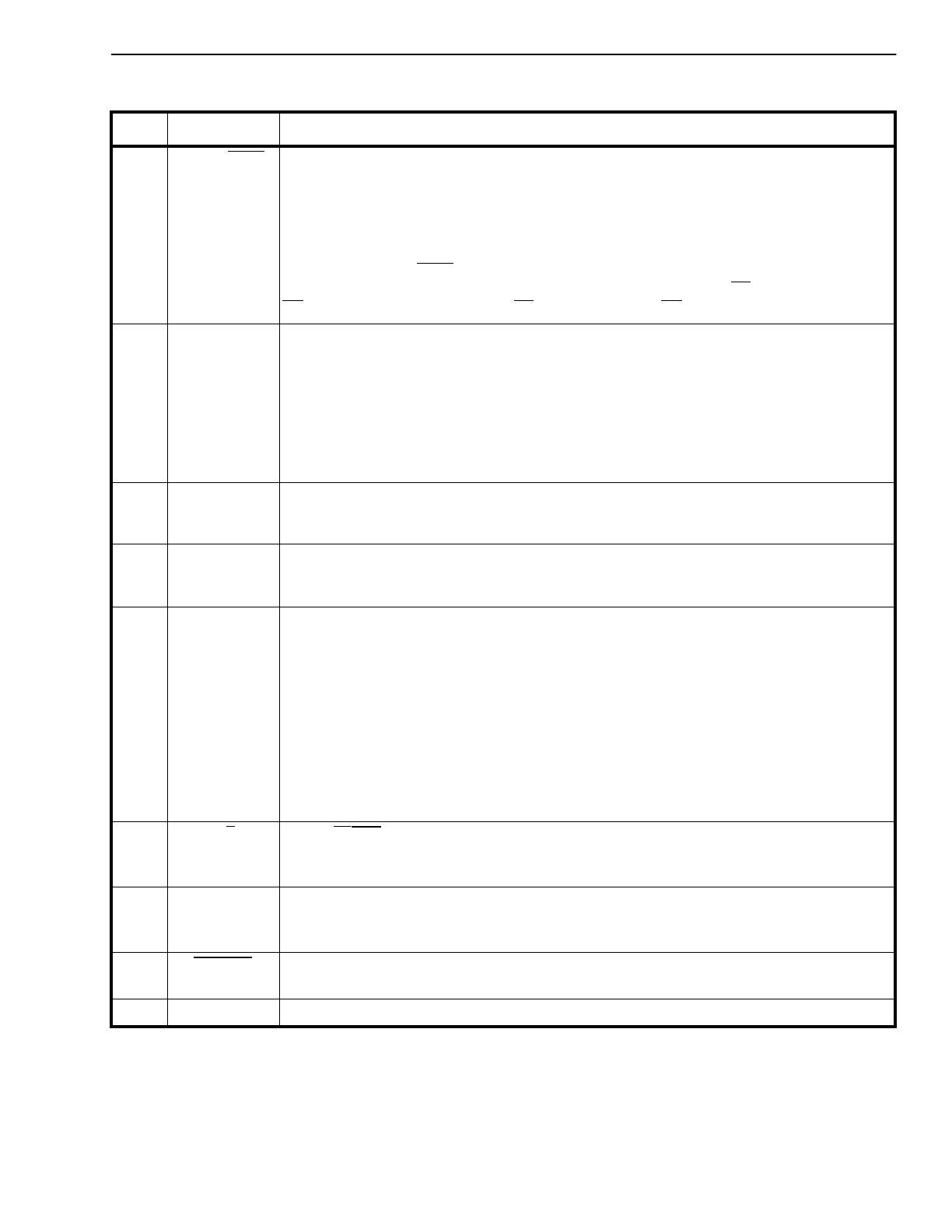

Preliminary Information MT9126

8-35

10 ENB2/F0od PCM B-Channel Enable Strobe 2 (Input) / Delayed Frame Pulse (Output).

SSI operation: ENB2 (Input). An 8-bit wide enable strobe input defining B2 channel

(AD)PCM data. A valid 8-bit strobe must be present at this input for SSI operation. See

Figures 4 & 6.

ST-BUS operation: F0od

(Output). This pin is a delayed frame strobe output. When LIN-

EAR=0, this becomes a delayed frame pulse output occurring 64 C4

clock cycles after

F0i

and when LINEAR = 1 at 128 C4 clock cycles after F0i . See Figures 7, 8, 9 & 14.

11 ENB1 PCM B-Channel Enable Strobe 1 (Input).

SSI operation: An 8-bit wide enable strobe input defining B1 channel (AD)PCM data. A

valid 8-bit strobe must be present at this input for SSI operation.

ST-BUS operation: When tied to V

SS

transparent bypass of the ST-BUS D- and C- chan-

nels is enabled. When tied to V

DD

the ST-BUS D-channel and C-channel output timeslots

are forced to a high-impedance state.

12 PCMo2 Serial PCM Stream 2 (Output). 128 kbit/s to 4096 kbit/s serial companded/linear PCM

output stream. Clocked out by rising edge of BCLK in SSI mode. Clocked out by MCLK

divided by two in ST-BUS mode. See Figure 14.

13 PCMi2 Serial PCM Stream 2 (Input). 128 kbit/s to 4096 kbit/s serial companded/linear PCM input

stream. Data bits are clocked in on falling edge of BCLK in SSI mode. Clocked in at the

3/4 bit position of MCLK in ST-BUS mode. See Figure 14.

14 SEL SELECT (Input).

PCM bypass mode: When SEL=0 the PCM1 port is selected for PCM bypass operation

and when SEL=1 the PCM2 port is selected for PCM bypass operation.

See Figures 6 & 9.

16 kbit/s transcoding mode:

SSI Operation - in 16 kbit/s transcoding mode, the ADPCM words are assigned to the I/O

timeslot defined by ENB2 when SEL=1 and by ENB1 when SEL=0. See Figure 4.

ST-BUS operation- in 16 kbit/s transcoding mode, the ADPCM words are assigned to the

B2 timeslot when SEL=1 and to the B1 timeslot when SEL=0. See Figure 9.

15 A/µ

A-Law/µ−Law Select (Input). This input pin selects µ−Law companding when set to

logic 0, and A-Law companding when set to logic 1. This control is for all channels .This

input is ignored in Linear mode during which it may be tied to V

SS

or V

DD

.

16 FORMAT FORMAT Select (Input). Selects ITU-T PCM coding when high and Sign-Magnitude

PCM coding when low. This control is for all channels.This input is ignored in Linear

mode during which it may be tied to V

SS

or V

DD

.

17 PWRDN

Power-down (Input). An active low reset forcing the device into a low power mode

where all outputs are high-impedance and device operation is halted.

18 IC Internal Connection (Input). Tie to V

SS

for normal operation.

Pin Description

Pin # Name Description