LMC6482

www.ti.com

SNOS674D –NOVEMBER 1997–REVISED MARCH 2013

LMC6482 CMOS Dual Rail-To-Rail Input and Output Operational Amplifier

Check for Samples: LMC6482

1

FEATURES

APPLICATIONS

2

• (Typical Unless Otherwise Noted)

• Data Acquisition Systems

• Rail-to-Rail Input Common-Mode Voltage • Transducer Amplifiers

Range (Ensured Over Temperature)

• Hand-held Analytic Instruments

• Rail-to-Rail Output Swing (within 20mV of

• Medical Instrumentation

Supply Rail, 100kΩ Load)

• Active Filter, Peak Detector, Sample and Hold,

• Ensured 3V, 5V and 15V Performance

pH Meter, Current Source

• Excellent CMRR and PSRR: 82dB

• Improved Replacement for TLC272, TLC277

• Ultra Low Input Current: 20fA

• High Voltage Gain (R

L

= 500kΩ): 130dB

• Specified for 2kΩ and 600Ω Loads

• Available in VSSOP Package

DESCRIPTION

The LMC6482 provides a common-mode range that extends to both supply rails. This rail-to-rail performance

combined with excellent accuracy, due to a high CMRR, makes it unique among rail-to-rail input amplifiers.

It is ideal for systems, such as data acquisition, that require a large input signal range. The LMC6482 is also an

excellent upgrade for circuits using limited common-mode range amplifiers such as the TLC272 and TLC277.

Maximum dynamic signal range is assured in low voltage and single supply systems by the LMC6482's rail-to-rail

output swing. The LMC6482's rail-to-rail output swing is ensured for loads down to 600Ω.

Ensured low voltage characteristics and low power dissipation make the LMC6482 especially well-suited for

battery-operated systems.

LMC6482 is also available in VSSOP package which is almost half the size of a SOIC-8 device.

See the LMC6484 data sheet for a Quad CMOS operational amplifier with these same features.

3V Single Supply Buffer Circuit

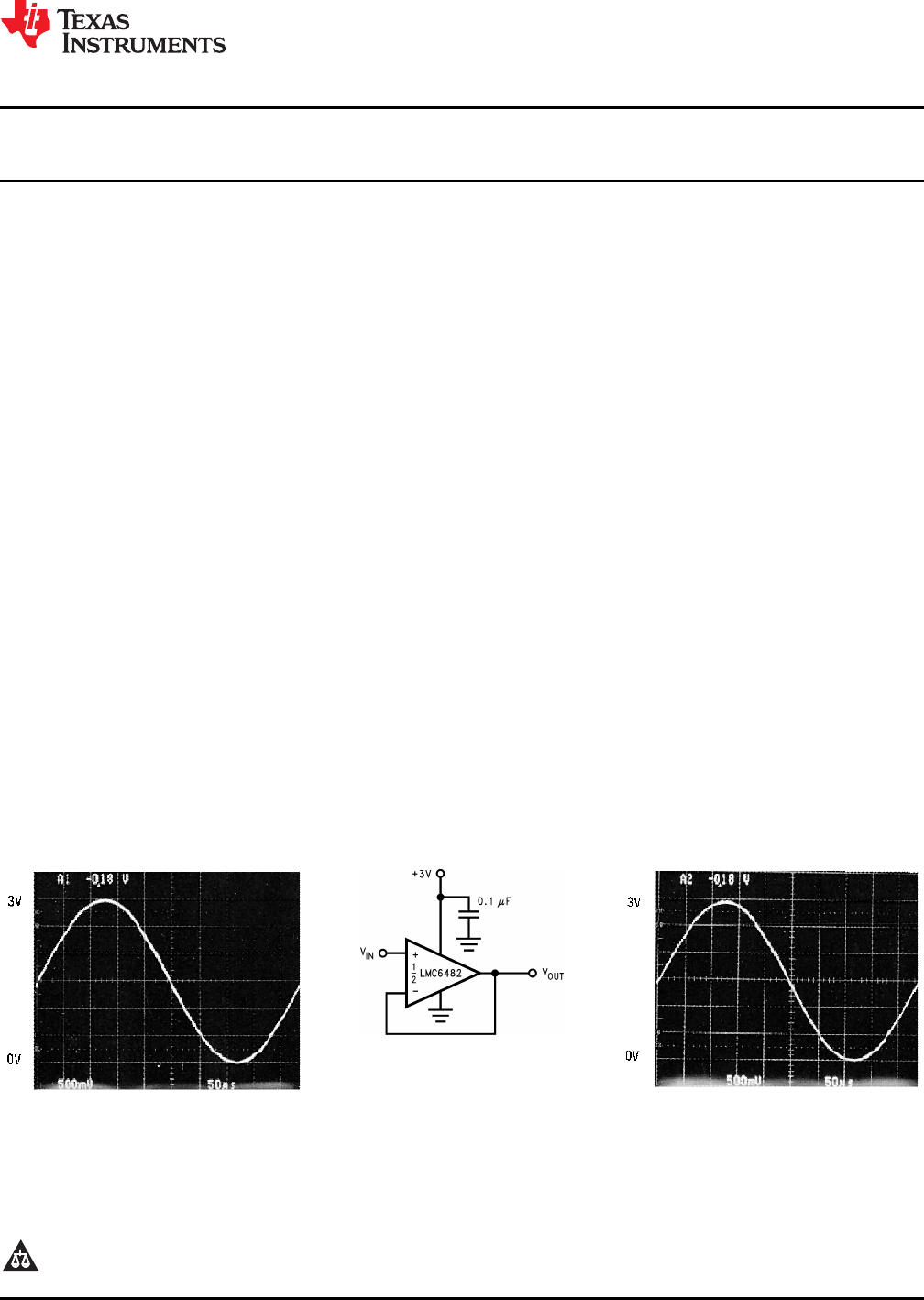

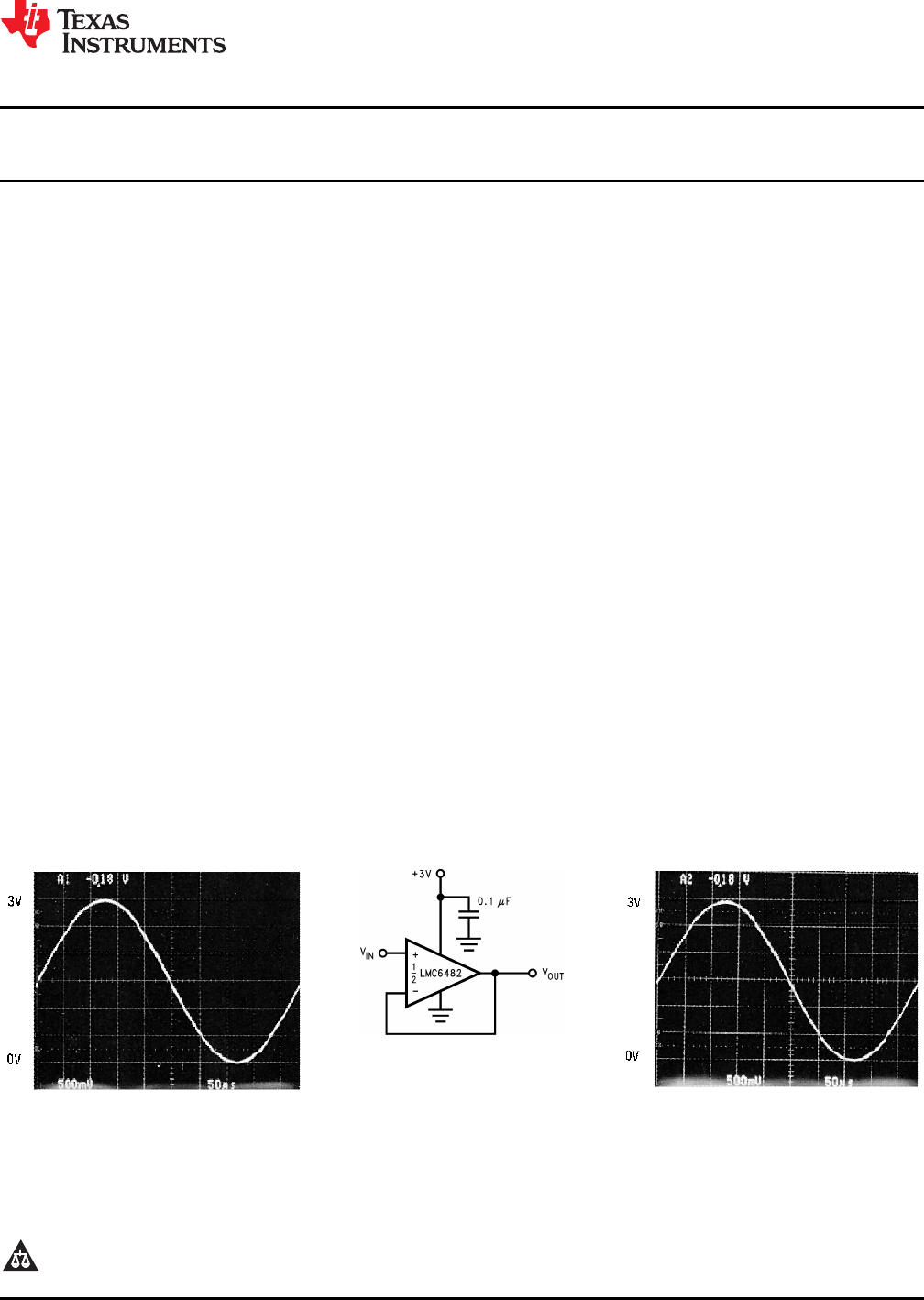

Figure 1. Rail-To-Rail Input Figure 2. Figure 3. Rail-To-Rail Output

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

2All trademarks are the property of their respective owners.

PRODUCTION DATA information is current as of publication date.

Copyright © 1997–2013, Texas Instruments Incorporated

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.