36 Altera Corporation

MAX 3000A Programmable Logic Device Family Data Sheet

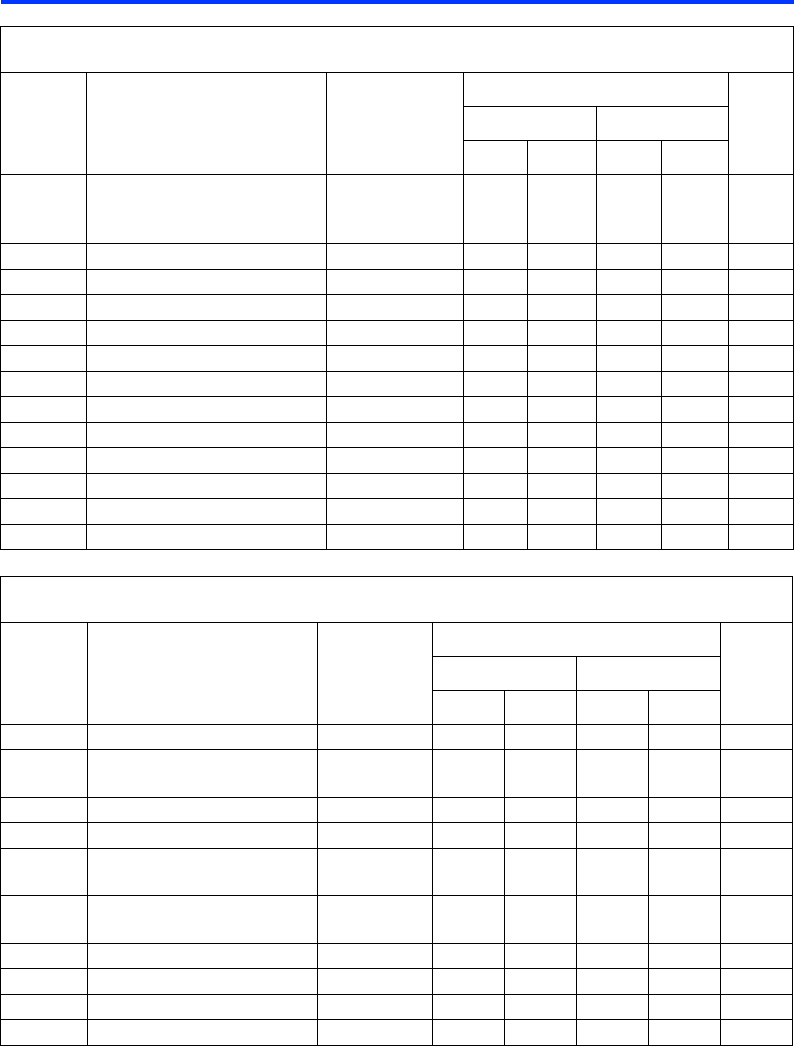

t

ZX3

Output buffer enable delay, slow

slew rate = on

V

CCIO

= 2.5 V or 3.3 V

C1 = 35 pF 9.0 10.0 ns

t

XZ

Output buffer disable delay C1 = 5 pF 4.0 5.0 ns

t

SU

Register setup time 2.1 2.9 ns

t

H

Register hold time 0.9 1.2 ns

t

RD

Register delay 1.2 1.6 ns

t

COMB

Combinatorial delay 0.8 1.2 ns

t

IC

Array clock delay 1.6 2.1 ns

t

EN

Register enable time 1.0 1.3 ns

t

GLOB

Global control delay 1.5 2.0 ns

t

PRE

Register preset time 2.3 3.0 ns

t

CLR

Register clear time 2.3 3.0 ns

t

PIA

PIA delay (2) 2.4 3.2 ns

t

LPA

Low–power adder (5) 4.0 5.0 ns

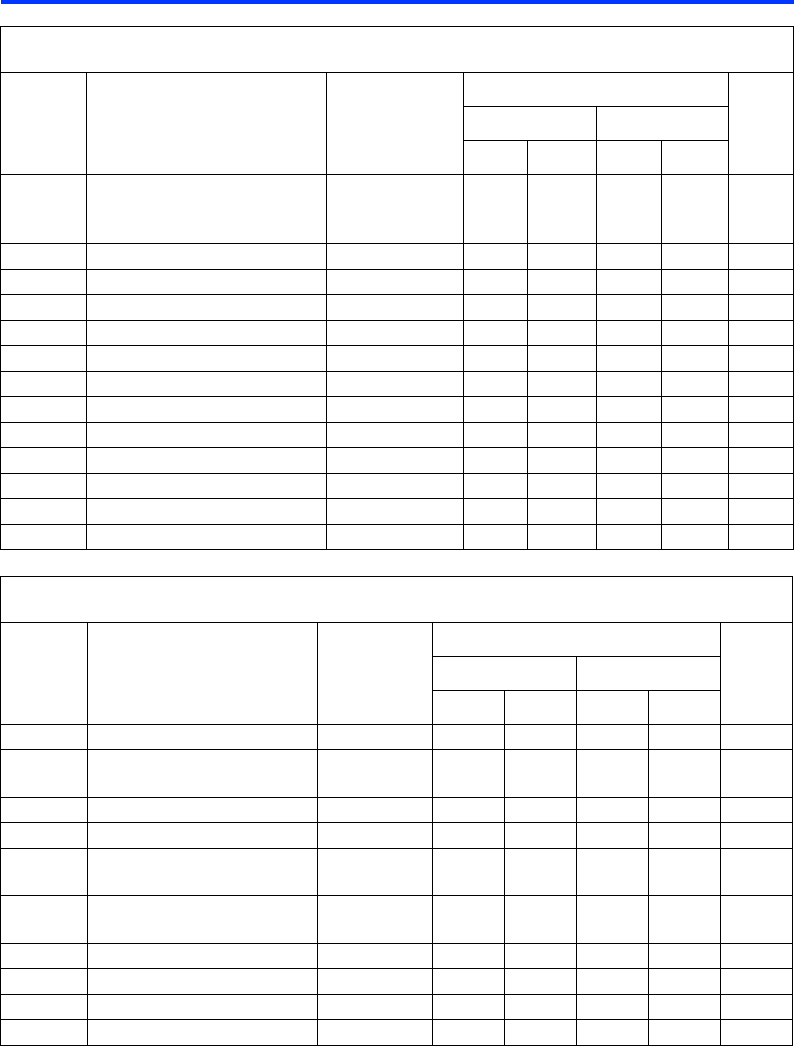

Table 24. EPM3512A External Timing Parameters Note (1)

Symbol Parameter Conditions Speed Grade Unit

-7 -10

Min Max Min Max

t

PD1

Input to non-registered output C1 = 35 pF (2) 7.5 10.0 ns

t

PD2

I/O input to non-registered

output

C1 = 35 pF (2) 7.5 10.0 ns

t

SU

Global clock setup time (2) 5.6 7.6 ns

t

H

Global clock hold time (2) 0.0 0.0 ns

t

FSU

Global clock setup time of fast

input

3.0 3.0 ns

t

FH

Global clock hold time of fast

input

0.0 0.0 ns

t

CO1

Global clock to output delay C1 = 35 pF 1.0 4.7 1.0 6.3 ns

t

CH

Global clock high time 3.0 4.0 ns

t

CL

Global clock low time 3.0 4.0 ns

t

ASU

Array clock setup time (2) 2.5 3.5 ns

Table 23. EPM3256A Internal Timing Parameters (Part 2 of 2) Note (1)

Symbol Parameter Conditions Speed Grade Unit

–7 –10

Min Max Min Max