CS4344/5/6/8

12 DS613PP2

4.APPLICATIONS

The CS4344 family accepts data at standard audio sample rates including 48, 44.1 and 32 kHz in SSM, 96,

88.2 and 64 kHz in DSM, and 192, 176.4 and 128 kHz in QSM. Audio data is input via the serial data input

pin (SDIN). The Left/Right Clock (LRCK) determines which channel is currently being input on SDIN,

and the optional Serial Clock (SCLK) clocks audio data into the input data buffer. The CS4344/5/6/8 differ

in serial data formats as shown in Figures 7-10.

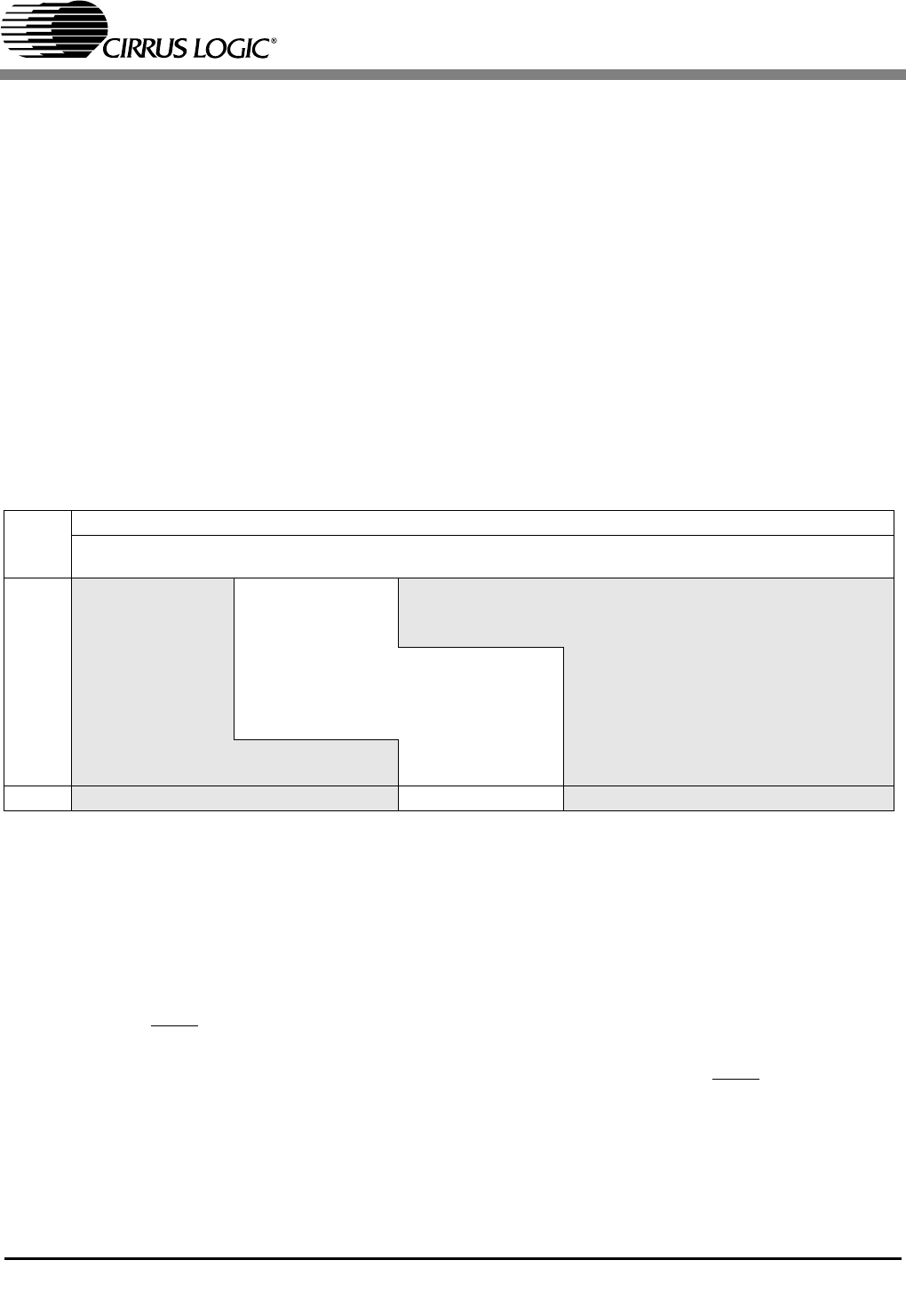

4.1 Master Clock

MCLK/LRCK must be an integer ratio as shown in Table 1. The LRCK frequency is equal to Fs, the fre-

quency at which words for each channel are input to the device. The MCLK-to-LRCK frequency ratio and

speed mode is detected automatically during the initialization sequence by counting the number of MCLK

transitions during a single LRCK period and by detecting the absolute speed of MCLK. Internal dividers

are set to generate the proper clocks. Table 1 illustrates several standard audio sample rates and the re-

quired MCLK and LRCK frequencies. Please note there is no required phase relationship, but MCLK,

LRCK and SCLK must be synchronous.

Table 1. Common Clock Frequencies

4.2 Serial Clock

The serial clock controls the shifting of data into the input data buffers. The CS4344 family supports both

external and internal serial clock generation modes. Refer to Figures 7-10 for data formats.

4.2.1 External Serial Clock Mode

The CS4344 family will enter the External Serial Clock Mode when 16 low to high transitions are de-

tected on the DEM/SCLK pin during any phase of the LRCK period. When this mode is enabled, the

Internal Serial Clock Mode and de-emphasis filter cannot be accessed. The CS4344 family will switch

to Internal Serial Clock Mode if no low to high transitions are detected on the DEM/SCLK pin for 2

consecutive frames of LRCK. Refer to Figure 12.

LRCK

(kHz)

MCLK (MHz)

64x 96x 128x 192x 256x 384x 512x 768x 1024x 1152x

32

- ---8.1920 12.2880 - - 32.7680 36.8640

44.1

- ---11.2896 16.9344 22.5792 33.8680 45.1580 -

48

- ---12.2880 18.4320 24.5760 36.8640 49.1520 -

64

- - 8.1920 12.2880 - - 32.7680 49.1520 - -

88.2

- - 11.2896 16.9344 22.5792 33.8680 - - - -

96

- - 12.2880 18.4320 24.5760 36.8640 - - - -

128

8.1920 12.2880 - - 32.7680 49.1520 - - - -

176.4

11.2896 16.9344 22.5792 33.8680 - - - - - -

192

12.2880 18.4320 24.5760 36.8640 - - - - - -

Mode

QSM DSM SSM