26 ©Copyright 2005 Cirrus Logic, Inc. DS651UM23

Version 2.3

CobraNet Hardware User’s Manual

Host Management Interface (HMI)

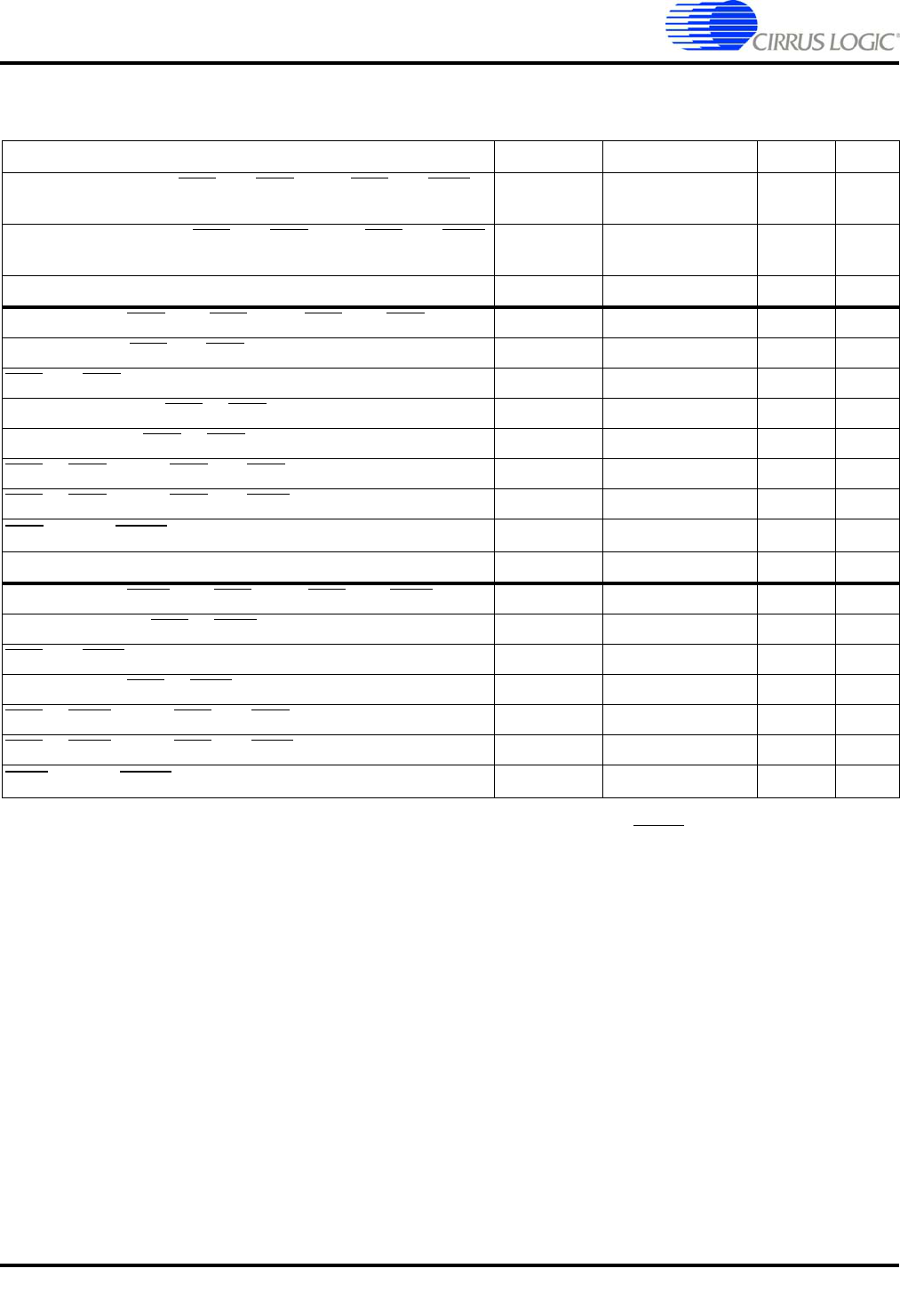

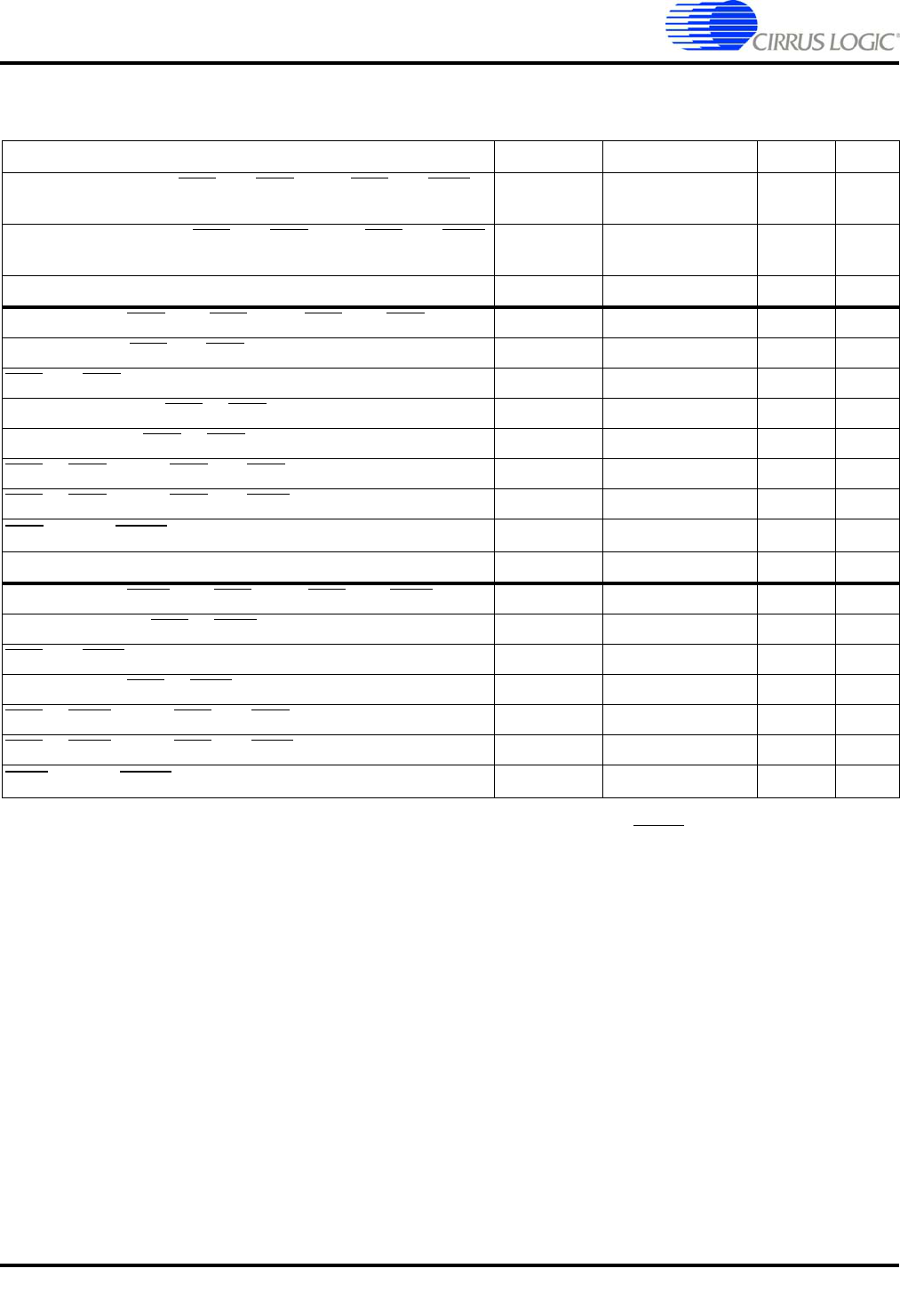

7.3 Host Port Timing - Intel

®

Mode

(C

L

= 20 pF)

NOTES:1. The system designer should be aware that the actual maximum speed of the communication port may

be limited by the firmware application. Hardware handshaking on the HREQ

pin/bit should be observed

to prevent overflowing the input data buffer.

Parameter Symbol Min Max Unit

Address setup before HCS

and HRD low or HCS and HWR

low

t

ias

5-ns

Address hold time after HCS

and HRD low or HCS and HWR

high

t

iah

5-ns

Read

Delay between HRD

then HCS low or HCS then HRD low t

icdr

0-ns

Data valid after HCS

and HRD low t

idd

-18ns

HCS

and HRD low for read t

irpw

24 - ns

Data hold time after HCS

or HRD high t

idhr

8-ns

Data high-Z after HCS

or HRD high t

idis

-18ns

HCS

or HRD high to HCS and HRD low for next read t

ird

30 - ns

HCS

or HRD high to HCS and HWR low for next write t

irdtw

30 - ns

HRD

rising to HREQ rising

t

irdirqhl

-12ns

Write

Delay between HWR

then HCS low or HCS then HWR low t

icdw

0-ns

Data setup before HCS

or HWR high t

idsu

8-ns

HCS

and HWR low for write t

iwpw

24 - ns

Data hold after HCS

or HWR high t

idhw

8-ns

HCS

or HWR high to HCS and HRD low for next read t

iwtrd

30 - ns

HCS

or HWR high to HCS and HWR low for next write t

iwd

30 - ns

HWR

rising to HREQ falling

t

iwrbsyl

-12ns