10 ©Copyright 2005 Cirrus Logic, Inc. DS651UM23

Version 2.3

CobraNet Hardware User’s Manual

Pinout and Signal Descriptions

4.1 CS1810xx & CS4961xx Package Pinouts

4.1.1 CS1810xx/CS4961xx Pinout

Ta bl e 1 lists the pinout for the 144-pin LQFP CS1810xx/CS4961xx device. The interfaces

for these signals are expanded in the following sections.

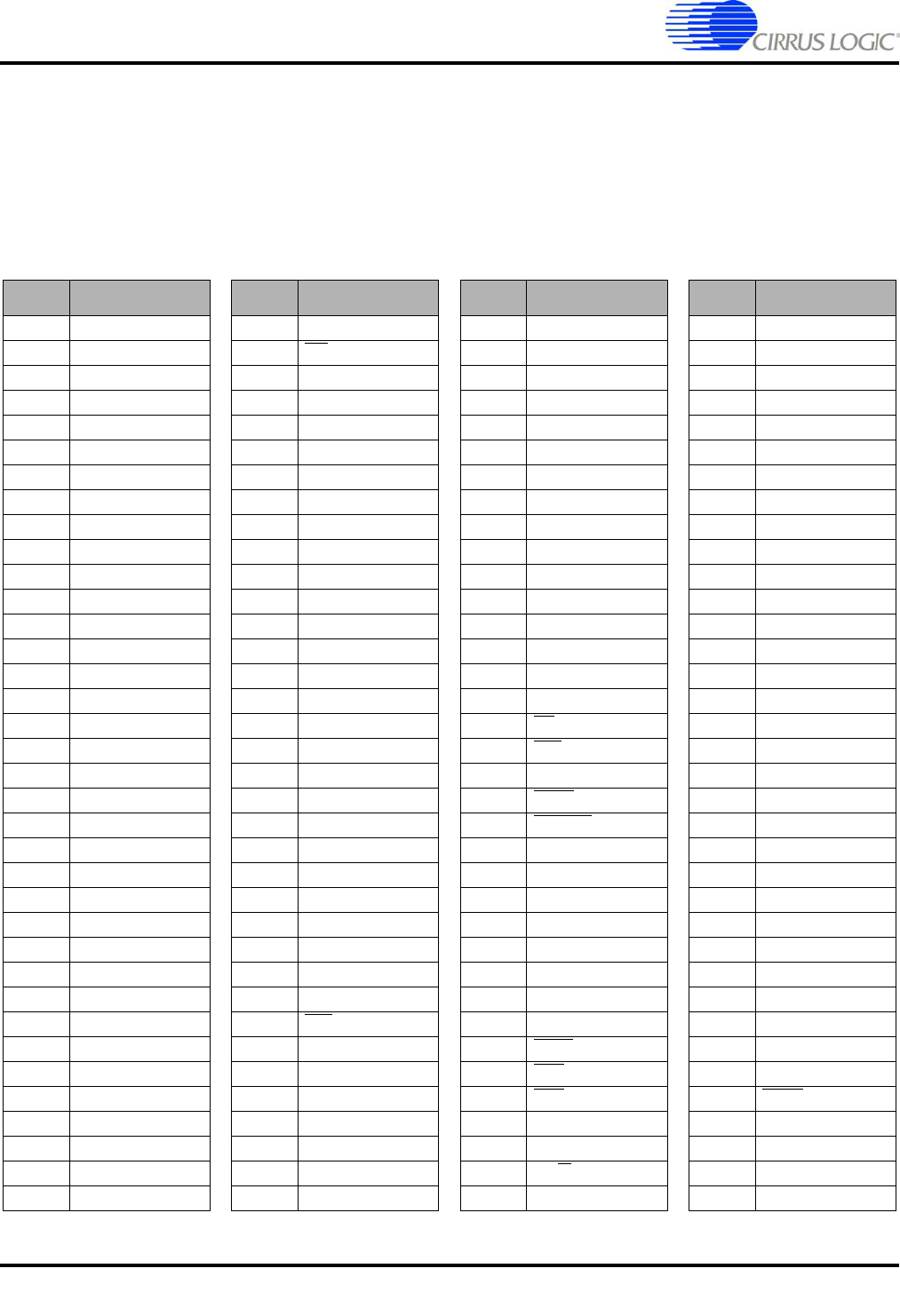

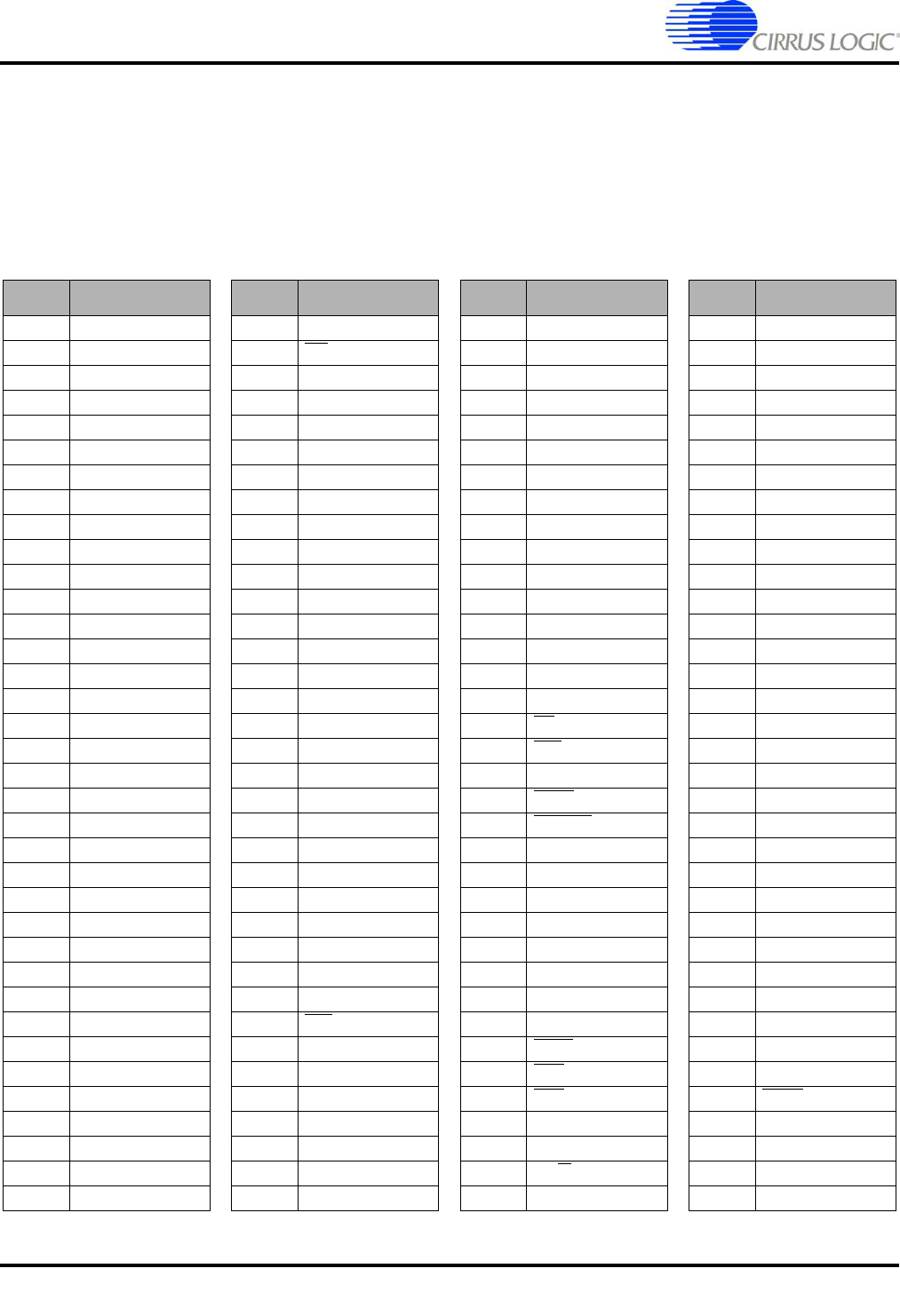

Table 1. CS1810xx/CS4961xx Pin Assignments

Pin # Pin Name Pin # Pin Name Pin # Pin Name Pin # Pin Name

1 VCXO_CTRL 37 DATA1 73 VDDIO 109 HADDR1

2

MCLK_SEL 38 WE 74 ADDR10 110 HADDR0

3

DBDA 39 DATA0 75 ADDR14 111 HDATA7

4

DBCK 40 DATA15 76 GND 112 HDATA6

5

NC 41 DATA14 77 ADDR13 113 VDDIO

6

NC 42 DATA13 78 NC 114 HDATA5

7

NC 43 DATA12 79 NC 115 HDATA4

8

DAO_MCLK 44 VDDIO 80 NC 116 GND

9

TEST 45 DATA11 81 NC 117 HDATA3

10

VDDD 46 DATA10 82 ADDR15 118 HDATA2

11

HS3 47 GND 83 VDDD 119 VDDD

12

NC 48 DATA9 84 ADDR16 120 HDATA1

13

GND 49 DATA8 85 ADDR17 121 HDATA0

14

DAO2_LRCLK 50 NC 86 GND 122 GND

15

DAO1_DATA3 51 NC 87 ADDR18 123 XTAL_OUT

16

DAO1_DATA2/HS2 52 NC 88 ADDR19 124 XTO

17

DAO1_DATA1/HS1 53 NC 89 OE 125 XTI

18

VDDIO 54 VDDD 90 CS1 126 GND_a

19

DAO1_DATA0/HS0 55 ADDR12 91 VDDIO 127 FILT2

20

DAO1_SCLK 56 ADDR11 92 MUTE 128 FILT1

21

GND 57 GND 93 HRESET 129 VDDA

22

DAO1_LRCLK 58 ADDR9 94 GND 130 VDDD

23

UART_TX_OE 59 ADDR8 95 WATCHDOG 131 DAI1_DATA3

24

VDDD 60 VDDIO 96 IOWAIT 132 DAI1_DATA2

25

UART_TXD 61 ADDR7 97 REFCLK_IN 133 GND

26

UART_RXD 62 ADDR6 98 VDDD 134 DAI1_DATA1

27

GND 63 GND 99 GPIO0 135 DAI1_DATA0

28

NC 64 ADDR5 100 GPIO1 136 VDDIO

29

DATA7 65 CS2 101 GND 137 DAI1_SCLK

30

DATA6 66 VDDD 102 HACK 138 DAI1_LRCLK

31

DATA5 67 ADDR4 103 HDS 139 GND

32

DATA4 68 ADDR3 104 HEN 140 HREQ

33 VDDIO 69 GND 105 HADDR3 141 NC

34

DATA3 70 ADDR2 106 HADDR2 142 NC

35

DATA2 71 ADDR1 107 HR/W 143 IRQ1

36

GND 72 ADDR0 108 GPIO2 144 IRQ2