CobraNet Hardware User’s Manual

Mechanical Drawings and Schematics

DS651UM23 ©Copyright 2005 Cirrus Logic, Inc. 49

Version 2.3

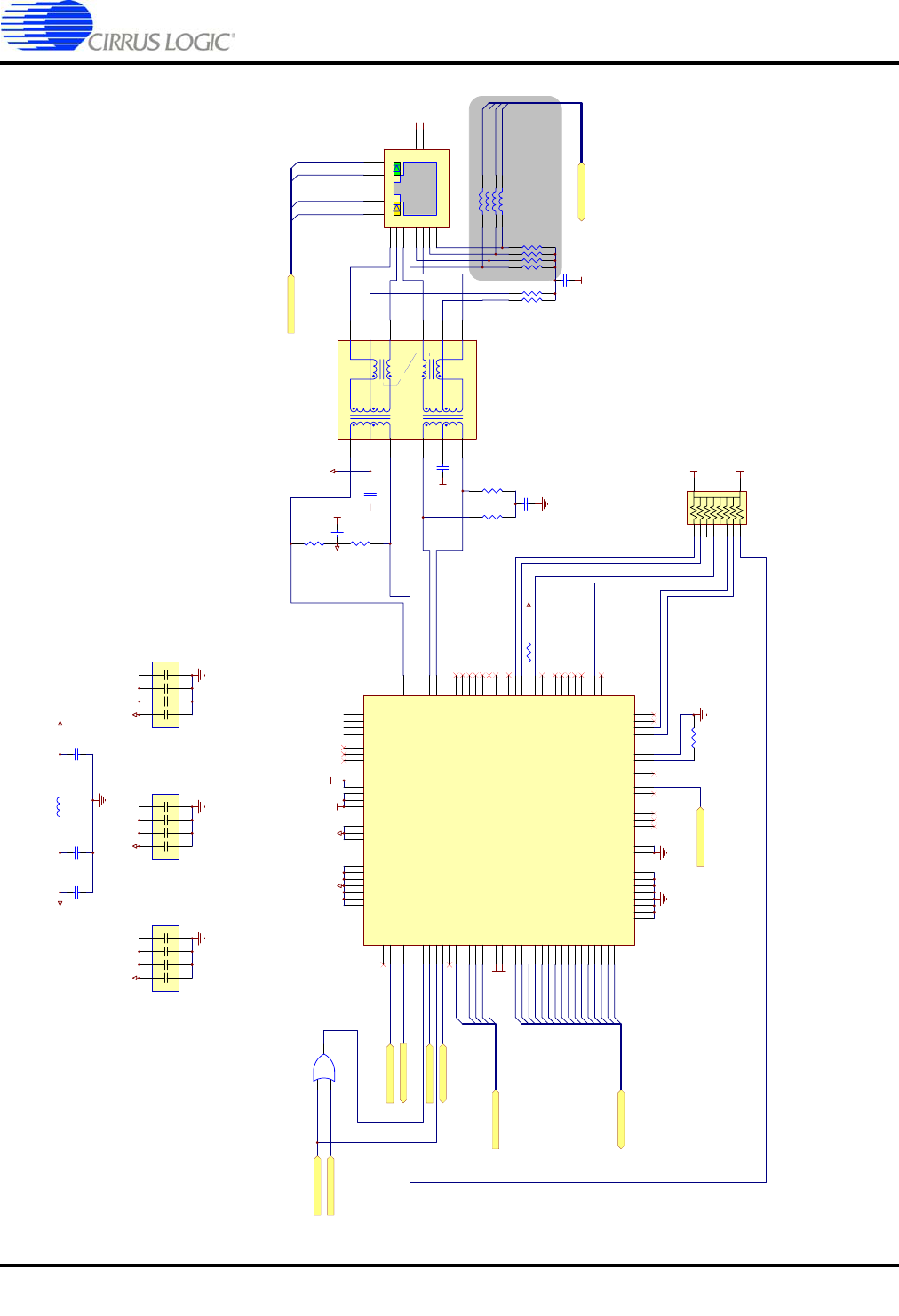

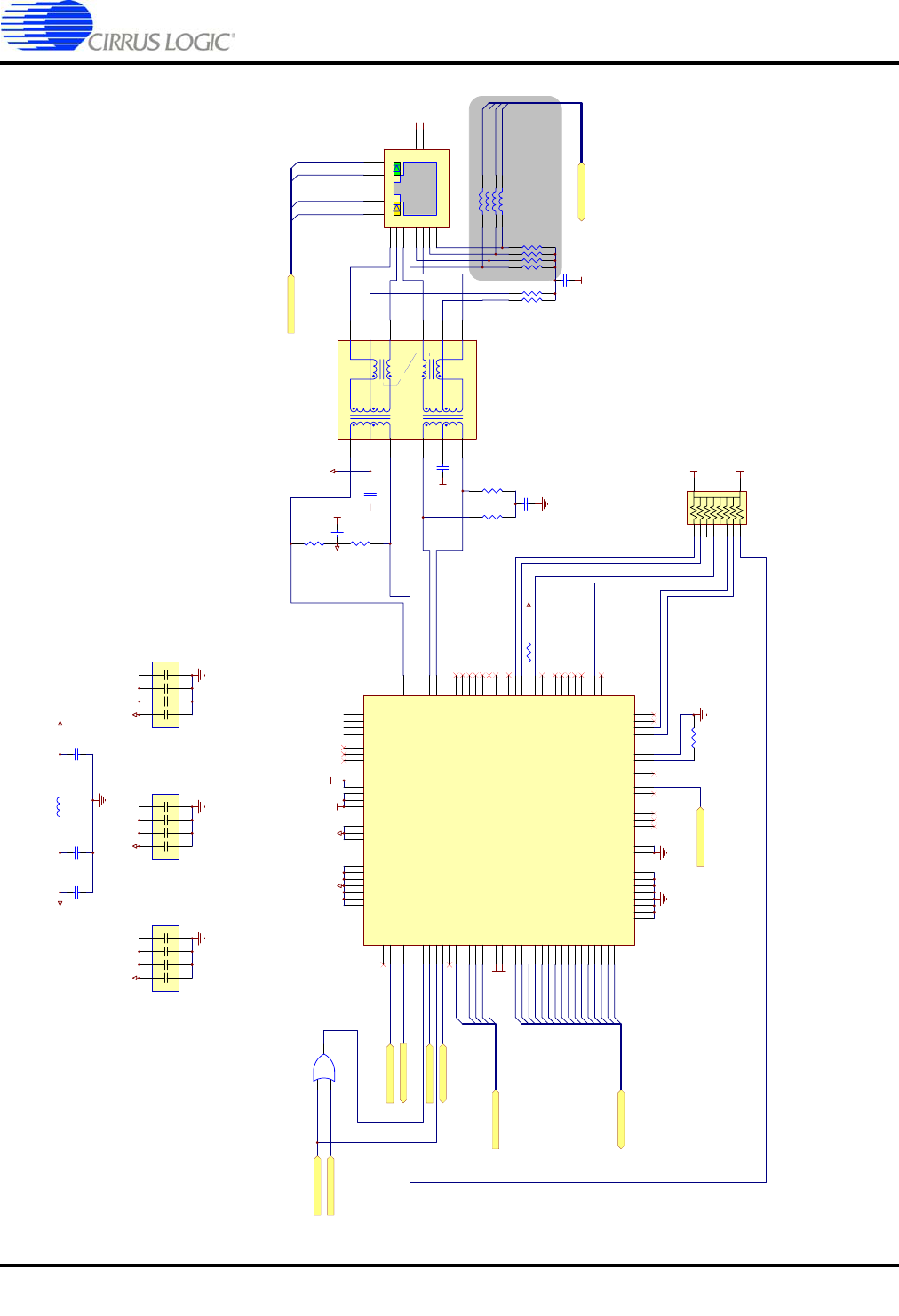

Figure 29. CM-2 RevF Schematic Page 6 of 7

IOR#

1

IOW#

2

AEN

3

IOWAIT

4

DVDD

5

SD0

6

SD1

7

SD2

8

SD3

9

SD4

10

SD5

11

SD6

12

SD7

13

RST

14

DGND

15

TEST1

16

TEST2

17

TEST3

18

TEST4

19

DVDD

20

X2_25M

21

X1_25M

22

DGND

23

SD

24

BGGND

25

BGRES

26

AVDD

27

AVDD

28

RXI+

29

RXI-

30

AGND

31

AGND

32

TXO+

33

TXO-

34

AVDD

35

DVDD

36

LINK_I

37

RXD0

38

RXD1

39

RXD2

40

RXD3

41

DGND

42

CRS

43

COL

44

RX_DV

45

RX_ER

46

RX_CLK

47

TEST5

48

TX_CLK

49

TXD0

50

TXD1

51

TXD2

52

TXD3

53

TX_EN

54

DVDD

55

MDIO

56

MDC

57

DGND

58

CLK20MO

59

SPEED#

60

DUP#

61

LINKACT#

62

DGND

63

EEDI

64

EEDO

65

EECK

66

EECS

67

GPIO0

68

GPIO1

69

GPIO2

70

GPIO3

71

DVDD

72

DVDD

73

NC

74

NC

75

DGND

76

NC

77

LINK_O

78

WAKEUP

79

PW_RST#

80

DGND

81

SD15

82

SD14

83

SD13

84

SD12

85

SD11

86

SD10

87

SD9

88

SD8

89

DVDD

90

IO16

91

CMD

92

SA4

93

SA5

94

SA6

95

SA7

96

SA8

97

SA9

98

DGND

99

INT

100

U8

DM9000

R23

49.9 Ohm, 1%

R24

49.9 Ohm, 1%

R21

R22

49.9 Ohm, 1%

R26

6.8K Ohm, 1%

C30

0.1 uF

C31

0.1 uF

C32

0.1 uF

C29

0.1 uF

Keep res close to chip pins.

GND

VCC_PHY2 GND

R34

75 Ohm, 1%

R33

R35

R36

R37

R38

75 Ohm, 1%

FB8

FB9

FB10

FB11

FBEAD, 68 Ohm @ 100 MHz

C49

0.01 uF, 2KV

Note: See Text Warning

Warning: Failure to properly install and

configure the aux. Ethernet signals can result in

very bad things (i.e., fire, smoke, bad hair days).

If power is supplied via the RJ-45 connector then

only the ferrite beads are installed (not the

resistors). If power is not supplied via the RJ-45

then the resistors are installed and the beads are

not.

VCC_PHY2VCC_+3.3

VCC_+3.3

VCC_+3.3

DATA0

DATA1

DATA2

DATA3

DATA4

DATA5

DATA6

DATA7

DATA8

DATA9

DATA10

DATA11

DATA12

DATA13

DATA14

DATA15

ADDR[0..19]

DATA[0..15]

ADDR[0..19]

DATA[0..15]

HRESET_BUF#

VCC_+3.3

GND

WE#

MAC_CS#

IOWAIT

HRESET_BUF#

WE#

IOWAIT

MAC_IRQ1

MAC_IRQ1

The secondary Ethernet MAC and connector are optional.

If it is not required then all parts on this page can be depopulated

(or removed entirely from a new design based on this circuit).

ADDR0

ADDR2

ADDR3

ADDR1

ADDR4

VCC_+3.3 VCC_PHY2

C47

0.01 uF

FB7

FBEAD, 68 Ohm @ 100 MHz

C8

10 uF, X5R, 6.3 Volts

C9

10 uF, X5R, 6.3 Volts

VCC_+3.3 VCC_PHY2

1

2

3

45

6

7

8

CN11

0.1 uF, 4x Array

1

2

3

45

6

7

8

CN9

0.1 uF, 4x Array

VCC_+3.3

1

2

3

45

6

7

8

CN10

0.1 uF, 4x Array

GND

12

3

4

5

6

7

8

9

10

RN8

3.3K Ohm, 8x Array

GND

CLK_25

CLK_25

VCC_PHY2OE#

MAC_CS#

OE#

MAC_CS#

12

13

11

U10D

74LVC32

R52

3.3K Ohm

VCC_+3.3

1

2

3

4

5

6

7

8

S1

S2

L1

L2

L3

L4

J6

RJ45

1

2

3

4

5

6 19

20

21

22

23

24

TXD+

TXD-

TXD+

TXD-

RXD+

RXD+

RXD- RXD-

T1A

H2006A

GND

SHIELD

SHIELD

SHIELD

LED_BUF[0..7]

LED_BUF[0..7]

AUX_POWER0

AUX_POWER1

AUX_POWER2

AUX_POWER3

AUX_POWER[0..3]

AUX_POWER[0..3]

LED_BUF4

LED_BUF5

LED_BUF6

LED_BUF7