CC1000

SWRS048A Page 43 of 55

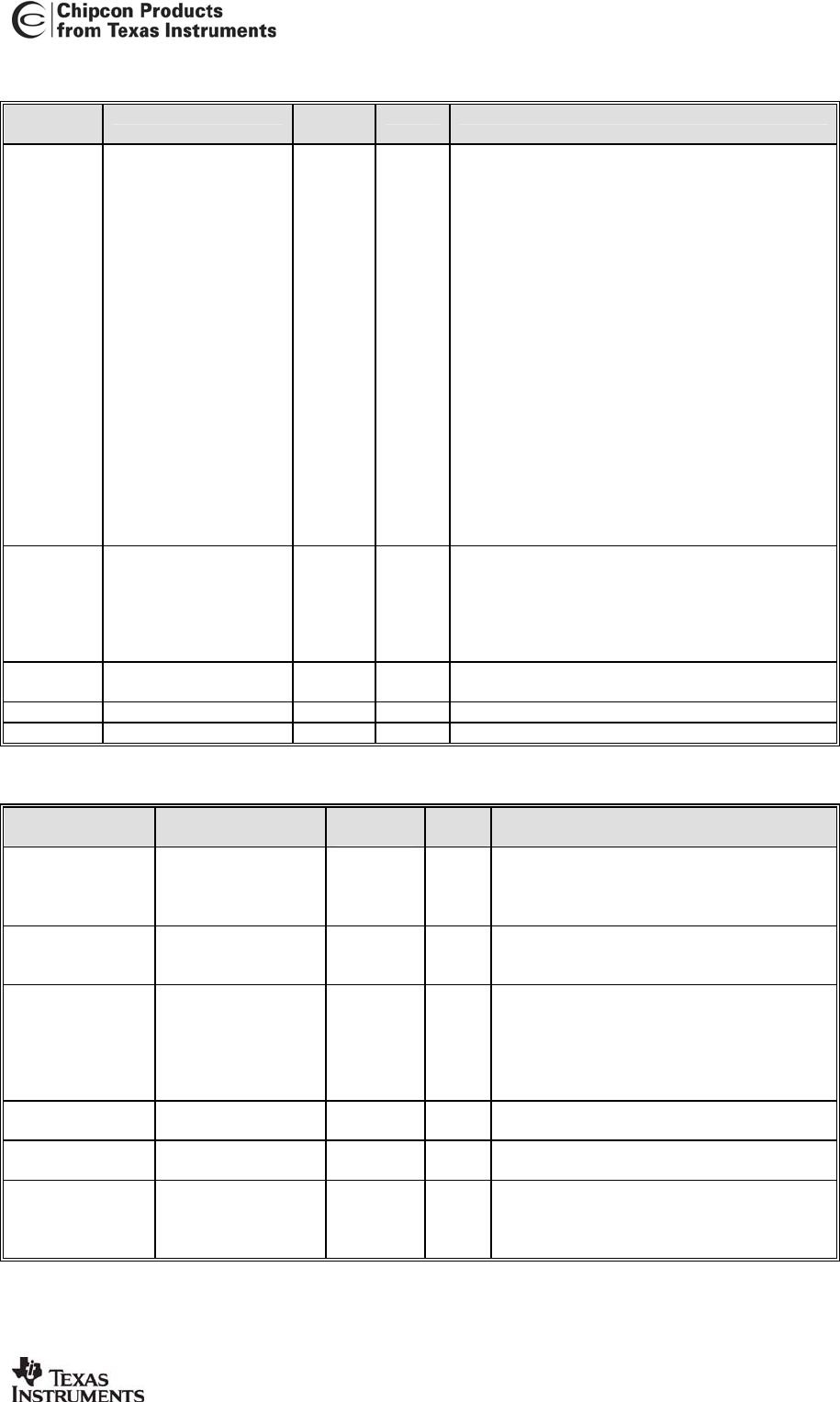

LOCK Register (0Dh)

REGISTE

R

NAME Default

value

Active Description

LOCK[7:4] LOCK_SELECT[3:0] 0000 - Selection of signals to CHP_OUT (LOCK) pin

0000 : Normal, pin can be used as CHP_OUT

0001 : LOCK_CONTINUOUS (active high)

0010 : LOCK_INSTANT (active high)

0011 : ALARM_H (active high)

0100 : ALARM_L (active high)

0101 : CAL_COMPLETE (active high)

0110 : IF_OUT

0111 : REFERENCE_DIVIDER Output

1000 : TX_PDB (active high, activates external PA

when TX_PD=0)

1001 : Manchester Violation (active high)

1010 : RX_PDB (active high, activates external

LNA when RX_PD=0)

1011 : Not defined

1100 : Not defined

1101 : LOCK_AVG_FILTER

1110 : N_DIVIDER Output

1111 : F_COMP

LOCK[3] PLL_LOCK_

ACCURACY

0 - 0 : Sets Lock Threshold = 127, Reset Lock

Threshold = 111. Corresponds to a worst case

accuracy of 0.7%

1 : Sets Lock Threshold = 31, Reset Lock

Threshold =15. Corresponds to a worst case

accuracy of 2.8%

LOCK[2] PLL_LOCK_

LENGTH

0 -

0 : Normal PLL lock window

1 : Not used

LOCK[1] LOCK_INSTANT - - Status bit from Lock Detector

LOCK[0] LOCK_CONTINUOUS - - Status bit from Lock Detector

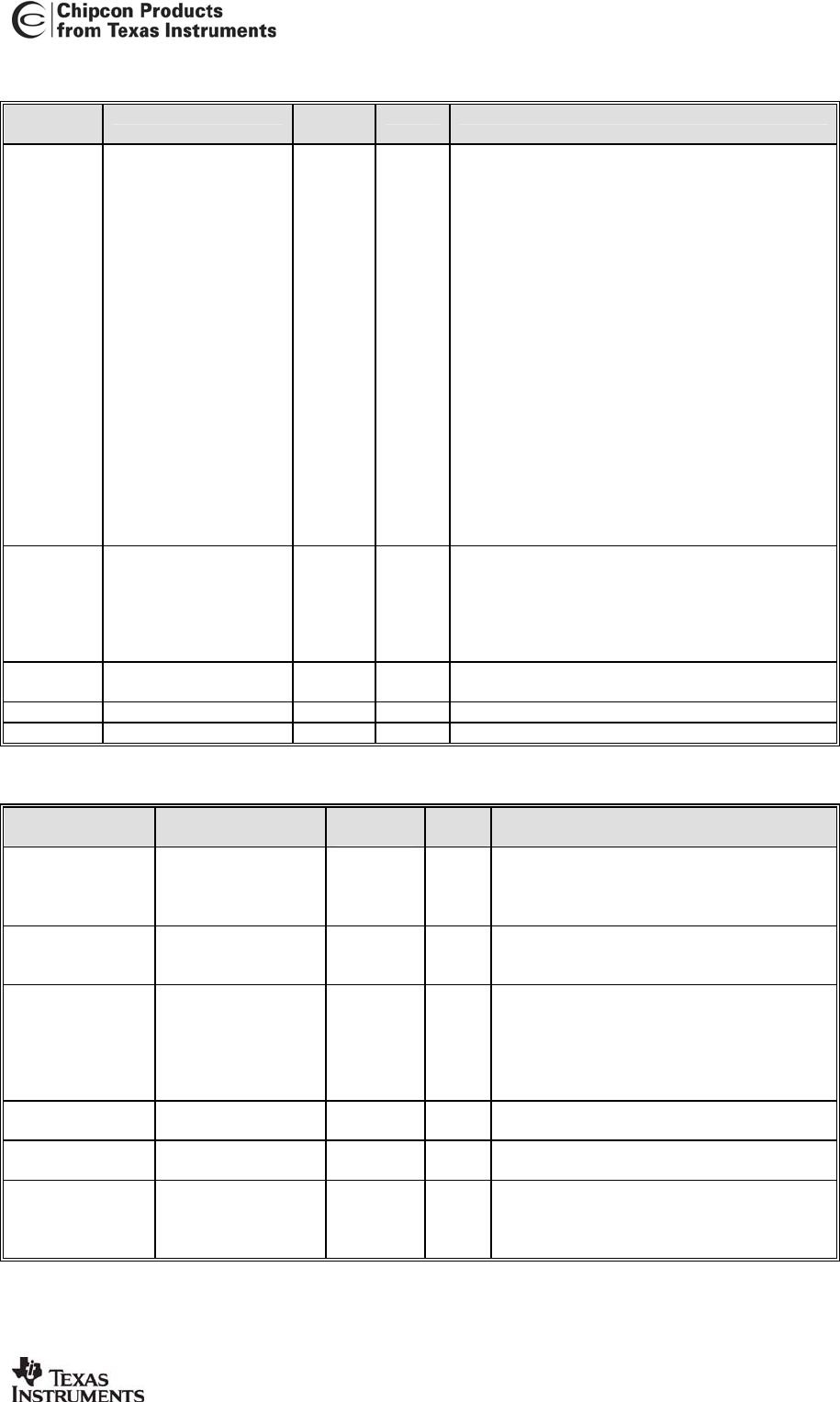

CAL Register (0Eh)

REGISTER NAME Default

value

Active Description

CAL[7] CAL_START 0

↑ ↑ 1 : Calibration started

0 : Calibration inactive

CAL_START must be set to 0 after

calibration is done

CAL[6] CAL_DUAL 0 H 1 : Store calibration in both A and B

0 : Store calibration in A or B defined by

MAIN[6]

CAL[5] CAL_WAIT 0 H 1 : Normal Calibration Wait Time

0 : Half Calibration Wait Time

The calibration time is proportional to the

internal reference frequency. 2 MHz

reference frequency gives 14 ms wait time.

CAL[4] CAL_CURRENT 0 H 1 : Calibration Current Doubled

0 : Normal Calibration Current

CAL[3] CAL_COMPLETE 0 H Status bit defining that calibration is

complete

CAL[2:0] CAL_ITERATE 101 H Iteration start value for calibration DAC

000 – 101: Not used

110 : Normal start value

111 : Not used