289

2545M–AVR–09/07

ATmega48/88/168

Note: 1. The default value of SUT1..0 results in maximum start-up time for the default clock source.

See Table 8-9 on page 35 for details.

2. The default setting of CKSEL3..0 results in internal RC Oscillator @ 8 MHz. See Table 8-8 on

page 35 for details.

3. The CKOUT Fuse allows the system clock to be output on PORTB0. See “Clock Output Buffer”

on page 36 for details.

4. See “System Clock Prescaler” on page 37 for details.

The status of the Fuse bits is not affected by Chip Erase. Note that the Fuse bits are locked if

Lock bit1 (LB1) is programmed. Program the Fuse bits before programming the Lock bits.

27.2.1 Latching of Fuses

The fuse values are latched when the device enters programming mode and changes of the

fuse values will have no effect until the part leaves Programming mode. This does not apply to

the EESAVE Fuse which will take effect once it is programmed. The fuses are also latched on

Power-up in Normal mode.

27.3 Signature Bytes

All Atmel microcontrollers have a three-byte signature code which identifies the device. This

code can be read in both serial and parallel mode, also when the device is locked. The three

bytes reside in a separate address space. For the ATmega48/88/168 the signature bytes are

given in Table 27-8.

27.4 Calibration Byte

The ATmega48/88/168 has a byte calibration value for the internal RC Oscillator. This byte

resides in the high byte of address 0x000 in the signature address space. During reset, this byte

is automatically written into the OSCCAL Register to ensure correct frequency of the calibrated

RC Oscillator.

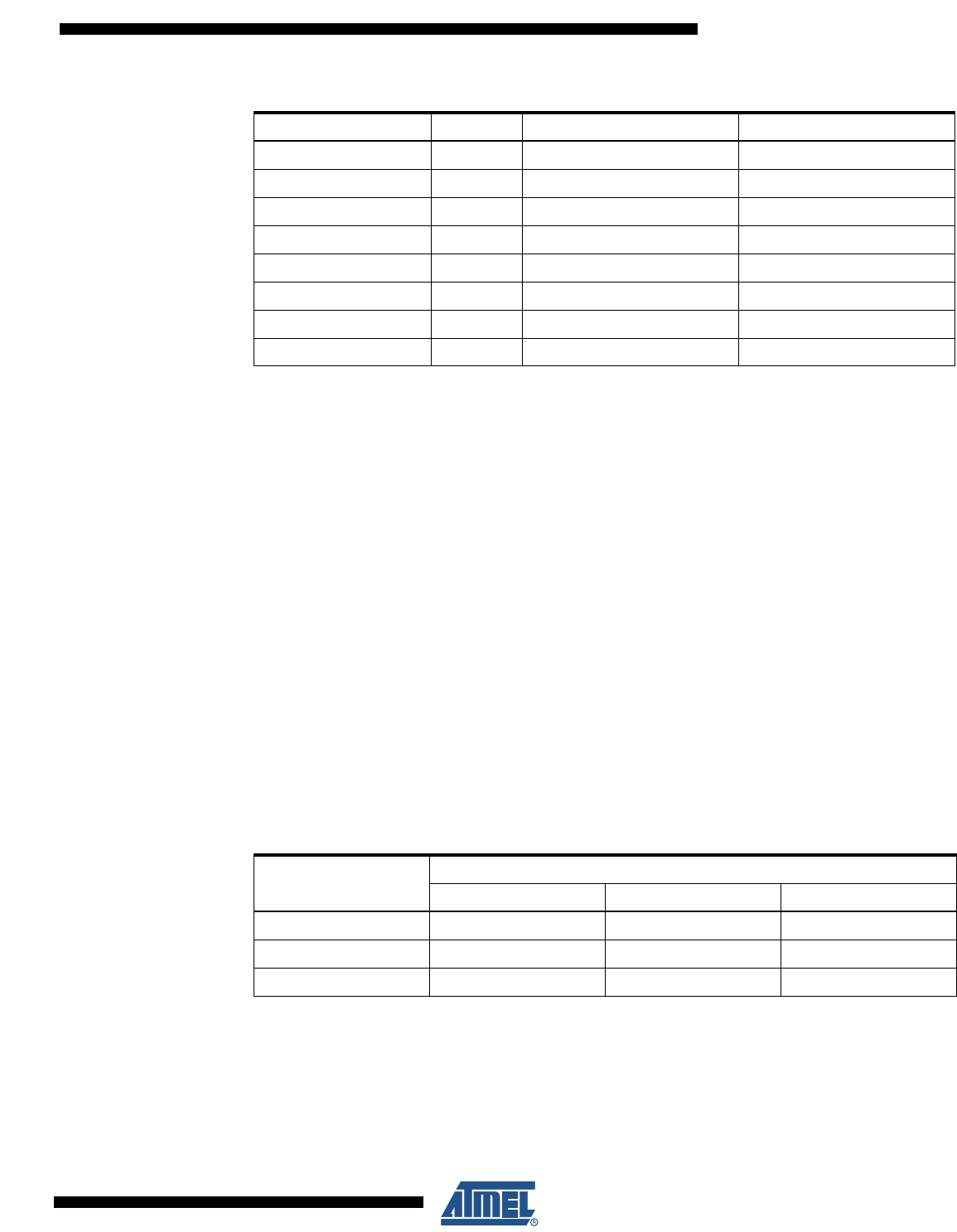

Table 27-7. Fuse Low Byte

Low Fuse Byte Bit No Description Default Value

CKDIV8

(4)

7 Divide clock by 8 0 (programmed)

CKOUT

(3)

6 Clock output 1 (unprogrammed)

SUT1 5 Select start-up time 1 (unprogrammed)

(1)

SUT0 4 Select start-up time 0 (programmed)

(1)

CKSEL3 3 Select Clock source 0 (programmed)

(2)

CKSEL2 2 Select Clock source 0 (programmed)

(2)

CKSEL1 1 Select Clock source 1 (unprogrammed)

(2)

CKSEL0 0 Select Clock source 0 (programmed)

(2)

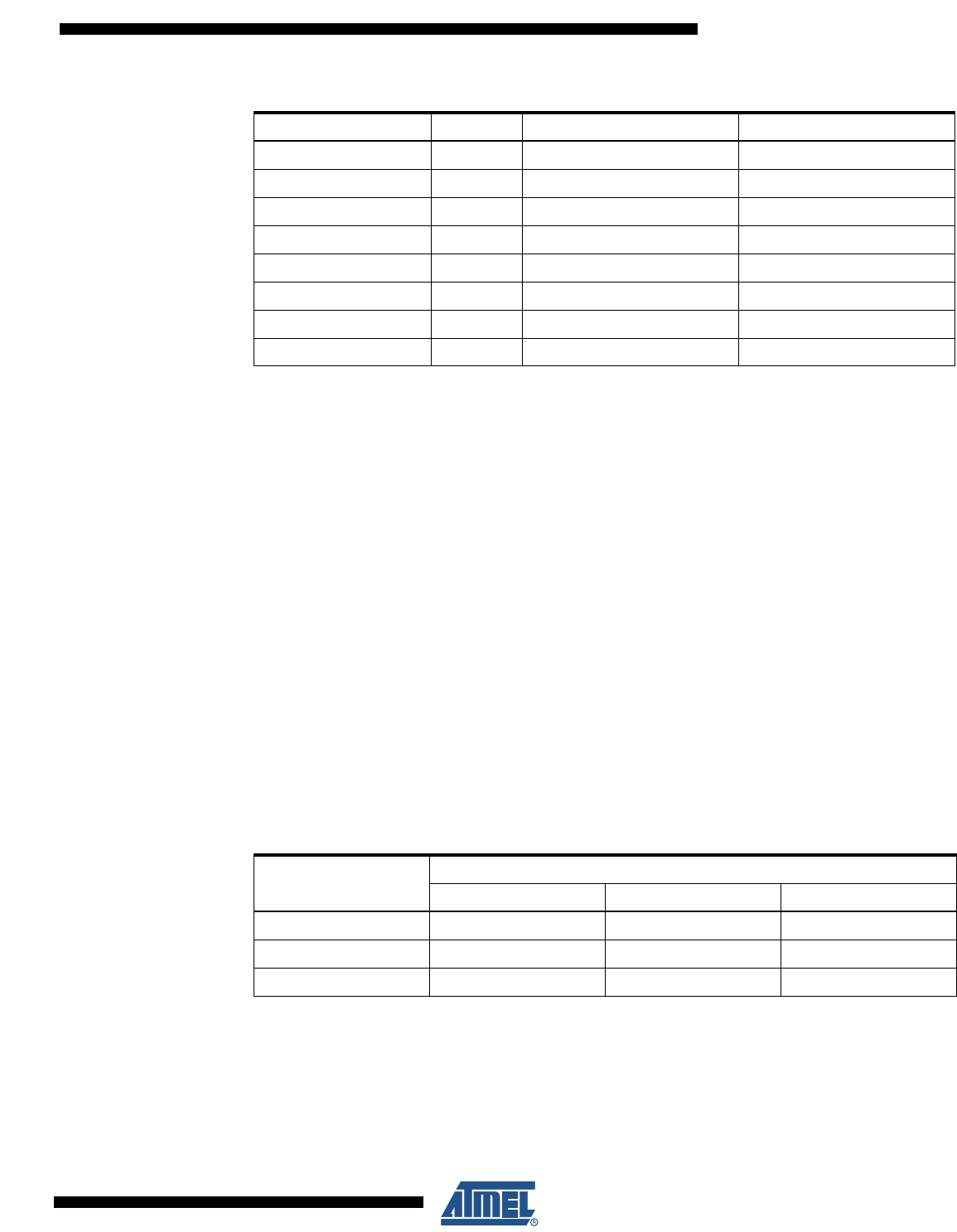

Table 27-8. Device ID

Part

Signature Bytes Address

0x000 0x001 0x002

ATmega48 0x1E 0x92 0x05

ATmega88 0x1E 0x93 0x0A

ATmega168 0x1E 0x94 0x06