231

2545M–AVR–09/07

ATmega48/88/168

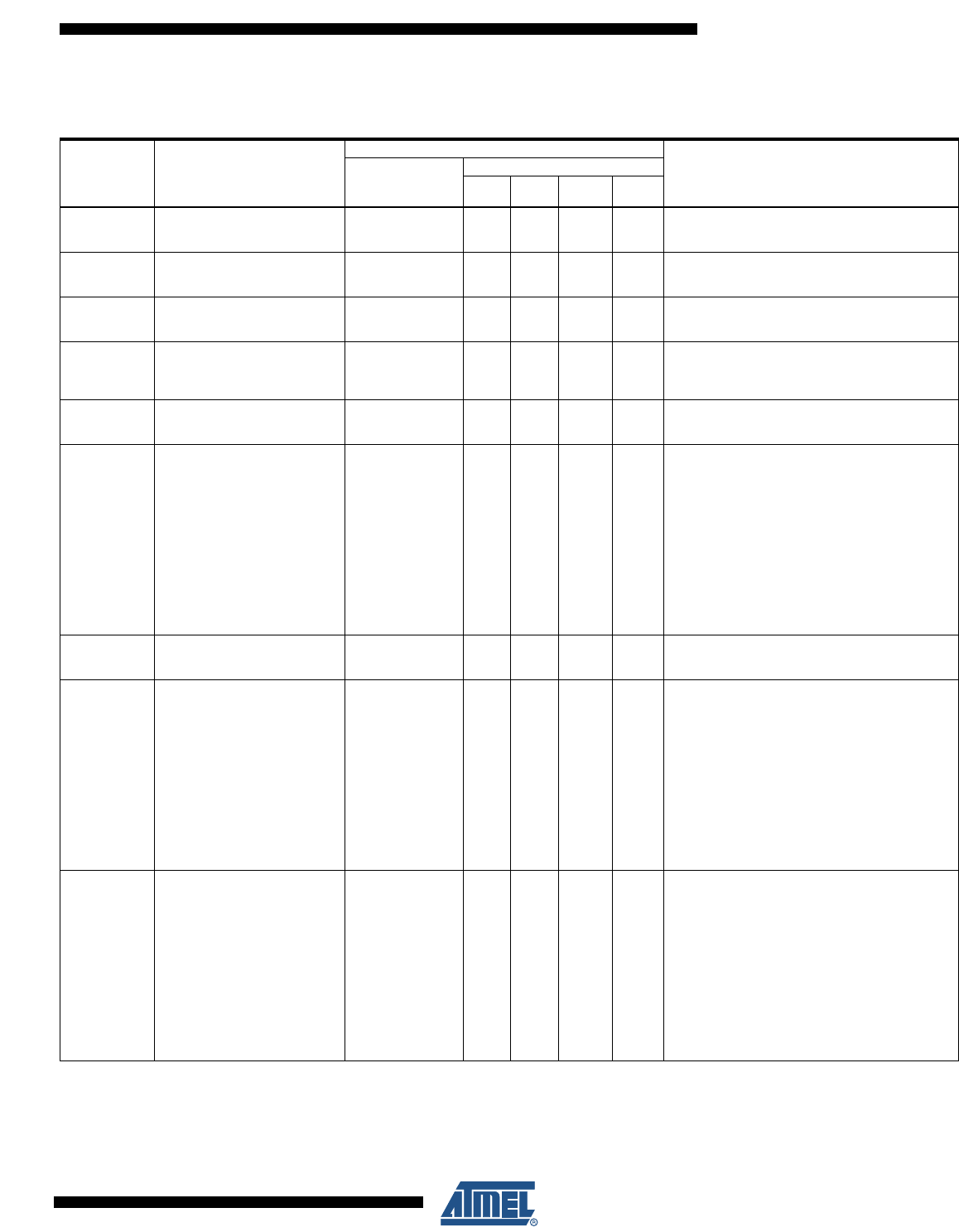

Table 21-4. Status Codes for Slave Receiver Mode

Status Code

(TWSR)

Prescaler Bits

are 0

Status of the 2-wire Serial Bus

and 2-wire Serial Interface Hard-

ware

Application Software Response

Next Action Taken by TWI Hardware

To/from TWDR

To TWCR

STA STO TWIN

T

TWE

A

0x60 Own SLA+W has been received;

ACK has been returned

No TWDR action or

No TWDR action

X

X

0

0

1

1

0

1

Data byte will be received and NOT ACK will be

returned

Data byte will be received and ACK will be returned

0x68 Arbitration lost in SLA+R/W as

Master; own SLA+W has been

received; ACK has been returned

No TWDR action or

No TWDR action

X

X

0

0

1

1

0

1

Data byte will be received and NOT ACK will be

returned

Data byte will be received and ACK will be returned

0x70 General call address has been

received; ACK has been returned

No TWDR action or

No TWDR action

X

X

0

0

1

1

0

1

Data byte will be received and NOT ACK will be

returned

Data byte will be received and ACK will be returned

0x78 Arbitration lost in SLA+R/W as

Master; General call address has

been received; ACK has been

returned

No TWDR action or

No TWDR action

X

X

0

0

1

1

0

1

Data byte will be received and NOT ACK will be

returned

Data byte will be received and ACK will be returned

0x80 Previously addressed with own

SLA+W; data has been received;

ACK has been returned

Read data byte or

Read data byte

X

X

0

0

1

1

0

1

Data byte will be received and NOT ACK will be

returned

Data byte will be received and ACK will be returned

0x88 Previously addressed with own

SLA+W; data has been received;

NOT ACK has been returned

Read data byte or

Read data byte or

Read data byte or

Read data byte

0

0

1

1

0

0

0

0

1

1

1

1

0

1

0

1

Switched to the not addressed Slave mode;

no recognition of own SLA or GCA

Switched to the not addressed Slave mode;

own SLA will be recognized;

GCA will be recognized if TWGCE = “1”

Switched to the not addressed Slave mode;

no recognition of own SLA or GCA;

a START condition will be transmitted when the bus

becomes free

Switched to the not addressed Slave mode;

own SLA will be recognized;

GCA will be recognized if TWGCE = “1”;

a START condition will be transmitted when the bus

becomes free

0x90 Previously addressed with

general call; data has been re-

ceived; ACK has been returned

Read data byte or

Read data byte

X

X

0

0

1

1

0

1

Data byte will be received and NOT ACK will be

returned

Data byte will be received and ACK will be returned

0x98 Previously addressed with

general call; data has been

received; NOT ACK has been

returned

Read data byte or

Read data byte or

Read data byte or

Read data byte

0

0

1

1

0

0

0

0

1

1

1

1

0

1

0

1

Switched to the not addressed Slave mode;

no recognition of own SLA or GCA

Switched to the not addressed Slave mode;

own SLA will be recognized;

GCA will be recognized if TWGCE = “1”

Switched to the not addressed Slave mode;

no recognition of own SLA or GCA;

a START condition will be transmitted when the bus

becomes free

Switched to the not addressed Slave mode;

own SLA will be recognized;

GCA will be recognized if TWGCE = “1”;

a START condition will be transmitted when the bus

becomes free

0xA0 A STOP condition or repeated

START condition has been

received while still addressed as

Slave

No action 0

0

1

1

0

0

0

0

1

1

1

1

0

1

0

1

Switched to the not addressed Slave mode;

no recognition of own SLA or GCA

Switched to the not addressed Slave mode;

own SLA will be recognized;

GCA will be recognized if TWGCE = “1”

Switched to the not addressed Slave mode;

no recognition of own SLA or GCA;

a START condition will be transmitted when the bus

becomes free

Switched to the not addressed Slave mode;

own SLA will be recognized;

GCA will be recognized if TWGCE = “1”;

a START condition will be transmitted when the bus

becomes free