228

2545M–AVR–09/07

the Master to switch between Slaves, Master Transmitter mode and Master Receiver mode with-

out losing control over the bus.

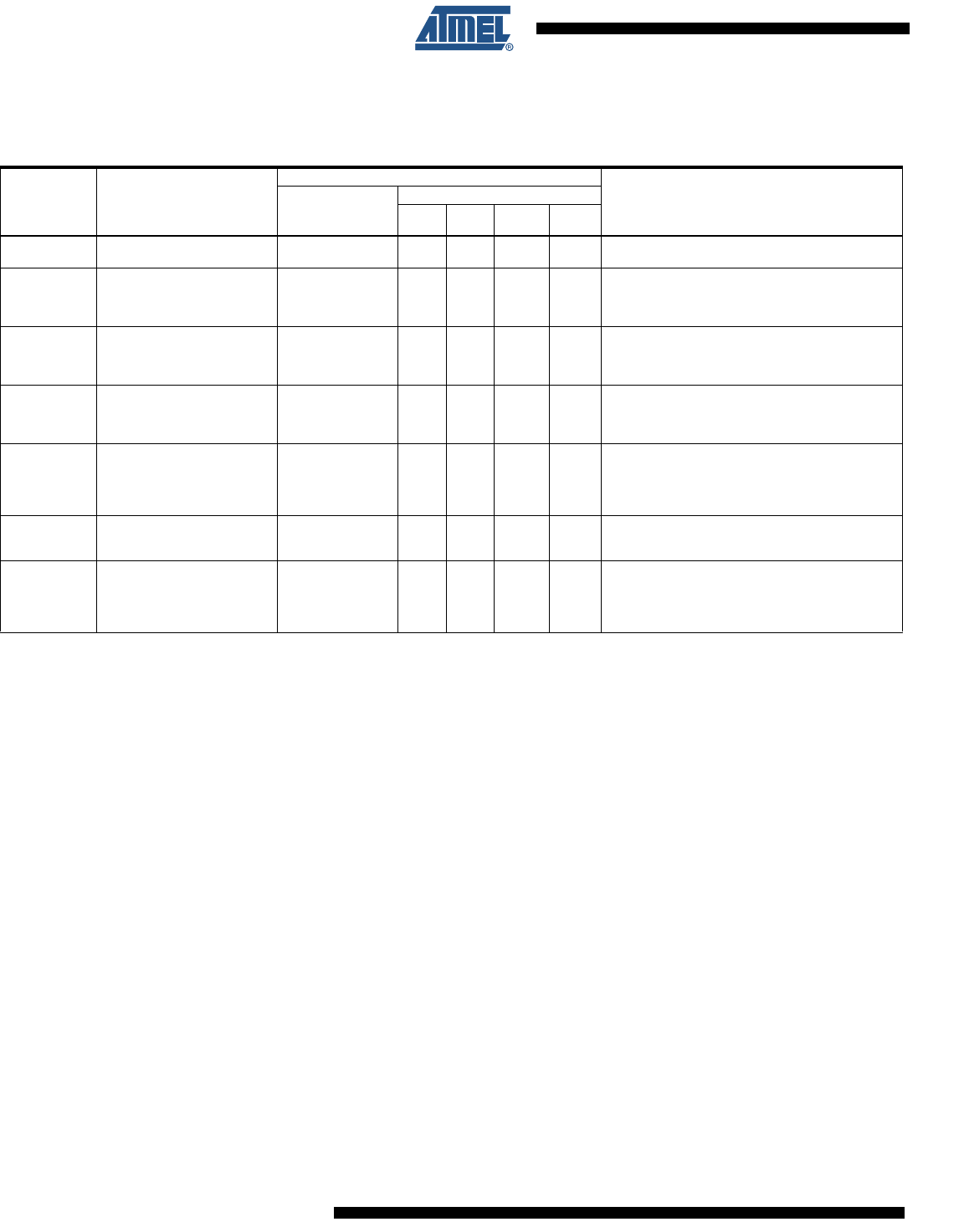

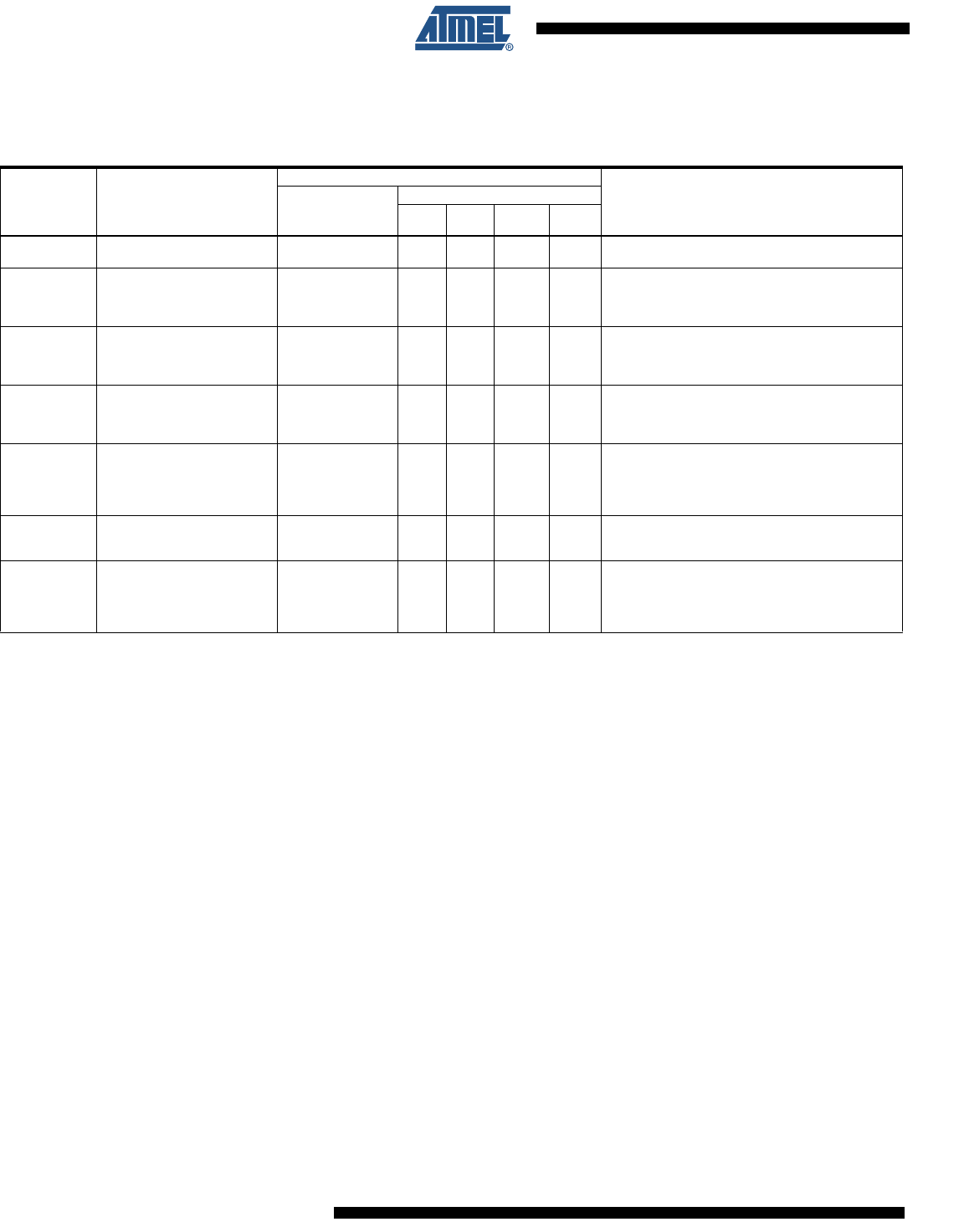

Table 21-3. Status codes for Master Receiver Mode

Status Code

(TWSR)

Prescaler Bits

are 0

Status of the 2-wire Serial Bus

and 2-wire Serial Interface

Hardware

Application Software Response

Next Action Taken by TWI Hardware

To/from TWDR

To TWCR

STA STO TWIN

T

TWE

A

0x08 A START condition has been

transmitted

Load SLA+R 0 0 1 X SLA+R will be transmitted

ACK or NOT ACK will be received

0x10 A repeated START condition

has been transmitted

Load SLA+R or

Load SLA+W

0

0

0

0

1

1

X

X

SLA+R will be transmitted

ACK or NOT ACK will be received

SLA+W will be transmitted

Logic will switch to Master Transmitter mode

0x38 Arbitration lost in SLA+R or

NOT ACK bit

No TWDR action or

No TWDR action

0

1

0

0

1

1

X

X

2-wire Serial Bus will be released and not addressed

Slave mode will be entered

A START condition will be transmitted when the bus

becomes free

0x40 SLA+R has been transmitted;

ACK has been received

No TWDR action or

No TWDR action

0

0

0

0

1

1

0

1

Data byte will be received and NOT ACK will be

returned

Data byte will be received and ACK will be returned

0x48 SLA+R has been transmitted;

NOT ACK has been received

No TWDR action or

No TWDR action or

No TWDR action

1

0

1

0

1

1

1

1

1

X

X

X

Repeated START will be transmitted

STOP condition will be transmitted and TWSTO Flag

will be reset

STOP condition followed by a START condition will be

transmitted and TWSTO Flag will be reset

0x50 Data byte has been received;

ACK has been returned

Read data byte or

Read data byte

0

0

0

0

1

1

0

1

Data byte will be received and NOT ACK will be

returned

Data byte will be received and ACK will be returned

0x58 Data byte has been received;

NOT ACK has been returned

Read data byte or

Read data byte or

Read data byte

1

0

1

0

1

1

1

1

1

X

X

X

Repeated START will be transmitted

STOP condition will be transmitted and TWSTO Flag

will be reset

STOP condition followed by a START condition will be

transmitted and TWSTO Flag will be reset