212

2545M–AVR–09/07

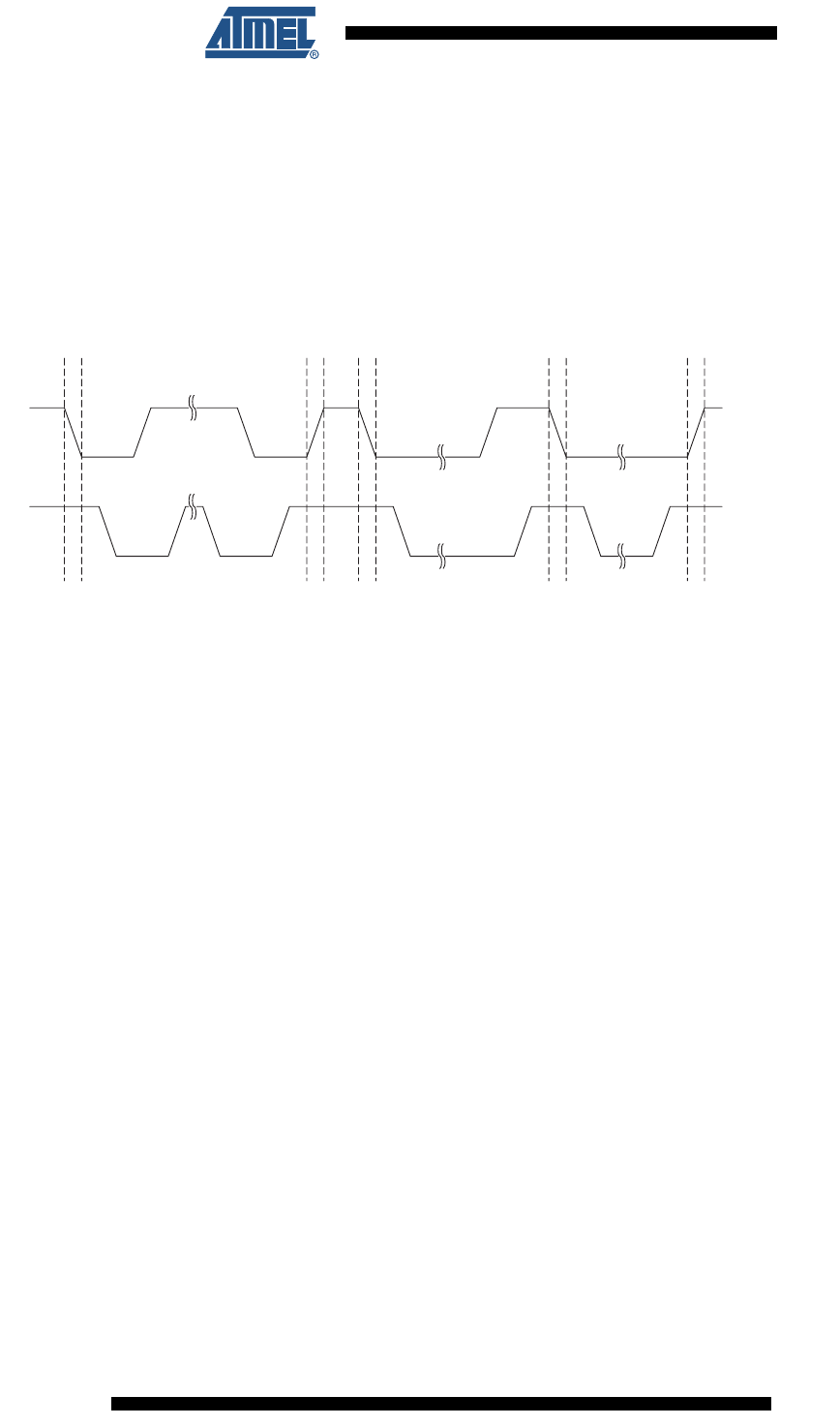

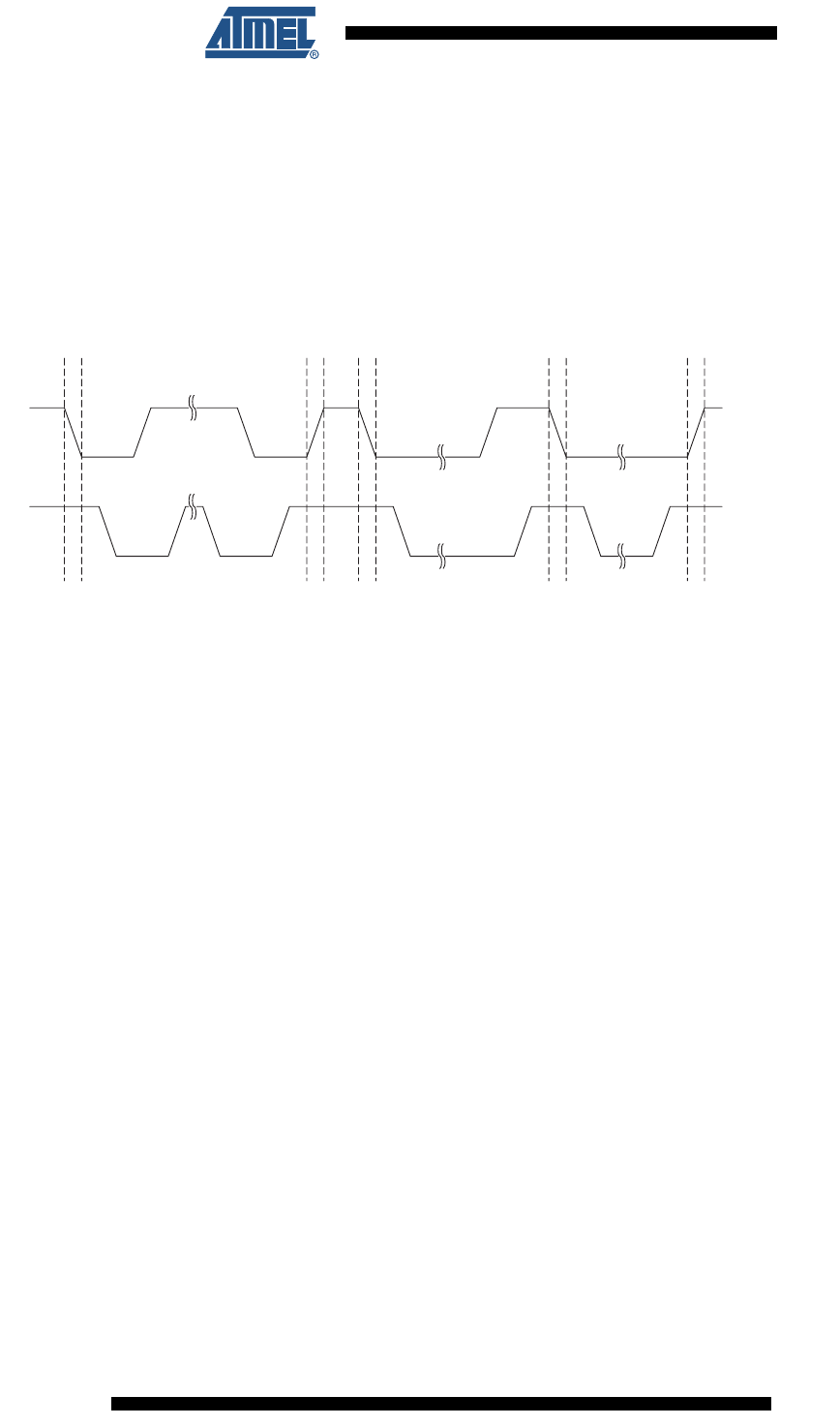

other master should try to seize control of the bus. A special case occurs when a new START

condition is issued between a START and STOP condition. This is referred to as a REPEATED

START condition, and is used when the Master wishes to initiate a new transfer without relin-

quishing control of the bus. After a REPEATED START, the bus is considered busy until the next

STOP. This is identical to the START behavior, and therefore START is used to describe both

START and REPEATED START for the remainder of this datasheet, unless otherwise noted. As

depicted below, START and STOP conditions are signalled by changing the level of the SDA

line when the SCL line is high.

Figure 21-3. START, REPEATED START and STOP conditions

21.3.3 Address Packet Format

All address packets transmitted on the TWI bus are 9 bits long, consisting of 7 address bits, one

READ/WRITE control bit and an acknowledge bit. If the READ/WRITE bit is set, a read opera-

tion is to be performed, otherwise a write operation should be performed. When a Slave

recognizes that it is being addressed, it should acknowledge by pulling SDA low in the ninth SCL

(ACK) cycle. If the addressed Slave is busy, or for some other reason can not service the Mas-

ter’s request, the SDA line should be left high in the ACK clock cycle. The Master can then

transmit a STOP condition, or a REPEATED START condition to initiate a new transmission. An

address packet consisting of a slave address and a READ or a WRITE bit is called SLA+R or

SLA+W, respectively.

The MSB of the address byte is transmitted first. Slave addresses can freely be allocated by the

designer, but the address 0000 000 is reserved for a general call.

When a general call is issued, all slaves should respond by pulling the SDA line low in the ACK

cycle. A general call is used when a Master wishes to transmit the same message to several

slaves in the system. When the general call address followed by a Write bit is transmitted on the

bus, all slaves set up to acknowledge the general call will pull the SDA line low in the ack cycle.

The following data packets will then be received by all the slaves that acknowledged the general

call. Note that transmitting the general call address followed by a Read bit is meaningless, as

this would cause contention if several slaves started transmitting different data.

All addresses of the format 1111 xxx should be reserved for future purposes.

SDA

SCL

START STOPREPEATED START

STOP START