53

AT84AD001B

2153C–BDC–04/04

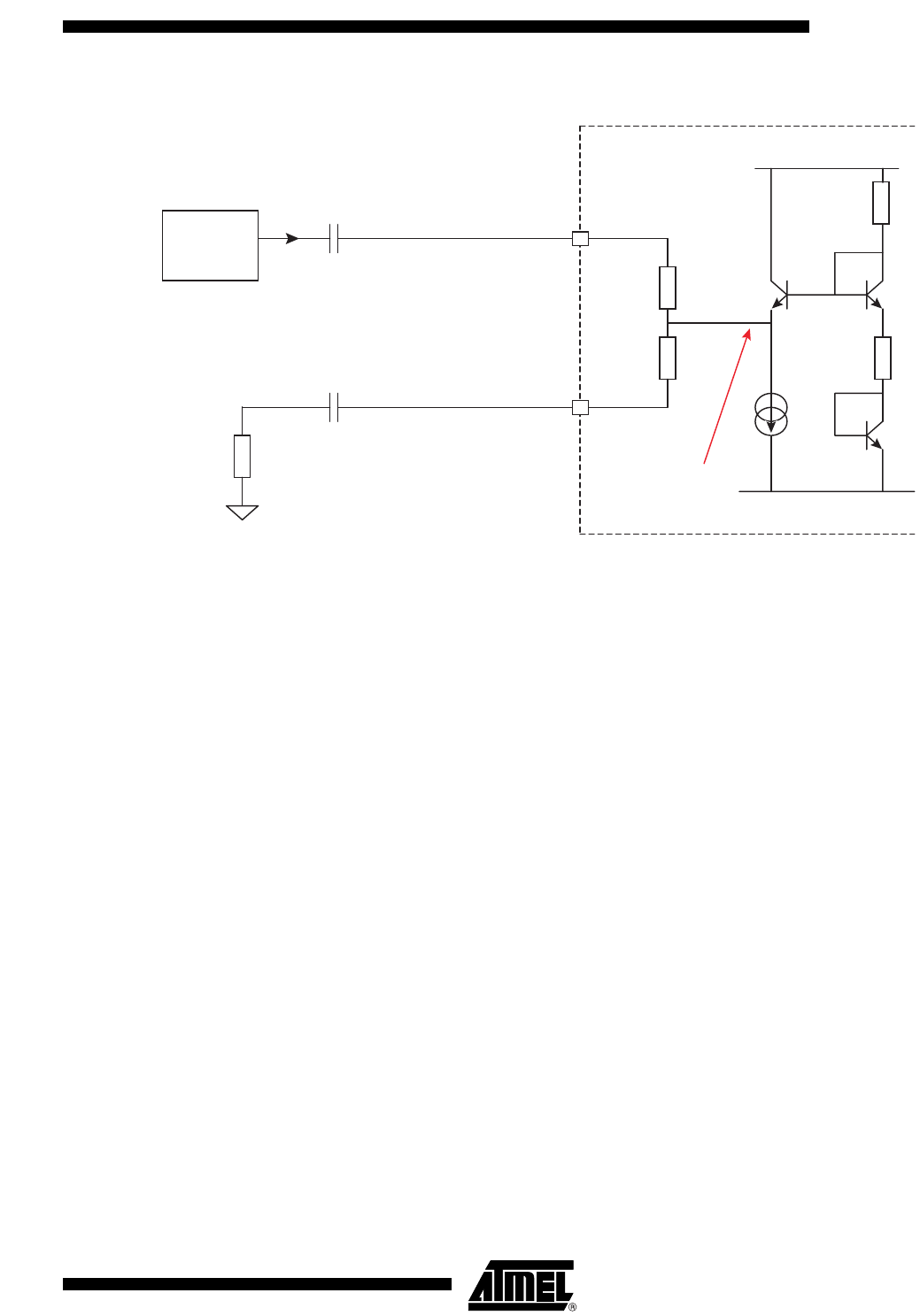

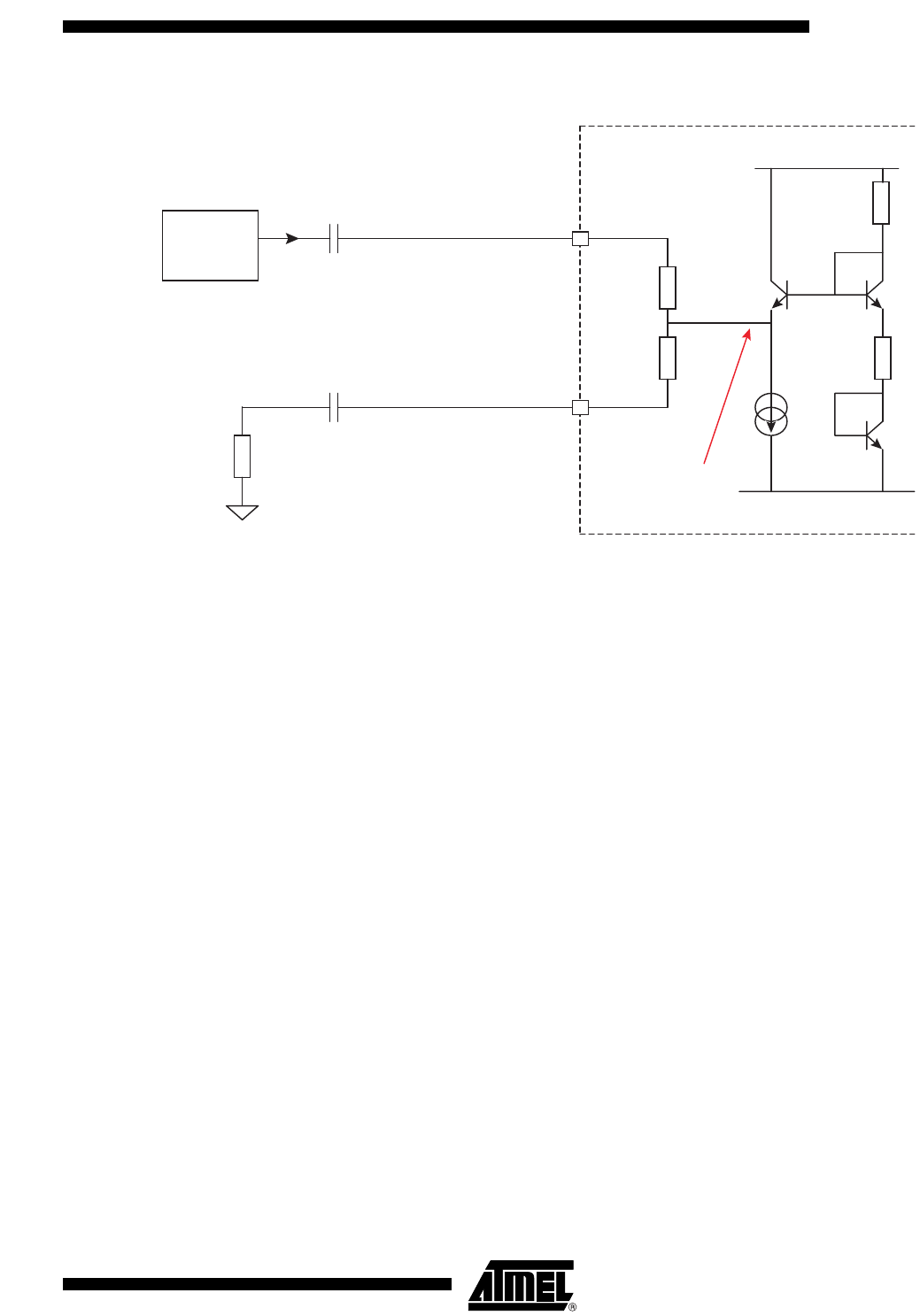

Figure 59. Single-ended Termination Method for Clock I or Clock Q

Output Termination in

1:1 Ratio

When using the integrated DMUX in 1:1 ratio, the valid port is port A. Port B remains

unused.

Port A functions in LVDS mode and the corresponding outputs (DOAI or DOAQ) have to

be 100Ω differentially terminated as shown in Figure 60 on page 54.

The pins corresponding to Port B (DOBI or DOBQ pins) must be left floating (in high

impedance state).

Figure 60 shows the example of a 1:1 ratio of the integrated DMUX for channel I (the

same applies to channel Q).

CLK

CLKB

50Ω

50Ω

VCCD

R1

R2

VCCD/2

AC coupling capacitor

AC coupling capacitor

50Ω

Source

50Ω