50

AT84AD001B

2153C–BDC–04/04

Using the AT84AD001B Dual 8-bit 1 Gsps ADC

Decoupling, Bypassing

and Grounding of Power

Supplies

The following figures show the recommended bypassing, decoupling and grounding

schemes for the dual 8-bit 1 Gsps ADC power supplies.

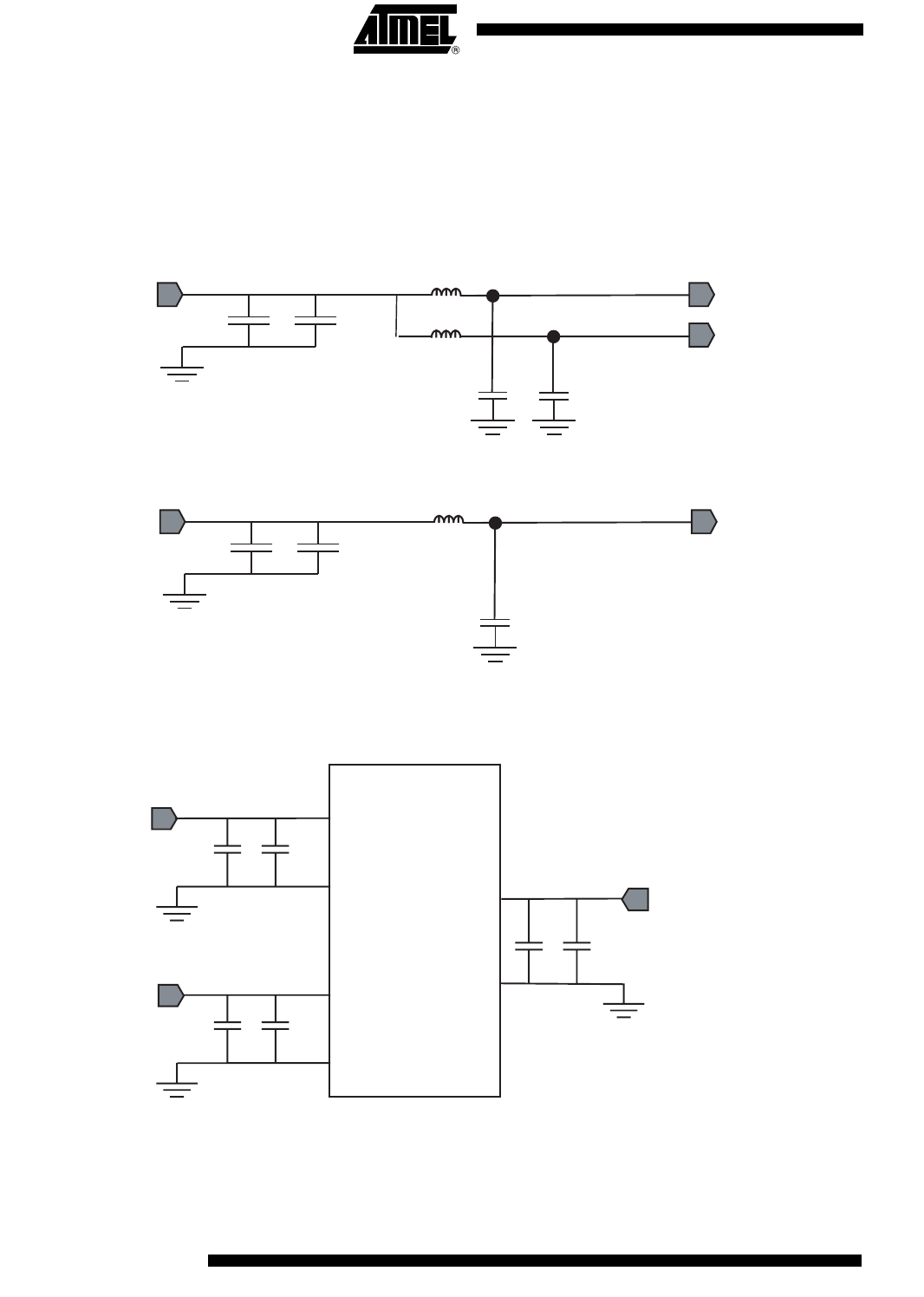

Figure 53. V

CCD

and V

CCA

Bypassing and Grounding Scheme

Figure 54. V

CCO

Bypassing and Grounding Scheme

Note: L and C values must be chosen in accordance with the operation frequency of the application.

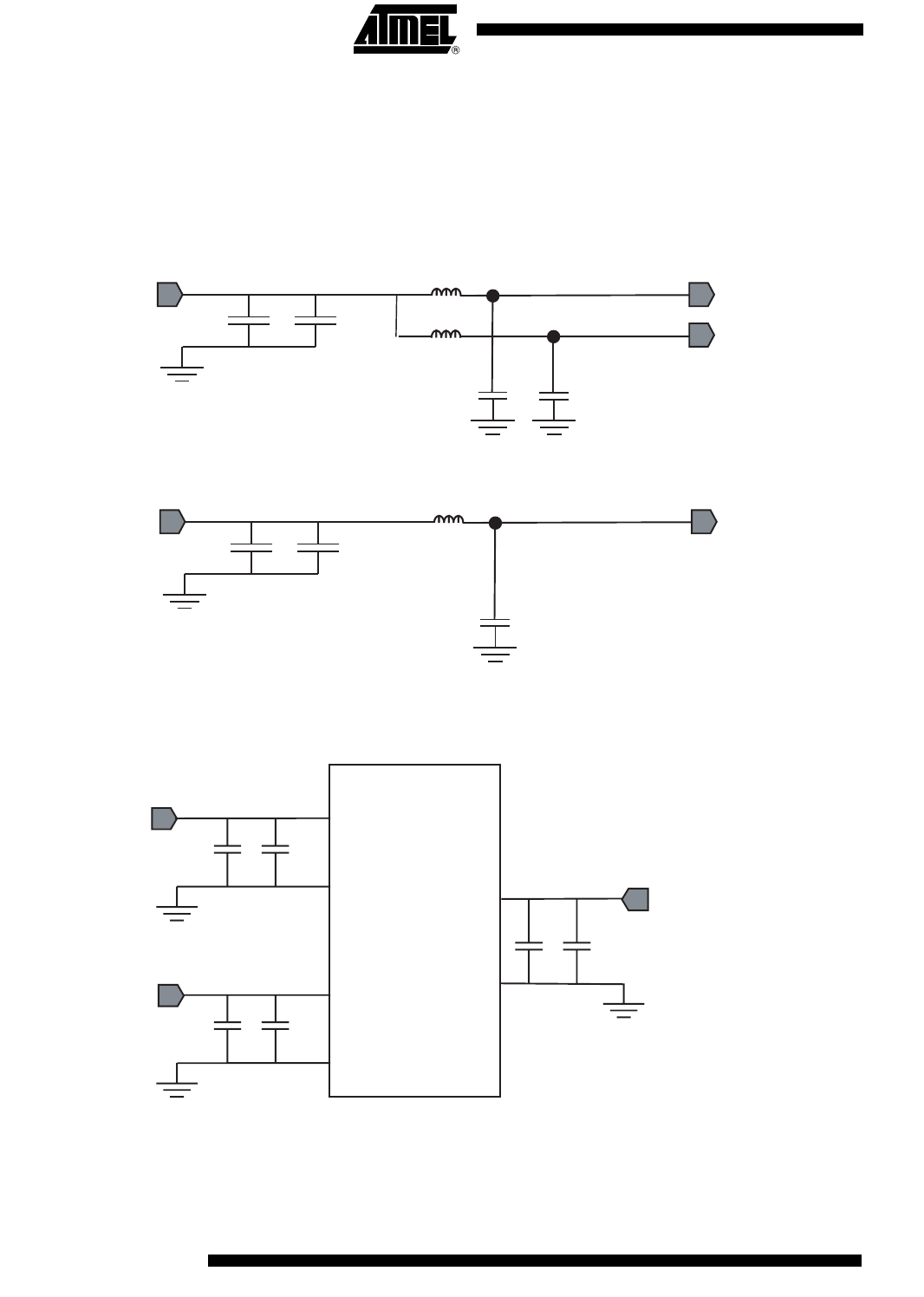

Figure 55. Power Supplies Decoupling Scheme

Note: The bypassing capacitors (1 µF and 100 pF) should be placed as close as possible to the board connectors, whereas the

decoupling capacitors (100 pF and 10 nF) should be placed as close as possible to the device.

1µF

L

PC Board 3.3V

PC Board GND

VCCD

L

C

C

VCCA

100 pF

1µF

L

PC Board 2.25V

PC Board GND

VCCO

C

100 pF

VCCA

GNDA

VCCO

GNDO

GNDA

GNDD

GNDO

VCCD

VCCA

VCCO

100 pF

100 pF 10 nF

10 nF

100 pF

10 nF