43

AT84AD001B

2153C–BDC–04/04

The calibration phase is necessary when using the AT84AD001B in interlace mode,

where one analog input is sampled at both ADC cores on the common input clock’s ris

-

ing and falling edges. This operation is equivalent to converting the analog signal at

twice the clock frequency

During the ADC’s auto-calibration phase, the dual ADC is set with the following:

• Decimation mode ON

• 1:1 DMUX mode

• Binary mode

Any external action applied to any signal of the ADC’s registers is inhibited during the

calibration phase.

Gain and Offset

Compensation Functions

It is also possible for the user to have external access to the ADC’s gain and offset com-

pensation functions:

• Offset compensation between I and Q channels (at address 010)

• Gain compensation between I and Q channels (at address 011)

To obtain manual access to these two functions, which are used to set the offset to mid-

dle code 127.5 and to match the gain of channel Q with that of channel I (if only one

channel is used, the gain compensation does not apply), it is necessary to set the ADC

to “manual” mode by writing 0 at bits D11 and D10 of address 000.

Built-In Test (BIT) A Built-In Test (BIT) function is available to allow rapid testing of the device’s I/O by

either applying a defined static pattern to the ADC or by generating a dynamic ramp at

the ADC’s output. The dynamic ramp can be used with a clock frequency of up to

750 Msps. This function is controlled via the 3-wire bus interface at address 101.

• The BIT is active when Data0 = 1 at address 110.

• The BIT is inactive when Data0 = 0 at address 110.

• The Data1 bit allows choosing between static mode (Data1 = 0) and dynamic mode

(Data1 = 1).

When the static BIT is selected (Data1 = 0), it is possible to write any 8-bit pattern by

defining the Data9 to Data2 bits. Port B then outputs an 8-bit pattern equal to Data9 ...

Data2, and Port A outputs an 8-bit pattern equal to NOT (Data9 ... Data2).

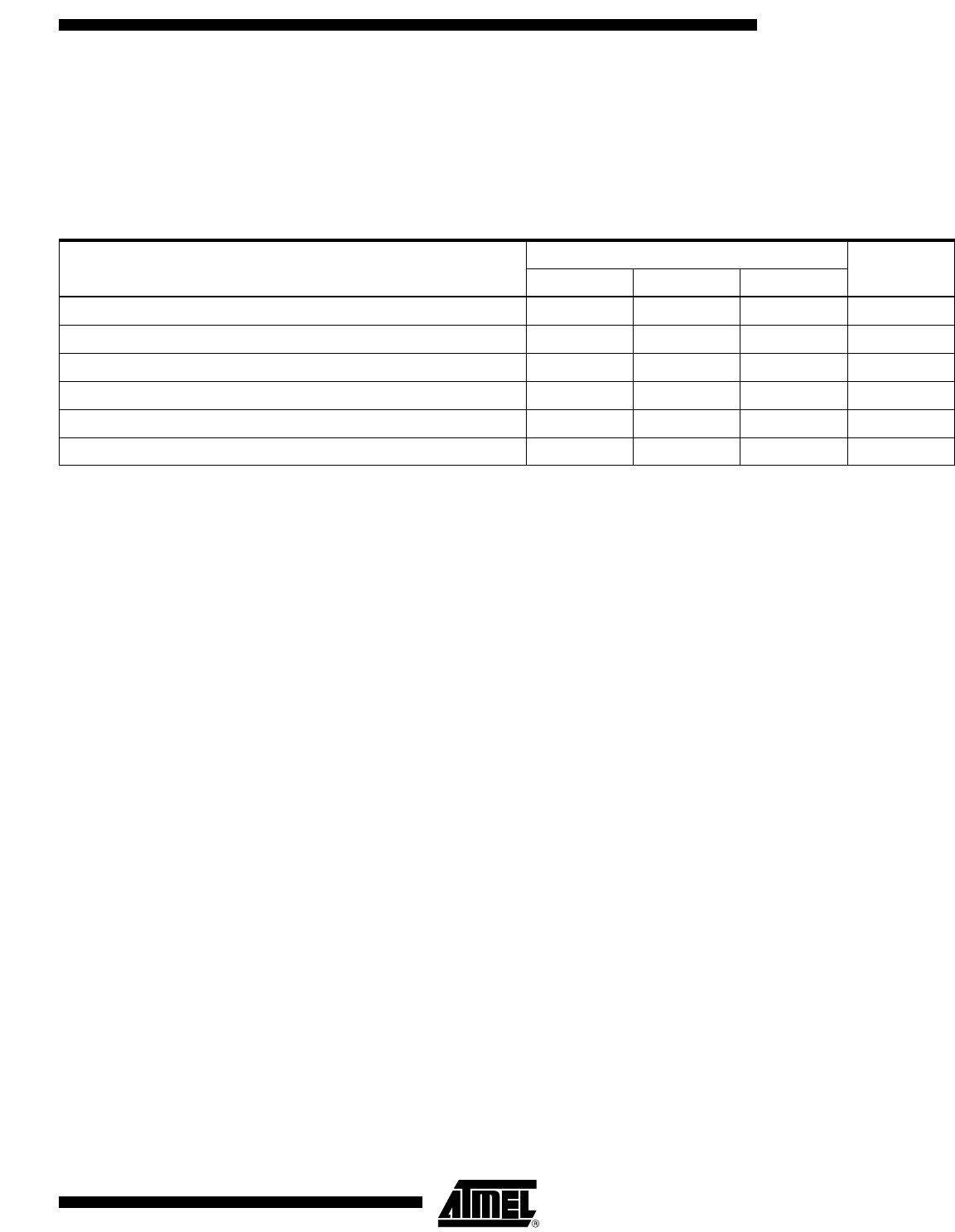

Table 15. Matching Between Channels

Parameter

Value

UnitMin Typ Max

Gain error (single channel I or Q) without calibration 0 LSB

Gain error (single channel I or Q) with calibration -0.5 0 0.5 LSB

Offset error (single channel I or Q) without calibration 0 LSB

Offset error (single channel I or Q) with calibration -0.5 0 0.5 LSB

Mean offset code without calibration (single channel I or Q) 127.5

Mean offset code with calibration (single channel I or Q) 127 127.5 128