ProASIC3 DC and Switching Characteristics

2-14 v1.3

Guidelines

Toggle Rate Definition

A toggle rate defines the frequency of a net or logic element relative to a clock. It is a percentage.

If the toggle rate of a net is 100%, this means that this net switches at half the clock frequency.

Below are some examples:

• The average toggle rate of a shift register is 100% because all flip-flop outputs toggle at

half of the clock frequency.

• The average toggle rate of an 8-bit counter is 25%:

– Bit 0 (LSB) = 100%

– Bit 1 = 50%

– Bit 2 = 25%

–…

– Bit 7 (MSB) = 0.78125%

– Average toggle rate = (100% + 50% + 25% + 12.5% + . . . + 0.78125%) / 8

Enable Rate Definition

Output enable rate is the average percentage of time during which tristate outputs are enabled.

When nontristate output buffers are used, the enable rate should be 100%.

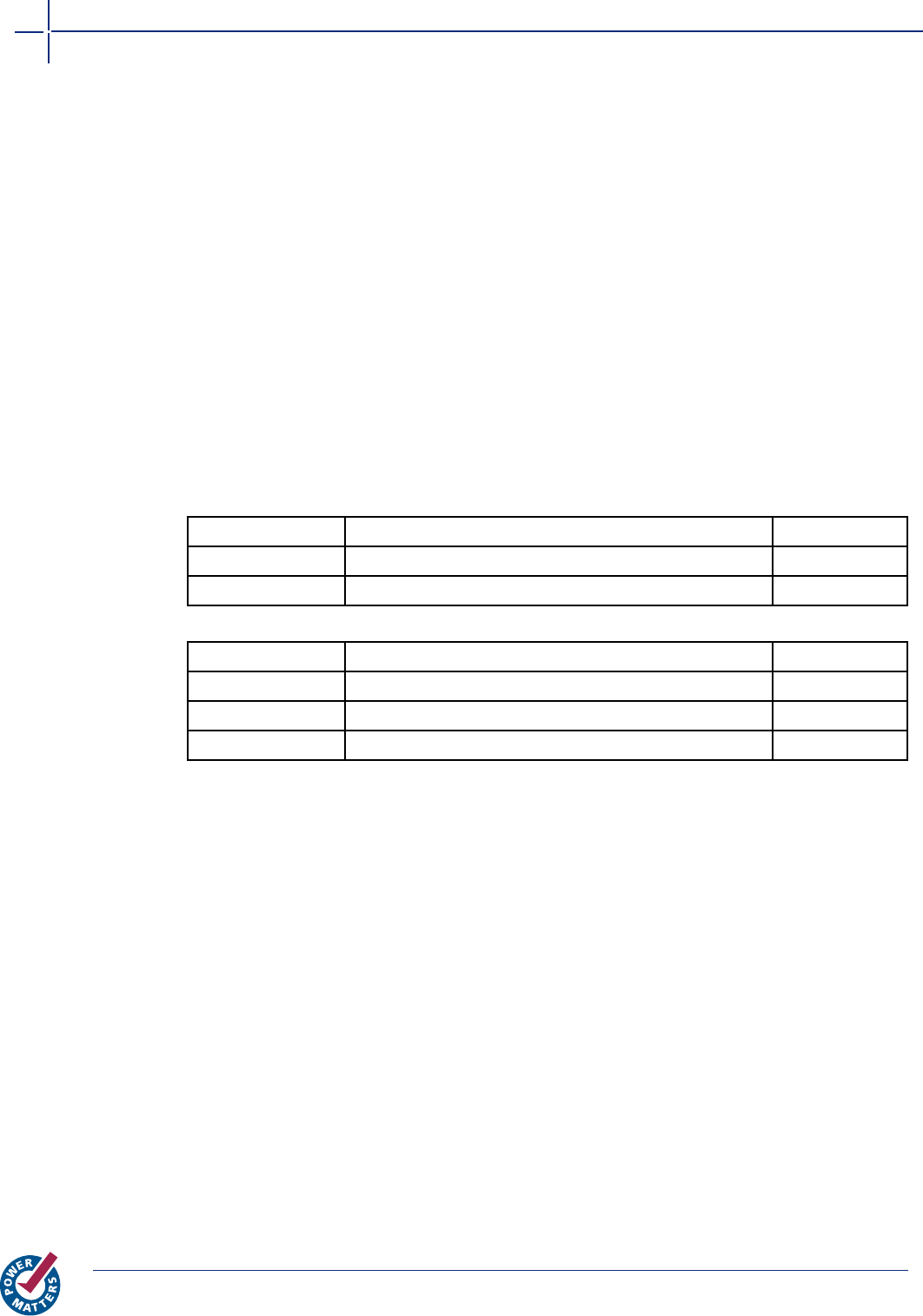

Table 2-16 • Toggle Rate Guidelines Recommended for Power Calculation

Component Definition Guideline

α

1

Toggle rate of VersaTile outputs 10%

α

2

I/O buffer toggle rate 10%

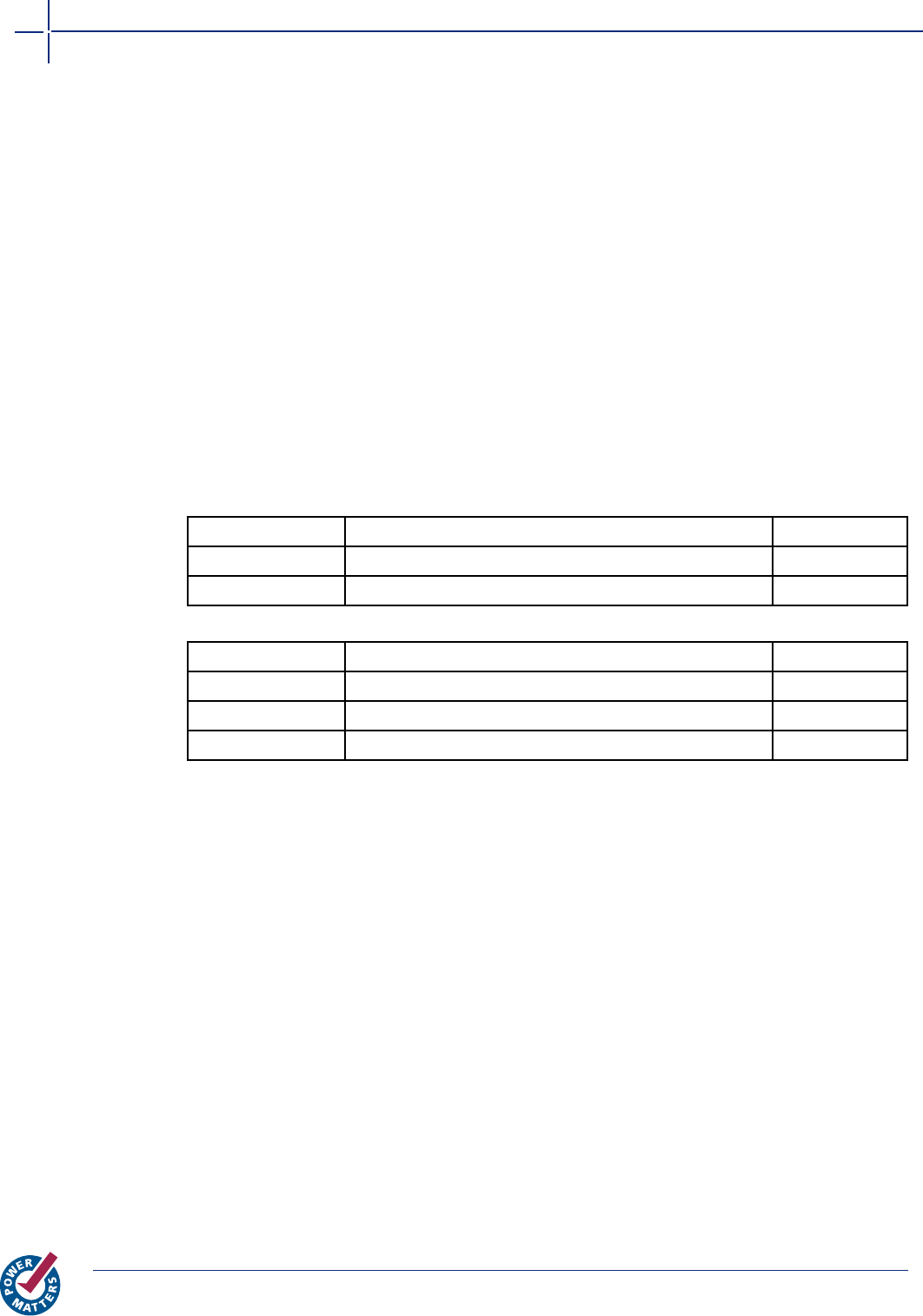

Table 2-17 • Enable Rate Guidelines Recommended for Power Calculation

Component Definition Guideline

β

1

I/O output buffer enable rate 100%

β

2

RAM enable rate for read operations 12.5%

β

3

RAM enable rate for write operations 12.5%