ProASIC3 DC and Switching Characteristics

2-104 v1.3

Part Number and Revision Date

Part Number 51700097-002-3

Revised August 2008

List of Changes

The following table lists critical changes that were made in the current version of the chapter.

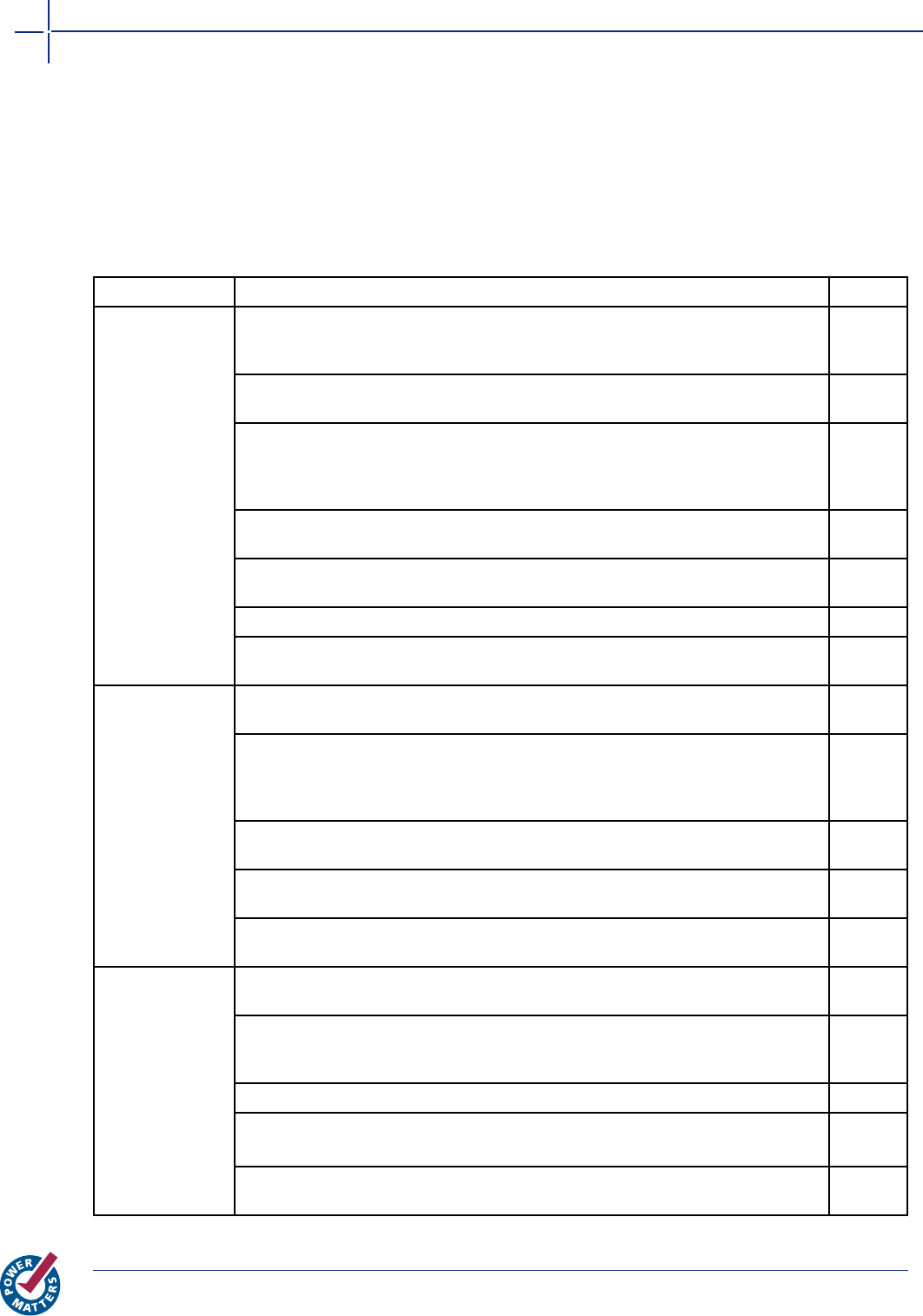

Previous Version Changes in Current Version (v1.3) Page

v1.2

(June 2008)

TJ, Maximum Junction Temperature, was changed to 100° from 110º in the

"Thermal Characteristics" section and EQ 2-2. The calculated result of Maximum

Power Allowed has thus changed to 1.463 W from 1.951 W.

2-5

Values for the A3P015 device were added to Table 2-7 · Quiescent Supply

Current Characteristics.

2-6

Values for the A3P015 device were added to Table 2-14 · Different Components

Contributing to Dynamic Power Consumption in ProASIC3 Devices. P

AC14

was

removed. Table 2-15 · Different Components Contributing to the Static Power

Consumption in ProASIC3 Devices is new.

2-10,

2-11

The "PLL Contribution—PPLL" section was updated to change the P

PLL

formula

from P

AC13

+ P

AC14

* F

CLKOUT

to P

DC4

+ P

AC13

* F

CLKOUT

.

2-13

Both fall and rise values were included for t

DDRISUD

and t

DDRIHD

in

Table 2-93 · Input DDR Propagation Delays.

2-71

Table 2-98 · A3P015 Global Resource is new. 2-79

The typical value for Delay Increments in Programmable Delay Blocks was

changed from 160 to 200 in Table 2-106 · ProASIC3 CCC/PLL Specification.

2-83

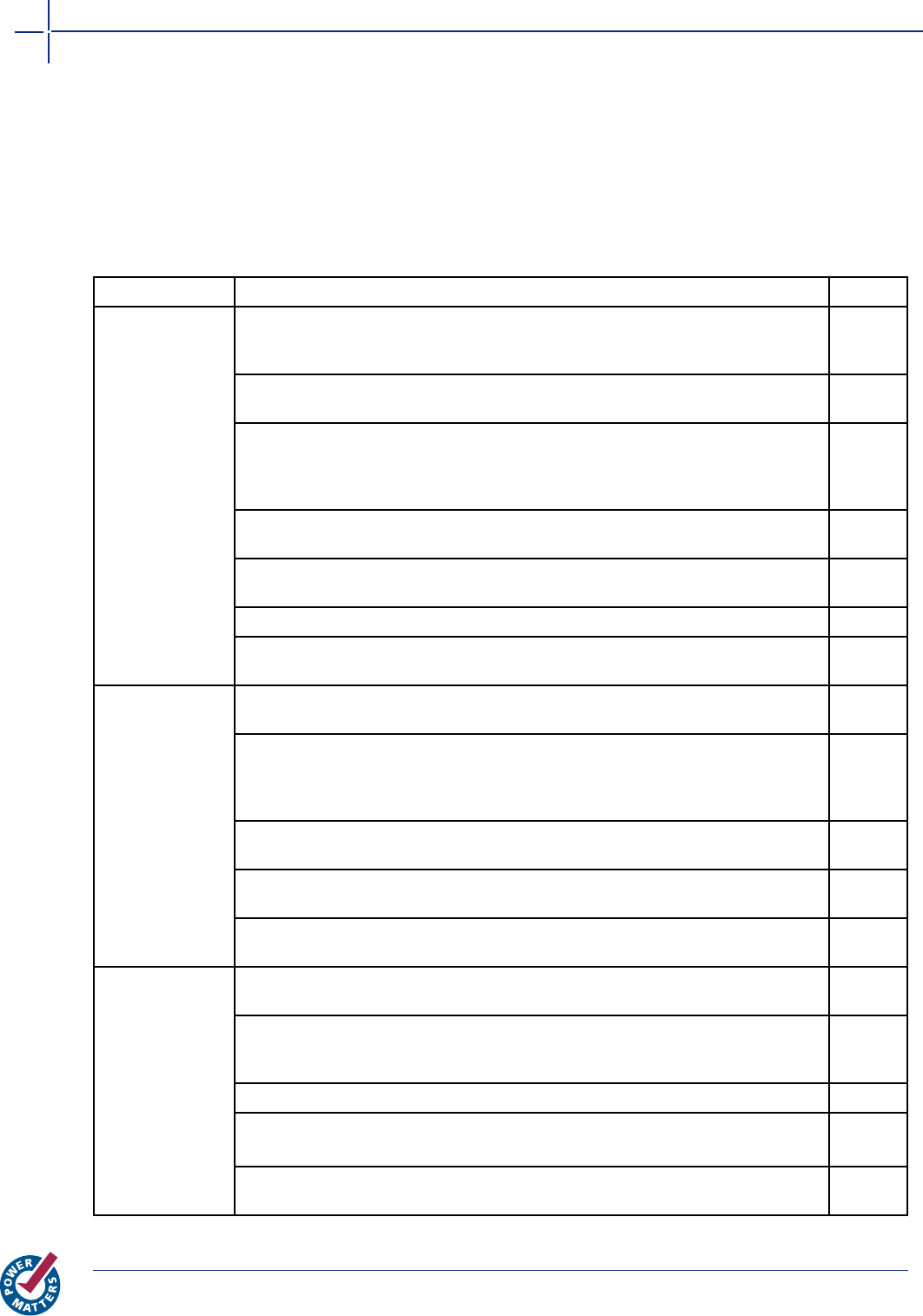

v1.1

(January 2008)

Table note references were added to Table 2-2 · Recommended Operating

Conditions

1

, and the order of the table notes was changed.

2-2

The title for Table 2-4 · Overshoot and Undershoot Limits

1

was modified to

remove "as measured on quiet I/Os." Table note 1 was revised to remove

"estimated SSO density over cycles." Table note 2 was revised to remove "refers

only to overshoot/undershoot limits for simultaneous switching I/Os.

"

2-3

The "Power per I/O Pin" section was updated to include 3 additional tables

pertaining to input buffer power and output buffer power.

2-6

Table 2-29 · I/O Output Buffer Maximum Resistances

1

was revised to include

values for 3.3 V PCI/PCI-X.

2-24

Table 2-81 · LVDS Minimum and Maximum DC Input and Output Levels was

updated.

2-59

v1.0

(January 2008)

In Table 2-2 · Recommended Operating Conditions

1

, T

J

was listed in the symbol

column and was incorrect. It was corrected and changed to T

A

.

2-2

In Table 2-3 · Flash Programming Limits – Retention, Storage and Operating

Temperature1, Maximum Operating Junction Temperature was changed from

110°C to 100°C for both commercial and industrial grades.

2-2

The "PLL Behavior at Brownout Condition" section is new. 2-3

In the "PLL Contribution—PPLL" section, the following was deleted:

FCLKIN is the input clock frequency.

2-13

In Table 2-21 · Summary of Maximum and Minimum DC Input Levels, the note

was incorrect. It previously said T

J

and it was corrected and changed to T

A

.

2-20