ProASIC3 DC and Switching Characteristics

2-96 v1.3

Timing Characteristics

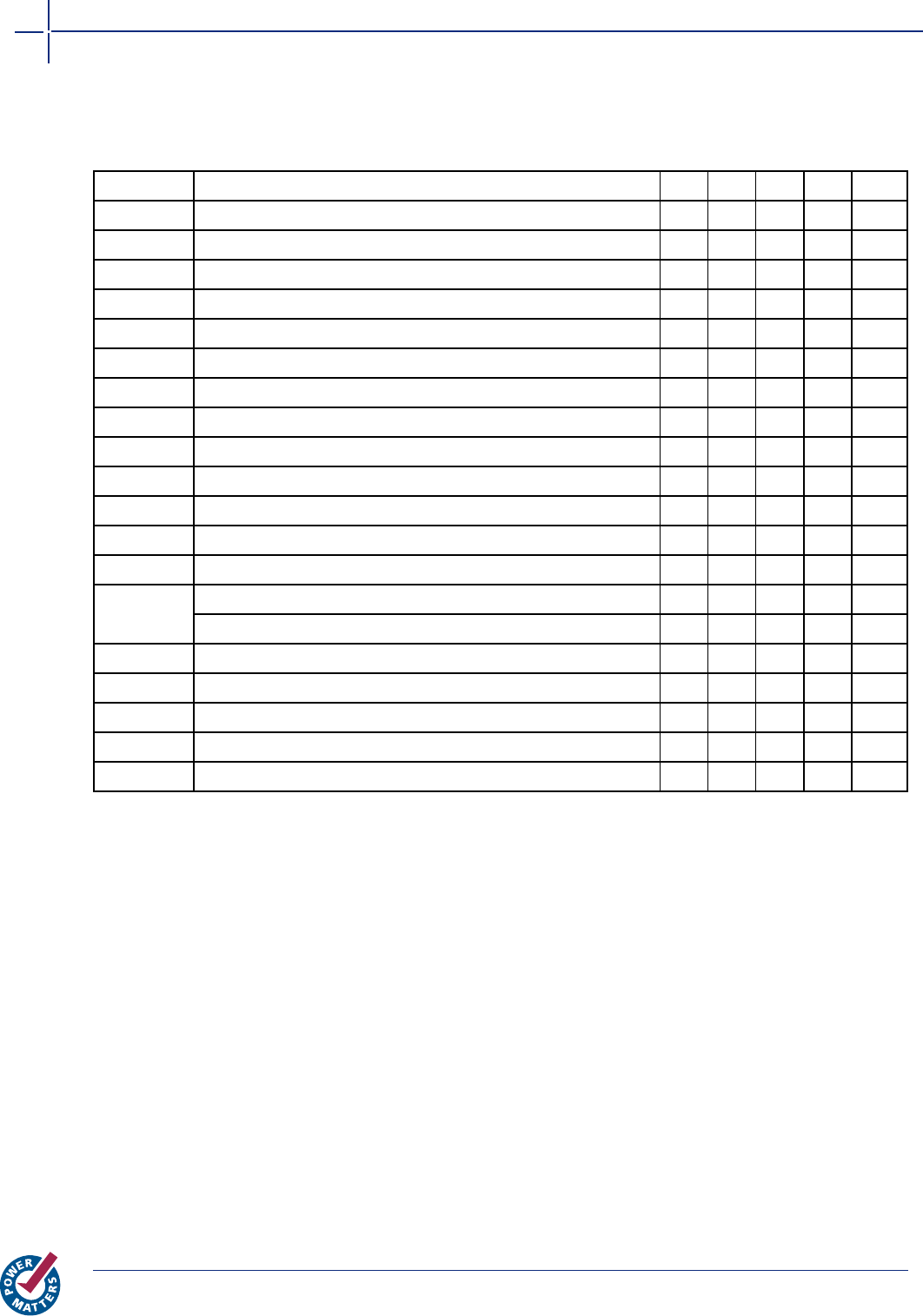

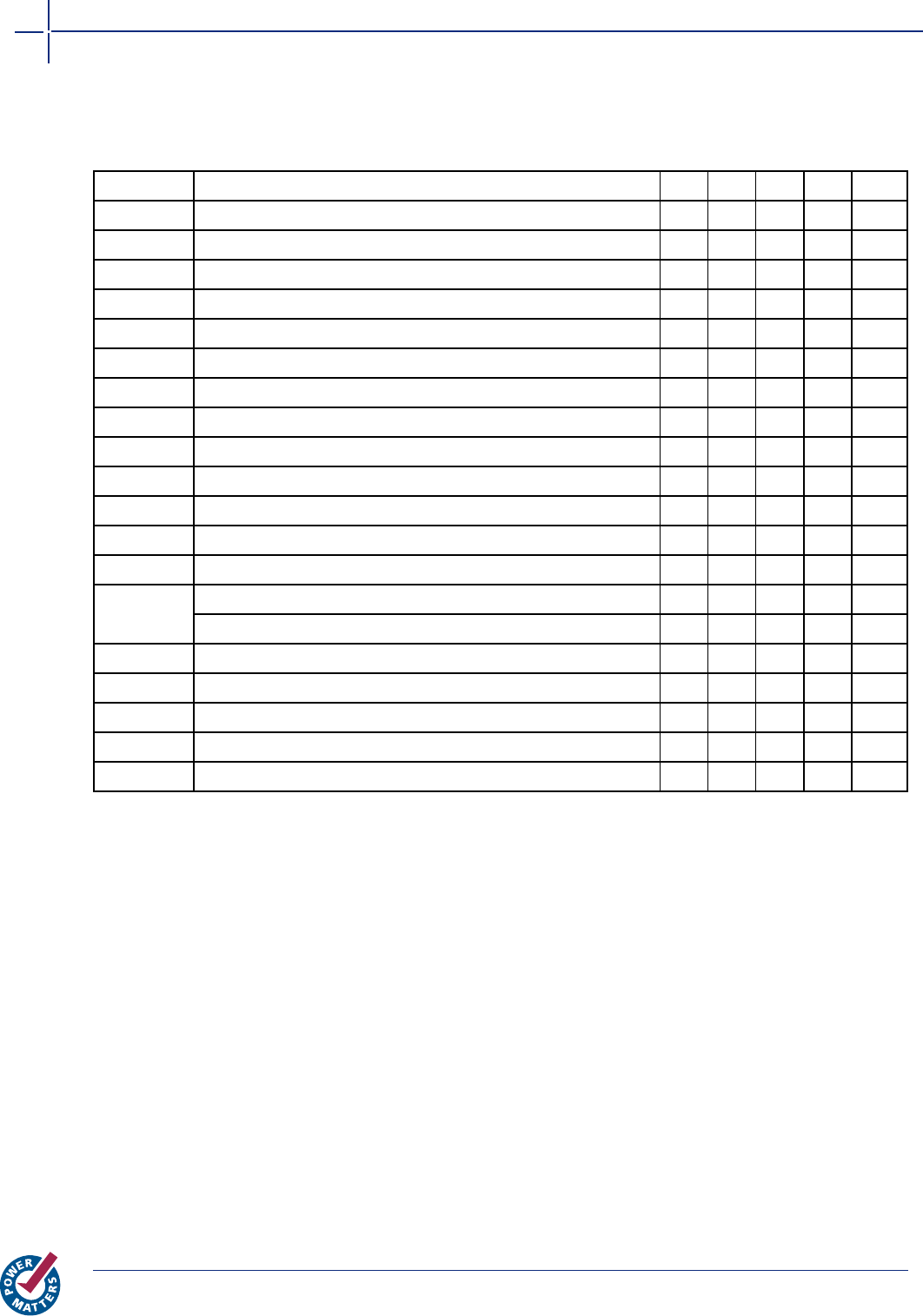

Table 2-109 • FIFO (for all dies except A3P250)

Worst Commercial-Case Conditions: T

J

= 70°C, V

CC

= 1.425 V

Parameter Description –2 –1 Std. –F Units

t

ENS

REN_B, WEN_B Setup Time 1.34 1.52 1.79 2.15 ns

t

ENH

REN_B, WEN_B Hold Time 0.00 0.00 0.00 0.00 ns

t

BKS

BLK_B Setup Time 0.19 0.22 0.26 0.31 ns

t

BKH

BLK_B Hold Time 0.00 0.00 0.00 0.00 ns

t

DS

Input Data (DI) Setup Time 0.18 0.21 0.25 0.29 ns

t

DH

Input Data (DI) Hold Time 0.00 0.00 0.00 0.00 ns

t

CKQ1

Clock HIGH to New Data Valid on DO (flow-through) 2.17 2.47 2.90 3.48 ns

t

CKQ2

Clock HIGH to New Data Valid on DO (pipelined) 0.94 1.07 1.26 1.52 ns

t

RCKEF

RCLK HIGH to Empty Flag Valid 1.72 1.96 2.30 2.76 ns

t

WCKFF

WCLK HIGH to Full Flag Valid 1.63 1.86 2.18 2.62 ns

t

CKAF

Clock HIGH to Almost Empty/Full Flag Valid 6.19 7.05 8.29 9.96 ns

t

RSTFG

RESET_B LOW to Empty/Full Flag Valid 1.69 1.93 2.27 2.72 ns

t

RSTAF

RESET_B LOW to Almost Empty/Full Flag Valid 6.13 6.98 8.20 9.85 ns

t

RSTBQ

RESET_B LOW to Data Out LOW on DO (flow-through) 0.921.051.231.48 ns

RESET_B LOW to Data Out LOW on DO (pipelined) 0.92 1.05 1.23 1.48 ns

t

REMRSTB

RESET_B Removal 0.29 0.33 0.38 0.46 ns

t

RECRSTB

RESET_B Recovery 1.50 1.71 2.01 2.41 ns

t

MPWRSTB

RESET_B Minimum Pulse Width 0.21 0.24 0.29 0.34 ns

t

CYC

Clock Cycle Time 3.23 3.68 4.32 5.19 ns

F

MAX

Maximum Frequency for FIFO 310 272 231 193 MHz

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating

values.