ProASIC3 DC and Switching Characteristics

2-82 v1.3

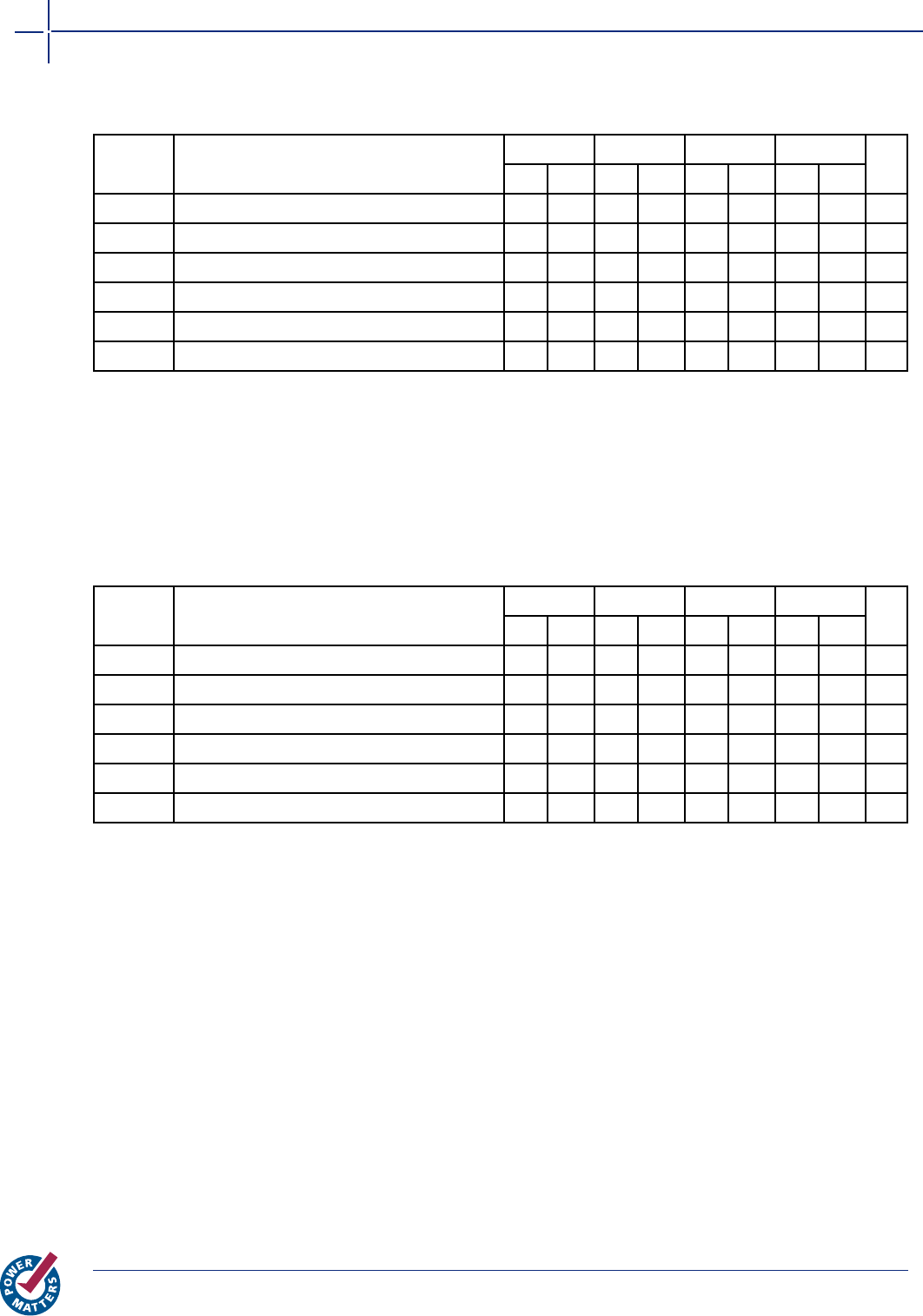

Table 2-104 • A3P600 Global Resource

Commercial-Case Conditions: T

J

= 70°C, V

CC

= 1.425 V

Parameter Description

–2 –1 Std. –F

UnitsMin.

1

Max.

2

Min.

1

Max.

2

Min.

1

Max.

2

Min.

1

Max.

2

t

RCKL

Input LOW Delay for Global Clock 0.87 1.09 0.99 1.24 1.17 1.46 1.40 1.75 ns

t

RCKH

Input HIGH Delay for Global Clock 0.861.110.981.271.151.491.381.79 ns

t

RCKMPWH

Minimum Pulse Width HIGH for Global Clock ns

t

RCKMPWL

Minimum Pulse Width LOW for Global Clock ns

t

RCKSW

Maximum Skew for Global Clock 0.26 0.29 0.34 0.41 ns

F

RMAX

Maximum Frequency for Global Clock MHz

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential

element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element,

located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating

values.

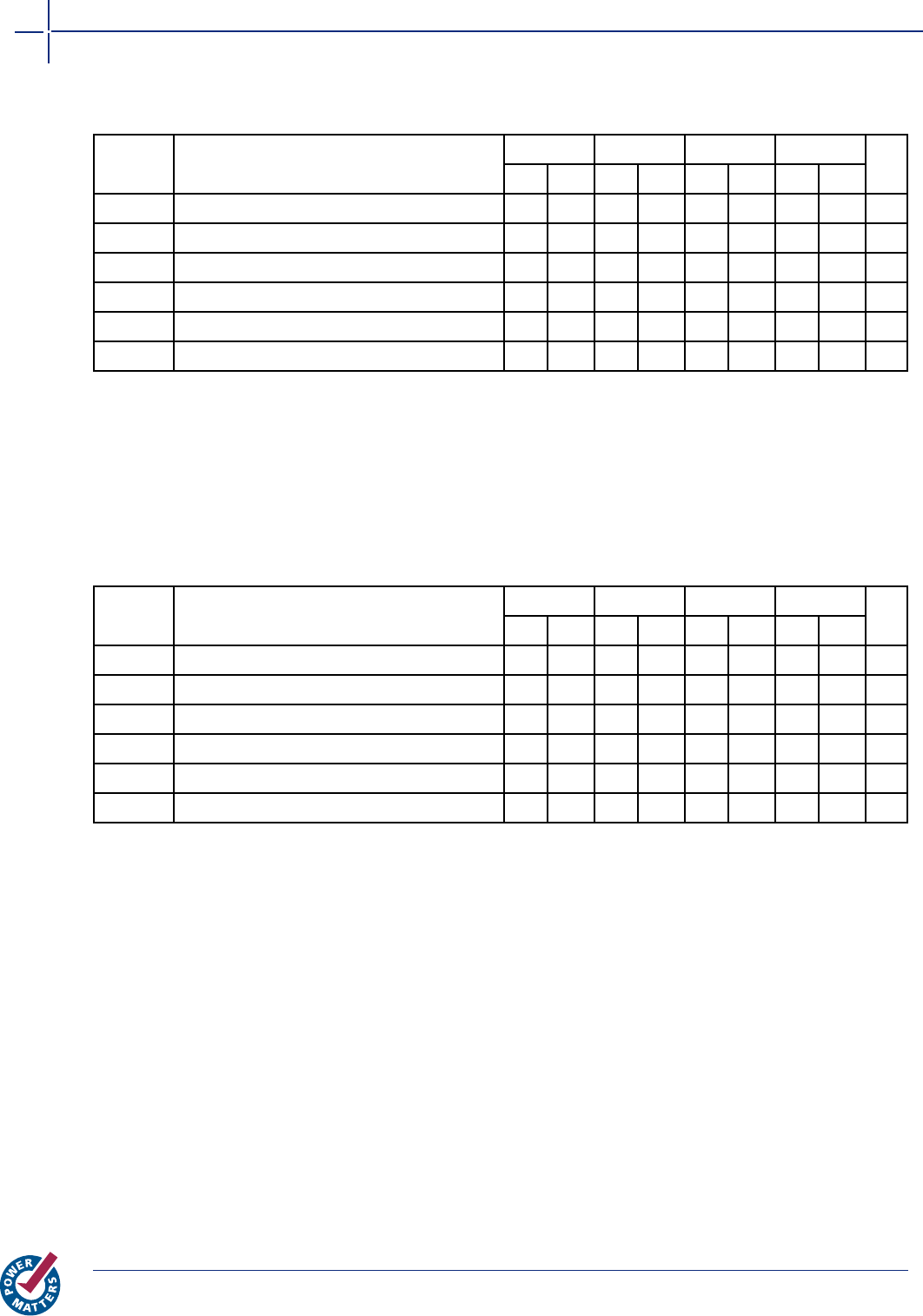

Table 2-105 • A3P1000 Global Resource

Commercial-Case Conditions: T

J

= 70°C, V

CC

= 1.425 V

Parameter Description

–2 –1 Std. –F

UnitsMin.

1

Max.

2

Min.

1

Max.

2

Min.

1

Max.

2

Min.

1

Max.

2

t

RCKL

Input LOW Delay for Global Clock 0.94 1.16 1.07 1.32 1.26 1.55 1.51 1.86 ns

t

RCKH

Input HIGH Delay for Global Clock 0.931.191.061.351.241.591.491.91 ns

t

RCKMPWH

Minimum Pulse Width HIGH for Global Clock ns

t

RCKMPWL

Minimum Pulse Width LOW for Global Clock ns

t

RCKSW

Maximum Skew for Global Clock 0.26 0.29 0.35 0.41 ns

F

RMAX

Maximum Frequency for Global Clock MHz

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential

element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element,

located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating

values.