ProASIC3 DC and Switching Characteristics

v1.3 2-69

Timing Characteristics

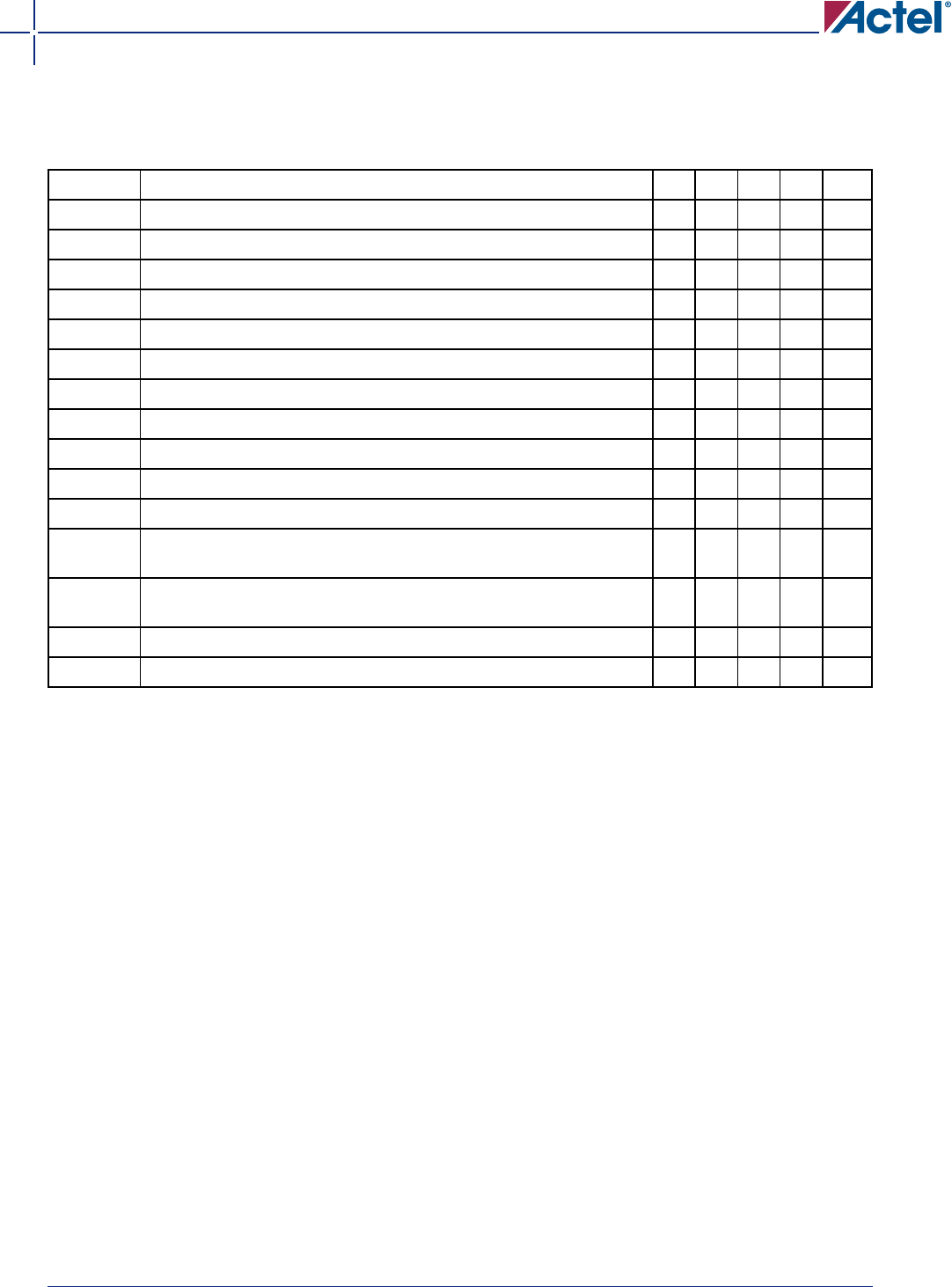

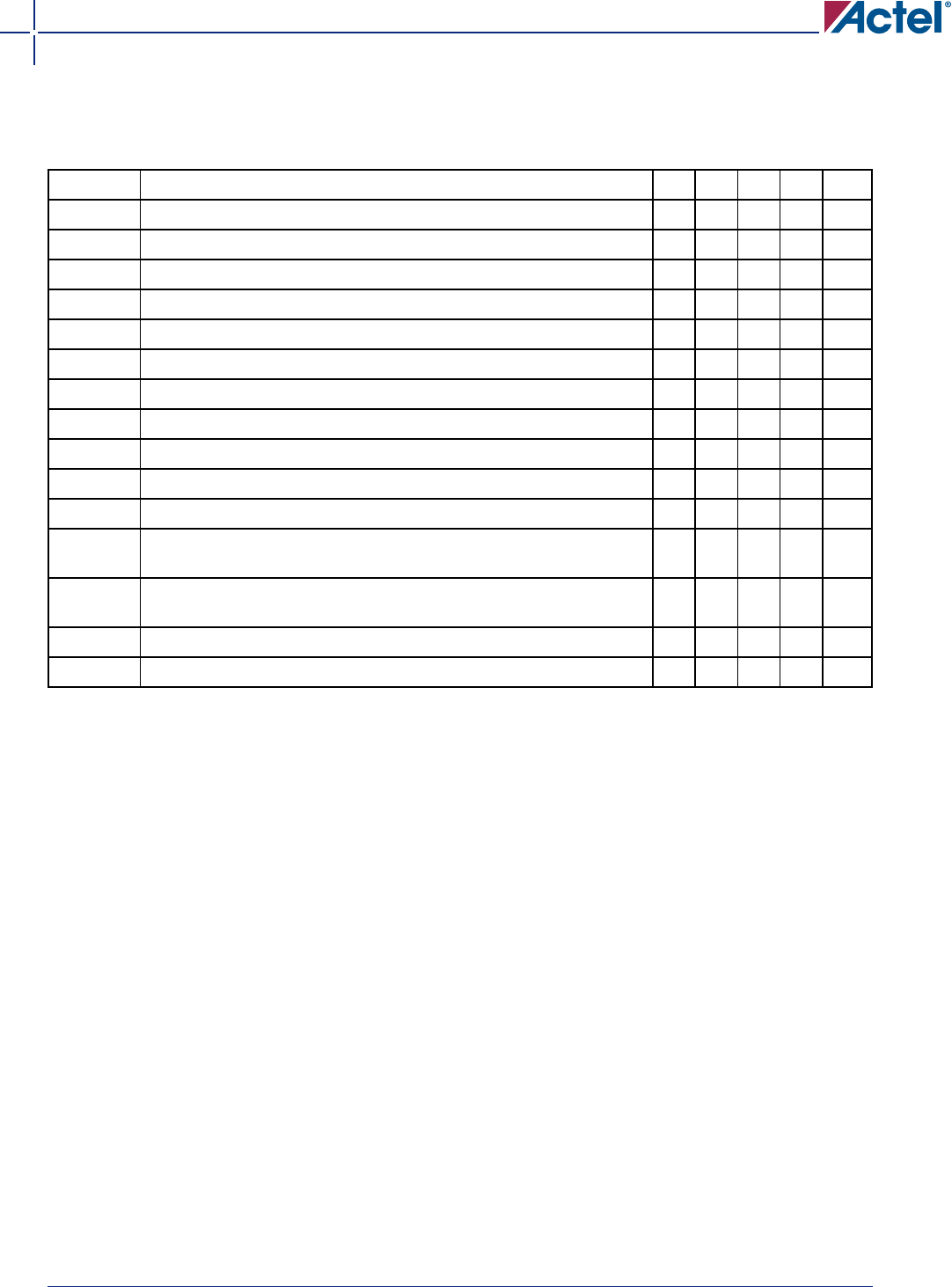

Table 2-91 • Output Enable Register Propagation Delays

Commercial-Case Conditions: T

J

= 70°C, Worst-Case V

CC

= 1.425 V

Parameter Description –2 –1 Std. –F Units

t

OECLKQ

Clock-to-Q of the Output Enable Register 0.59 0.67 0.79 0.95 ns

t

OESUD

Data Setup Time for the Output Enable Register 0.31 0.36 0.42 0.50 ns

t

OEHD

Data Hold Time for the Output Enable Register 0.00 0.00 0.00 0.00 ns

t

OESUE

Enable Setup Time for the Output Enable Register 0.44 0.50 0.58 0.70 ns

t

OEHE

Enable Hold Time for the Output Enable Register 0.00 0.00 0.00 0.00 ns

t

OECLR2Q

Asynchronous Clear-to-Q of the Output Enable Register 0.67 0.76 0.89 1.07 ns

t

OEPRE2Q

Asynchronous Preset-to-Q of the Output Enable Register 0.67 0.76 0.89 1.07 ns

t

OEREMCLR

Asynchronous Clear Removal Time for the Output Enable Register 0.00 0.00 0.00 0.00 ns

t

OERECCLR

Asynchronous Clear Recovery Time for the Output Enable Register 0.22 0.25 0.30 0.36 ns

t

OEREMPRE

Asynchronous Preset Removal Time for the Output Enable Register 0.00 0.00 0.00 0.00 ns

t

OERECPRE

Asynchronous Preset Recovery Time for the Output Enable Register 0.22 0.25 0.30 0.36 ns

t

OEWCLR

Asynchronous Clear Minimum Pulse Width for the Output Enable

Register

0.22 0.25 0.30 0.36 ns

t

OEWPRE

Asynchronous Preset Minimum Pulse Width for the Output Enable

Register

0.22 0.25 0.30 0.36 ns

t

OECKMPWH

Clock Minimum Pulse Width HIGH for the Output Enable Register 0.36 0.41 0.48 0.57 ns

t

OECKMPWL

Clock Minimum Pulse Width LOW for the Output Enable Register 0.32 0.37 0.43 0.52 ns

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating

values.