ProASIC3 DC and Switching Characteristics

v1.3 2-65

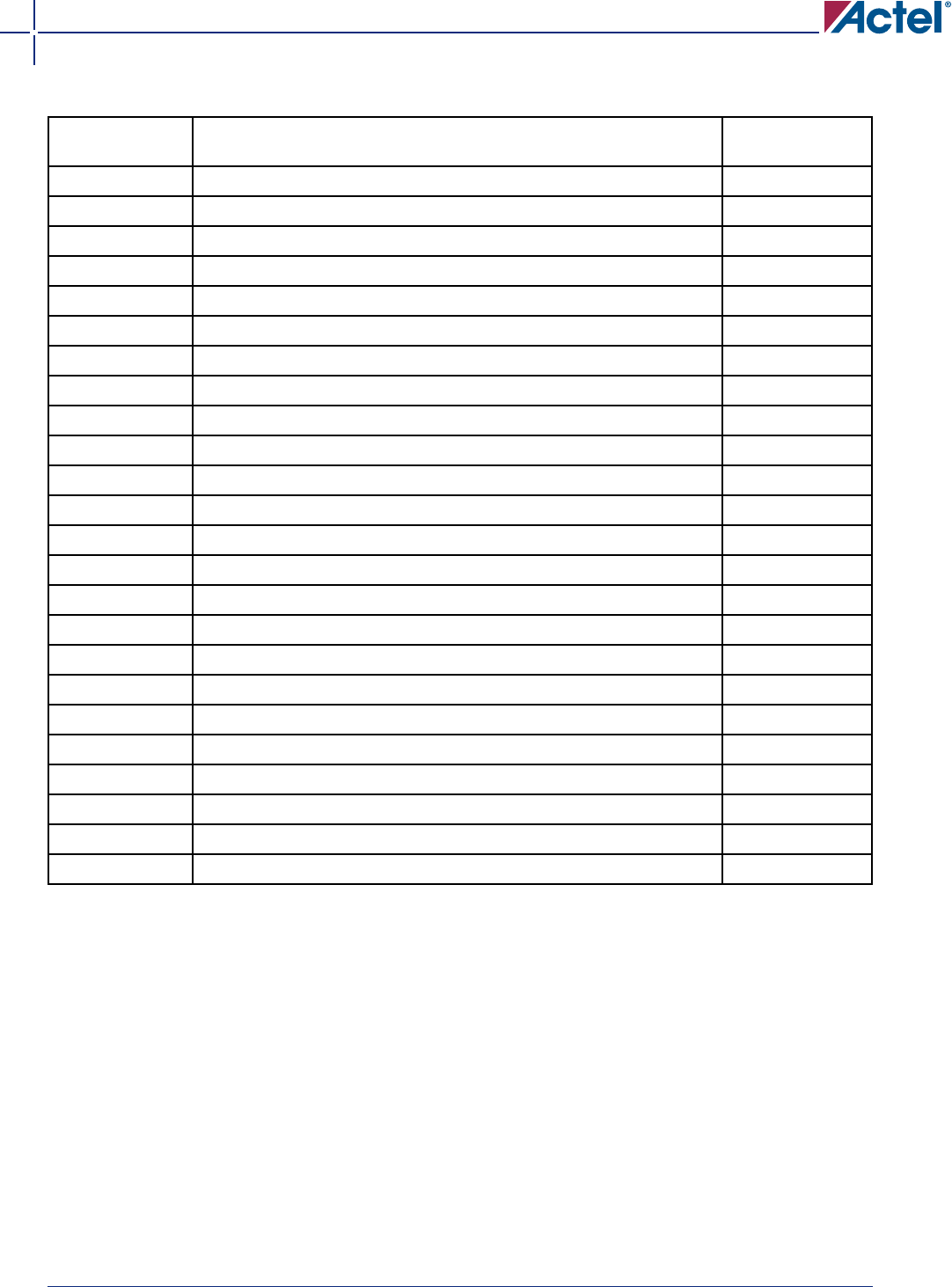

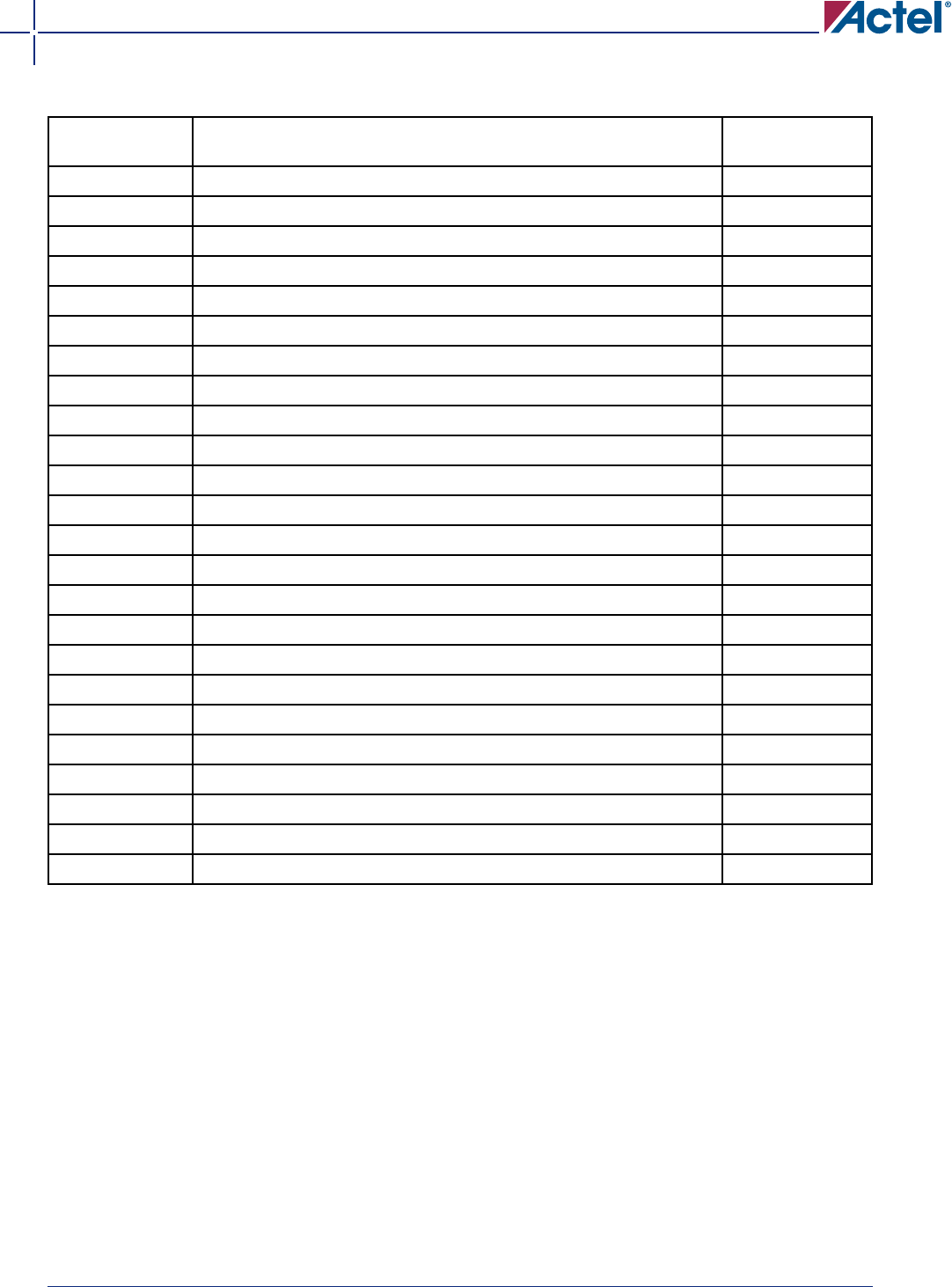

Table 2-88 • Parameter Definition and Measuring Nodes

Parameter Name Parameter Definition

Measuring Nodes

(from, to)*

t

OCLKQ

Clock-to-Q of the Output Data Register HH, DOUT

t

OSUD

Data Setup Time for the Output Data Register FF, HH

t

OHD

Data Hold Time for the Output Data Register FF, HH

t

OSUE

Enable Setup Time for the Output Data Register GG, HH

t

OHE

Enable Hold Time for the Output Data Register GG, HH

t

OCLR2Q

Asynchronous Clear-to-Q of the Output Data Register LL, DOUT

t

OREMCLR

Asynchronous Clear Removal Time for the Output Data Register LL, HH

t

ORECCLR

Asynchronous Clear Recovery Time for the Output Data Register LL, HH

t

OECLKQ

Clock-to-Q of the Output Enable Register HH, EOUT

t

OESUD

Data Setup Time for the Output Enable Register JJ, HH

t

OEHD

Data Hold Time for the Output Enable Register JJ, HH

t

OESUE

Enable Setup Time for the Output Enable Register KK, HH

t

OEHE

Enable Hold Time for the Output Enable Register KK, HH

t

OECLR2Q

Asynchronous Clear-to-Q of the Output Enable Register II, EOUT

t

OEREMCLR

Asynchronous Clear Removal Time for the Output Enable Register II, HH

t

OERECCLR

Asynchronous Clear Recovery Time for the Output Enable Register II, HH

t

ICLKQ

Clock-to-Q of the Input Data Register AA, EE

t

ISUD

Data Setup Time for the Input Data Register CC, AA

t

IHD

Data Hold Time for the Input Data Register CC, AA

t

ISUE

Enable Setup Time for the Input Data Register BB, AA

t

IHE

Enable Hold Time for the Input Data Register BB, AA

t

ICLR2Q

Asynchronous Clear-to-Q of the Input Data Register DD, EE

t

IREMCLR

Asynchronous Clear Removal Time for the Input Data Register DD, AA

t

IRECCLR

Asynchronous Clear Recovery Time for the Input Data Register DD, AA

* See Figure 2-15 on page 2-64 for more information.