ProASIC3 DC and Switching Characteristics

2-22 v1.3

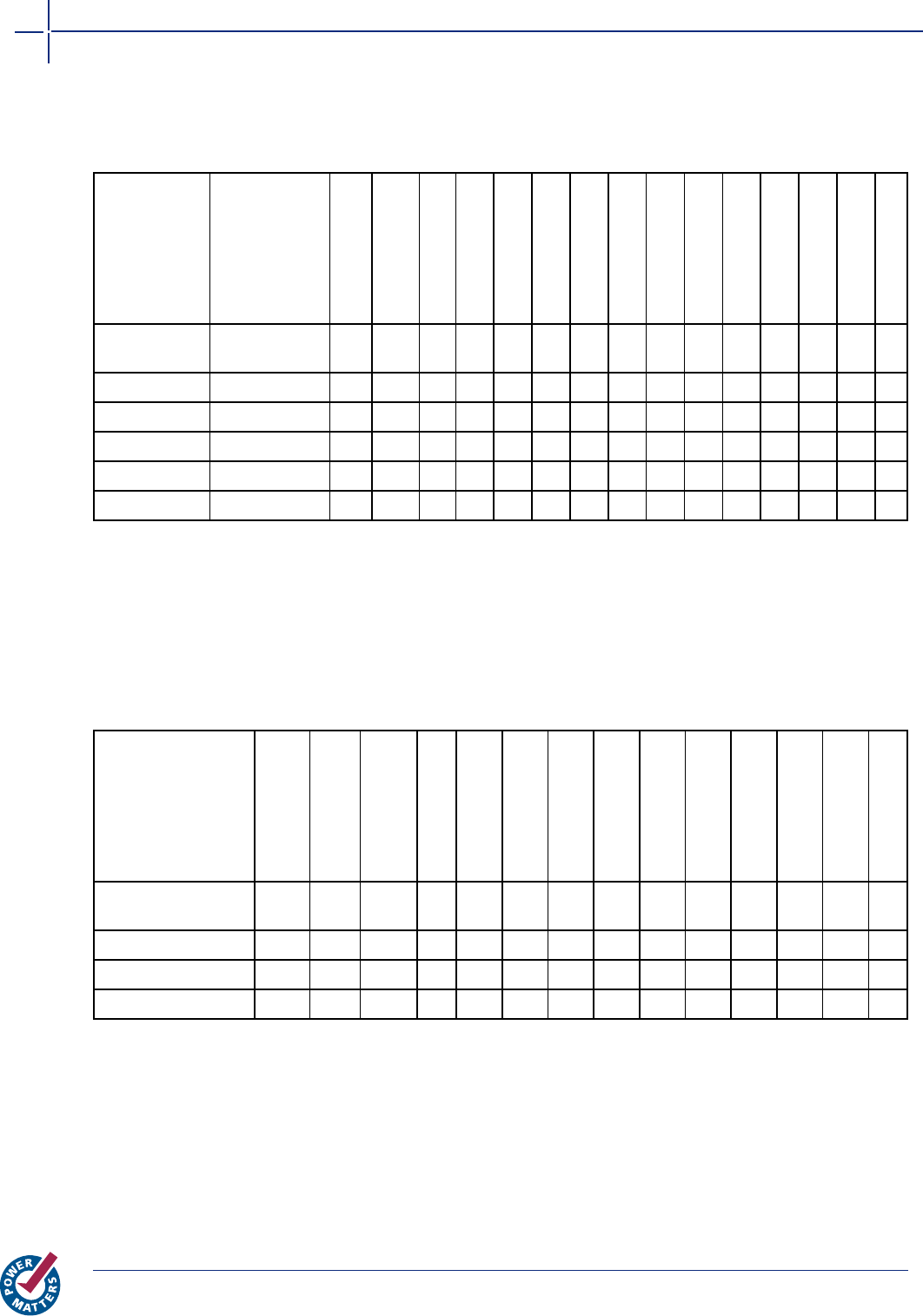

Table 2-25 • Summary of I/O Timing Characteristics—Software Default Settings

–2 Speed Grade, Commercial-Case Conditions: T

J

= 70°C, Worst Case V

CC

= 1.425 V, Worst Case

V

CCI

=3.0V

Standard Plus I/O Banks

I/O Standard

Drive Strength (mA)

Slew Rate

Capacitive Load (pF)

External Resistor

t

DOUT

(ns)

t

DP

(ns)

t

DIN

(ns)

t

PY

(ns)

t

EOUT

(ns)

t

ZL

(ns)

t

ZH

(ns)

t

LZ

(ns)

t

HZ

(ns)

t

ZLS

(ns)

t

ZHS

(ns)

Units

3.3 V LVTTL /

3.3 V LVCMOS

12 mA High 35 pF – 0.49 2.36 0.03 0.75 0.32 2.40 1.93 2.08 2.41 4.07 3.60 ns

2.5 V LVCMOS 12 mA High 35 pF – 0.49 2.39 0.03 0.97 0.32 2.44 2.35 2.11 2.32 4.11 4.02 ns

1.8 V LVCMOS 8 mA High 35 pF – 0.49 3.03 0.030.900.322.873.032.192.324.544.70 ns

1.5 V LVCMOS 4 mA High 35 pF – 0.49 3.61 0.031.060.323.353.612.262.345.025.28 ns

3.3 V PCI Per PCI spec. High 10 pF 25

2

0.49 1.72 0.03 0.64 0.32 1.76 1.27 2.08 2.41 3.42 2.94 ns

3.3 V PCI-X Per PCI-X spec. High 10 pF 25

2

0.49 1.72 0.03 0.64 0.32 1.76 1.27 2.08 2.41 3.42 2.94 ns

Notes:

1. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating

values.

2. Resistance is used to measure I/O propagation delays as defined in PCI specifications. See Figure 2-10 on

page 2-56 for connectivity. This resistor is not required during normal operation.

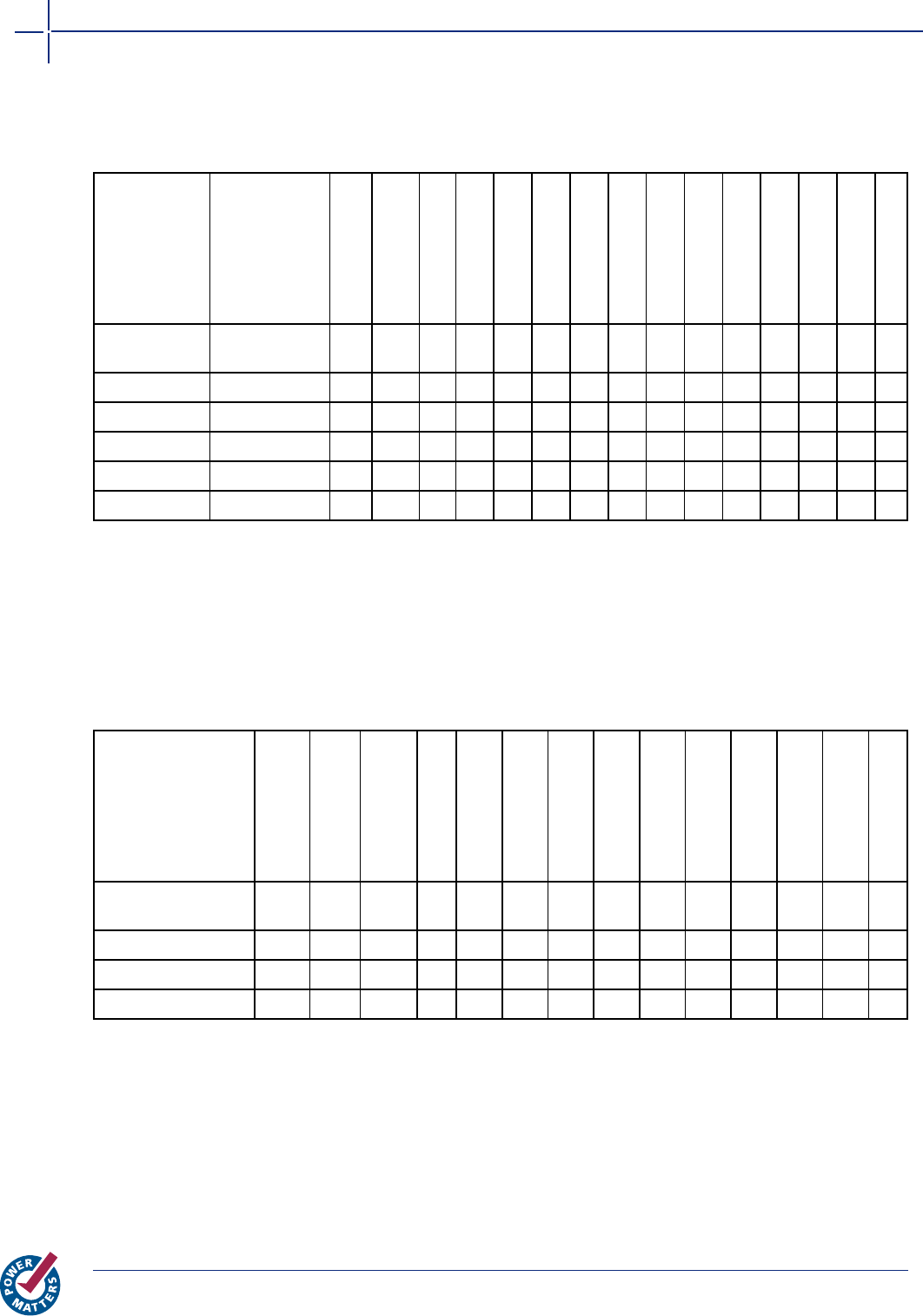

Table 2-26 • Summary of I/O Timing Characteristics—Software Default Settings

–2 Speed Grade, Commercial-Case Conditions: T

J

= 70°C, Worst Case V

CC

= 1.425 V,

Worst Case V

CCI

= 3.0 V

Standard I/O Banks

I/O Standard

Drive Strength (mA)

Slew Rate

Capacitive Load (pF)

External Resistor

t

DOUT

(ns)

t

DP

(ns)

t

DIN

(ns)

t

PY

(ns)

t

EOUT

(ns)

t

ZL

(ns)

t

ZH

(ns)

t

LZ

(ns)

t

HZ

(ns)

Units

3.3 V LVTTL /

3.3 V LVCMOS

8 mA High 35 pF – 0.49 3.29 0.03 0.75 0.32 3.36 2.80 1.79 2.01 ns

2.5 V LVCMOS 8 mA High 35 pF – 0.49 3.56 0.03 0.96 0.32 3.40 3.56 1.78 1.91 ns

1.8 V LVCMOS 4 mA High 35 pF – 0.49 4.74 0.03 0.90 0.32 4.02 4.74 1.80 1.85 ns

1.5 V LVCMOS 2 mA High 35 pF – 0.49 5.71 0.03 1.06 0.32 4.71 5.71 1.83 1.83 ns

Notes:

1. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating

values.

2. Resistance is used to measure I/O propagation delays as defined in PCI specifications. See Figure 2-10 on

page 2-56 for connectivity. This resistor is not required during normal operation.