ProASIC3 DC and Switching Characteristics

v1.3 2-19

Overview of I/O Performance

Summary of I/O DC Input and Output Levels – Default I/O Software

Settings

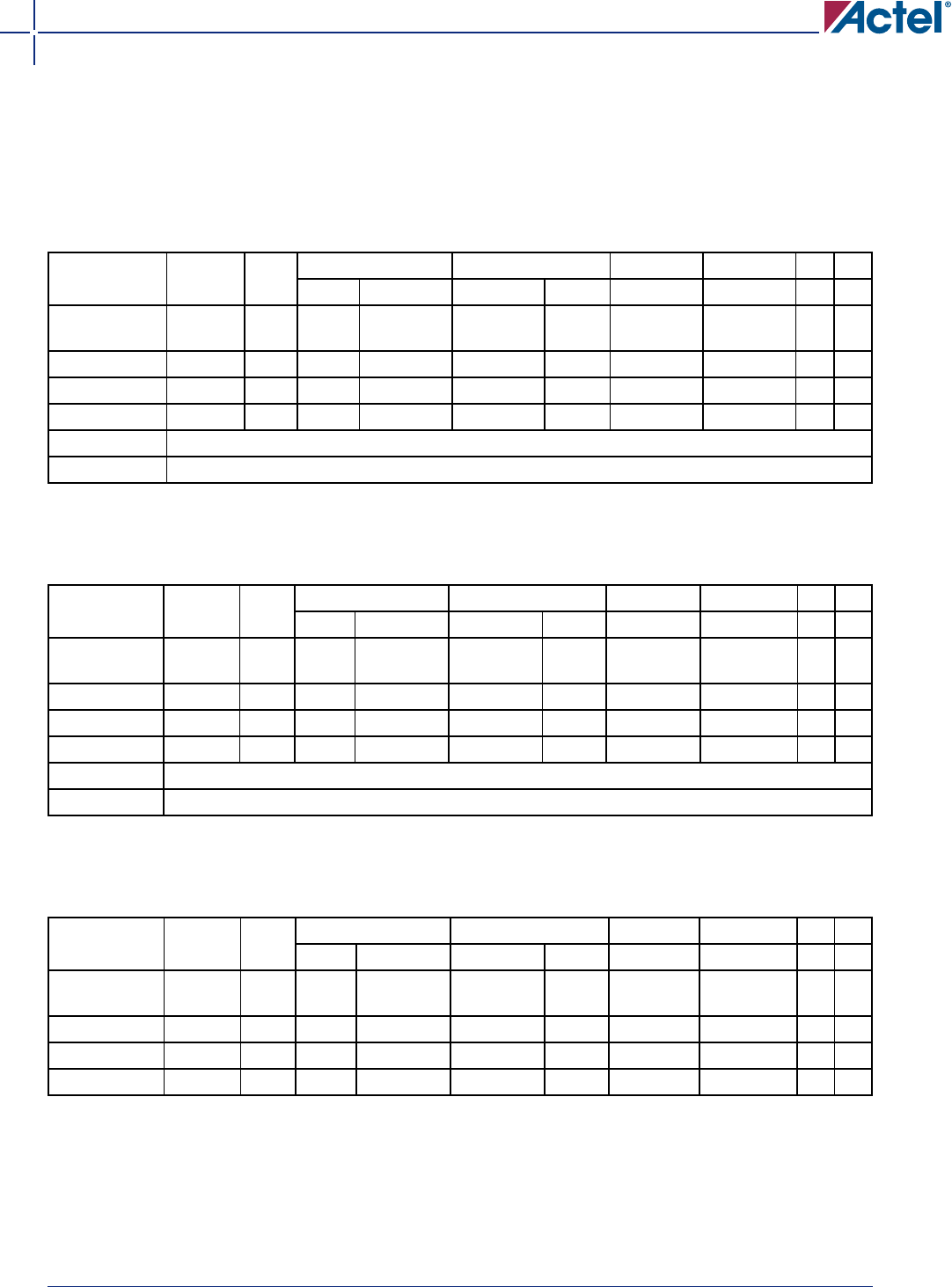

Table 2-18 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial and

Industrial Conditions—Software Default Settings

Applicable to Advanced I/O Banks

I/O Standard

Drive

Strength

Slew

Rate

V

IL

V

IH

V

OL

V

OH

I

OL

I

OH

Min, V Max, V Min, V Max, V Max, V Min, V mA mA

3.3 V LVTTL /

3.3 V LVCMOS

12 mA High –0.3 0.8 2 3.6 0.4 2.4 12 12

2.5 V LVCMOS 12 mA High –0.3 0.7 1.7 3.6 0.7 1.7 12 12

1.8 V LVCMOS 12 mA High –0.3 0.35 * V

CCI

0.65 * V

CCI

3.6 0.45 V

CCI

– 0.45 12 12

1.5 V LVCMOS 12 mA High –0.3 0.30 * V

CCI

0.7 * V

CCI

3.6 0.25 * V

CCI

0.75 * V

CCI

12 12

3.3 V PCI Per PCI specifications

3.3 V PCI-X Per PCI-X specifications

Note: Currents are measured at 85°C junction temperature.

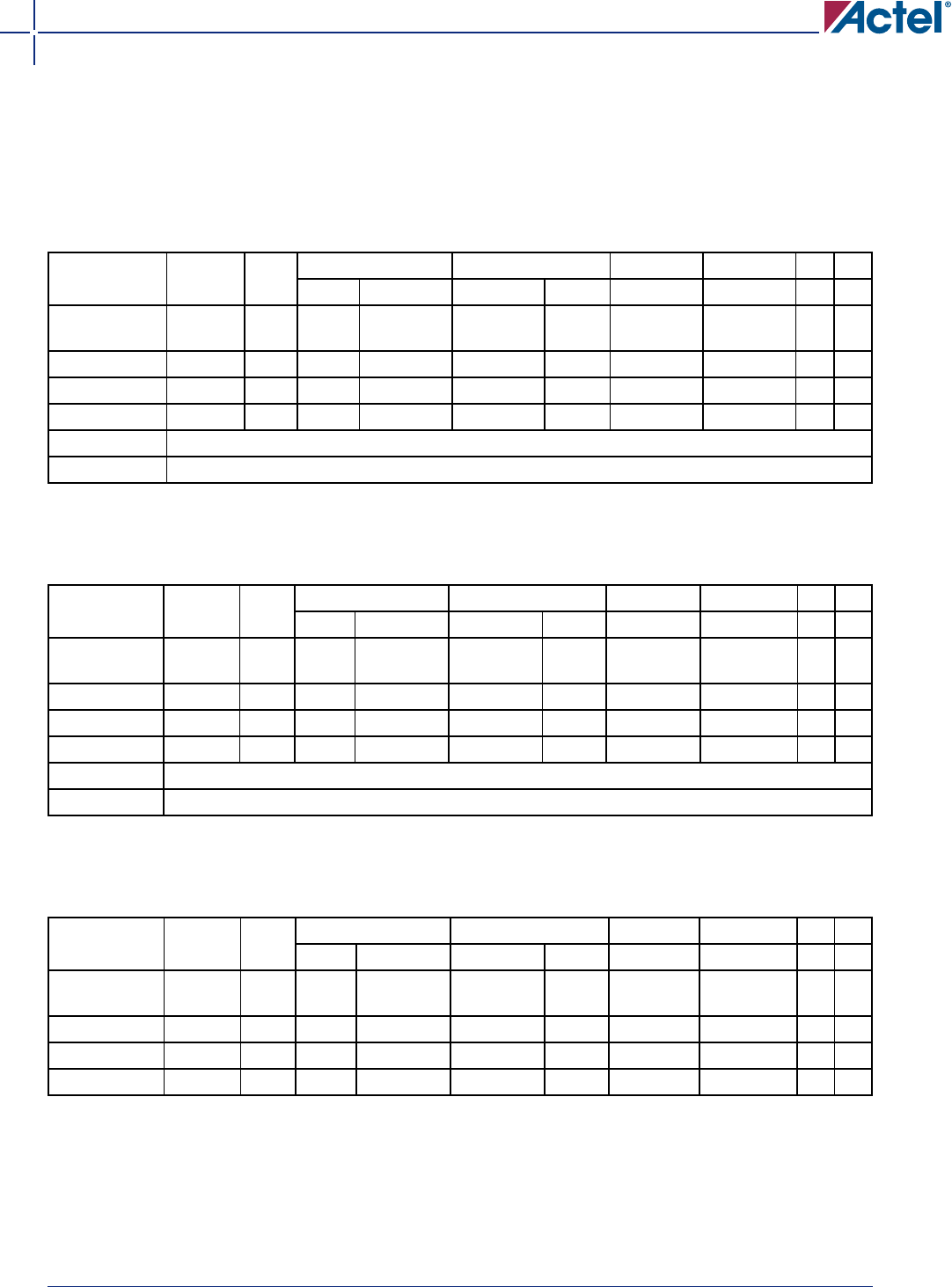

Table 2-19 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial and

Industrial Conditions—Software Default Settings

Applicable to Standard Plus I/O Banks

I/O Standard

Drive

Strength

Slew

Rate

V

IL

V

IH

V

OL

V

OH

I

OL

I

OH

Min, V Max, V Min, V Max, V Max, V Min, V mA mA

3.3 V LVTTL /

3.3 V LVCMOS

12 mA High –0.3 0.8 2 3.6 0.4 2.4 12 12

2.5 V LVCMOS 12 mA High –0.3 0.7 1.7 3.6 0.7 1.7 12 12

1.8 V LVCMOS 8 mA High –0.3 0.35 * V

CCI

0.65 * V

CCI

3.6 0.45 V

CCI

– 0.45 8 8

1.5 V LVCMOS 4 mA High –0.3 0.30 * V

CCI

0.7 * V

CCI

3.6 0.25 * V

CCI

0.75 * V

CCI

44

3.3 V PCI Per PCI specifications

3.3 V PCI-X Per PCI-X specifications

Note: Currents are measured at 85°C junction temperature.

Table 2-20 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial and

Industrial Conditions—Software Default Settings

Applicable to Standard I/O Banks

I/O Standard

Drive

Strength

Slew

Rate

V

IL

V

IH

V

OL

V

OH

I

OL

I

OH

Min, V Max, V Min, V Max, V Max, V Min, V mA mA

3.3 V LVTTL /

3.3 V LVCMOS

8 mA High –0.3 0.8 2 3.6 0.4 2.4 8 8

2.5 V LVCMOS 8 mA High –0.3 0.7 1.7 3.6 0.7 1.7 8 8

1.8 V LVCMOS 4 mA High –0.3 0.35 * V

CCI

0.65 * V

CCI

3.6 0.45 V

CCI

– 0.45 4 4

1.5 V LVCMOS 2 mA High –0.3 0.30 * V

CCI

0.7 * V

CCI

3.6 0.25 * V

CCI

0.75 * V

CCI

22

Note: Currents are measured at 85°C junction temperature.