ADG608/ADG609

REV. A

–9–

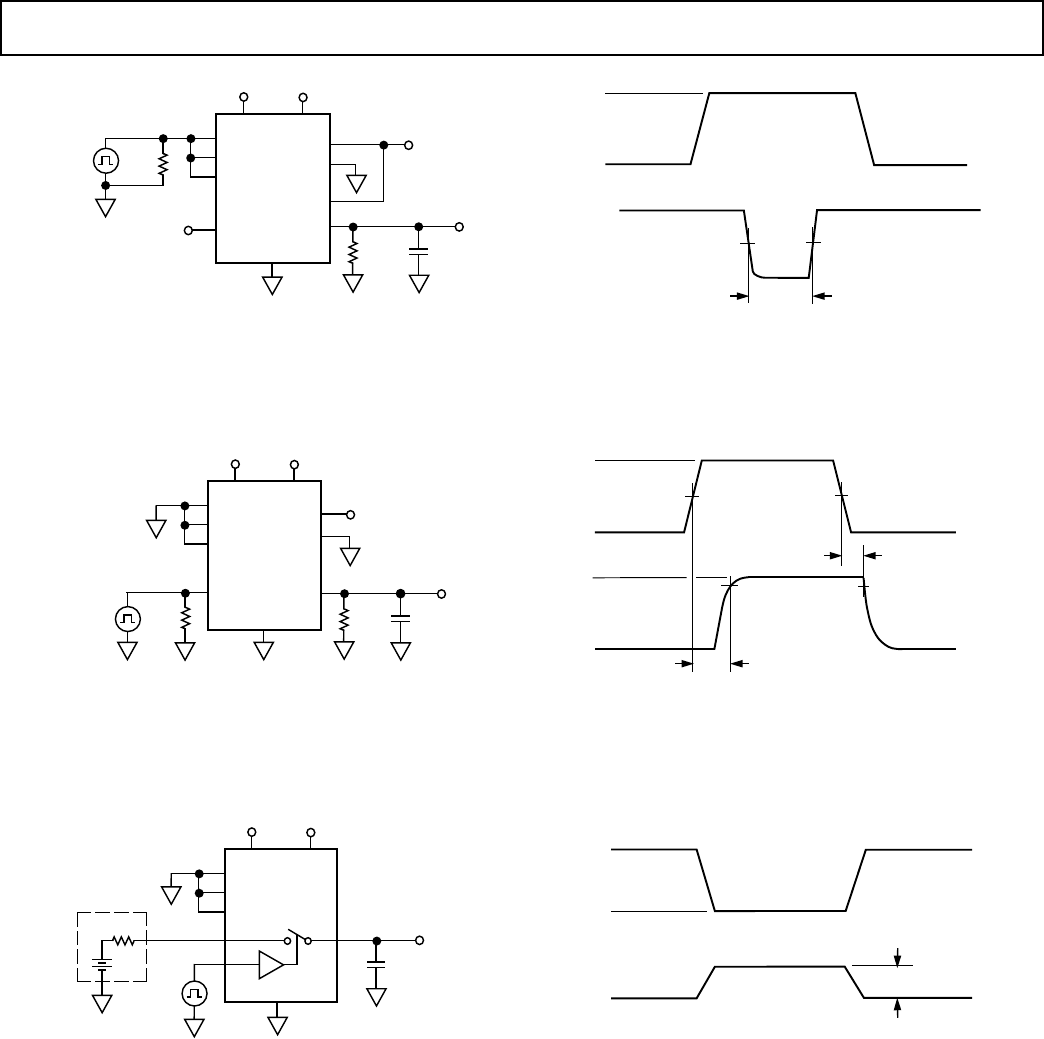

A2

V

OUT

V

SS

V

DD

D

V

S

* SIMILAR CONNECTION FOR ADG609

A1

A0

EN

GND

ADG608

*

S1

S8

S2 THRU S7

V

IN

+2.4V

50Ω

R

L

300Ω

C

L

35pF

V

SS

V

DD

ADDRESS

DRIVE (V

IN

)

3V

V

OUT

t

OPEN

80%

80%

0V

Test Circuit 6. Break-Before-Make Delay, t

OPEN

3V

50%

OUTPUT

0.9V

0

50%

t

ON

(EN)

0.9V

0

0V

V

0

0V

t

OFF

(EN)

ENABLE

DRIVE (V

IN

)

A2

V

OUT

V

SS

V

DD

D

V

S

* SIMILAR CONNECTION FOR ADG609

A1

A0

EN

GND

ADG608

*

S1

S2 THRU S8

V

IN

50Ω

R

L

300Ω

C

L

35pF

V

SS

V

DD

Test Circuit 7. Enable Delay, t

ON

(EN), t

OFF

(EN)

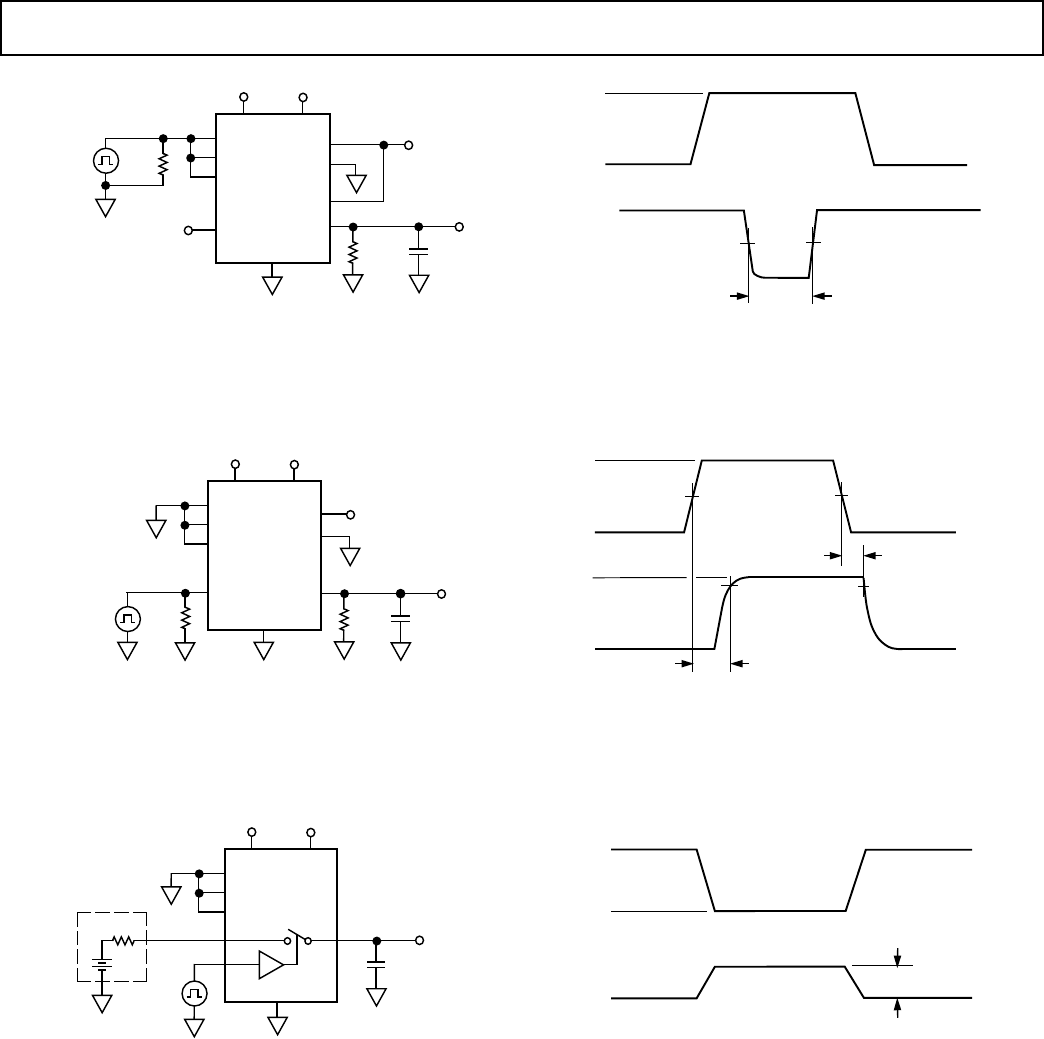

∆ V

OUT

3V

V

OUT

LOGIC

INPUT (V

IN

)

Q

INJ

= C

L

x ∆V

OUT

0V

A2

V

OUT

V

SS

V

DD

D

* SIMILAR CONNECTION FOR ADG609

A1

A0

EN

GND

ADG608*

V

IN

C

L

1nF

V

SS

V

DD

S

R

S

V

S

Test Circuit 8. Charge Injection