AD9696/AD9698

–6–

REV. B

R

R

A2

A1

AD9698

+IN

1

–IN

1

+V

REF

R

1

Q

1 OUT

R = 10kΩ

R

1

+ R

2

>5kΩ

A

1

,A

2

= AD708 or OP– 290

(±5V) (+5V)

R

2

Q

1 OUT

Q

1 OUT

Q

2 OUT

Q

2 OUT

+Q

2 OUT

–V

REF

V

SIGNAL

V

IN

+IN

2

–IN

2

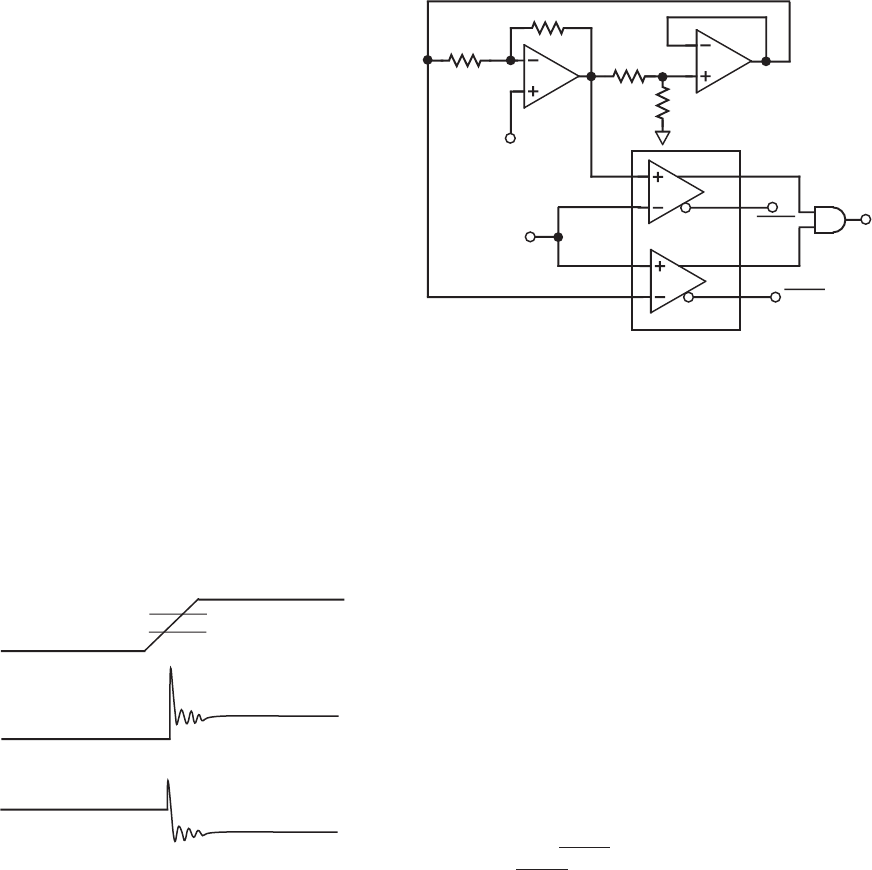

Figure 1. AD9698 Used as Window Detector

When configured as shown, the op amps generate reference lev-

els for the comparators that are equally spaced above and below

the applied V

IN

. The width of the window is established by the

ratio of R1 and R2. For a given ratio of R1 and R2, +V

REF

and

–V

REF

will be fixed percentages above and below V

IN

. As an ex-

ample, using 2.2 kΩ for R1 and 10 kΩ for R2 creates a ±10%

window. When V

IN

equals +3 V, +V

REF

will be +3.3 V and

–V

REF

will be +2.7 V. Likewise, for a –2 V input, the thresholds

will be –1.8 V and –2.2 V. Windows of differing percentage

width can be calculated with the equation:

(1–X)/2X = R2/R1

where:

X = % window

Additionally, the low impedance of the op amp outputs assures

that the threshold voltages will remain constant when the input

currents change as the signal passes through the threshold volt-

age levels.

The output of the AND gate will be high while the signal is in-

side the window. Q1

OUT

will be high when the signal is above

+V

REF

, and Q2

OUT

will be high when the signal is below –V

REF

.

Crystal Oscillator

Oscillators are used in a wide variety of applications from audio

circuits to waveform generators, from ATE triggers and tele-

communications transceivers to radar. Figure 2 shows a versatile

and inexpensive oscillator. The circuit uses the AD9696, in a

positive feedback mode, and is capable of generating accurate

and stable oscillations with frequencies ranging from 1 MHz to

more than 40 MHz.

To generate oscillations from 1 to 25 MHz, a fundamental

mode crystal is used without the dc blocking capacitor and

choke. The parallel capacitor on the inverting input is selected

for stability (0.1 µF for 1–10 MHz; 220 pF for frequencies

above 10 MHz).

APPLICATIONS

General

Two characteristics of the AD9696 and AD9698 should be con-

sidered for any application. First is the fact that all TTL com-

parators are prone to oscillate if the inputs are close to equal for

any appreciable period of time. One instance of this happening

would be slow changes in the unknown signal; the probability of

oscillation is reduced when the unknown signal passes through

the threshold at a high slew rate. Another instance is if the un-

known signal does not overdrive the comparator logic. Unless

they are overdriven, TTL comparators have undershoot when

switching logic states. The smaller the overdrive, the greater the

undershoot; when small enough, the comparator will oscillate,

not being able to determine a valid logic state. For the AD9696

and AD9698, 20 mV is the smallest overdrive which will assure

crisp switching of logic states without significant undershoot.

The second characteristic to keep in mind when designing

threshold circuits for these comparators is twofold: (1) bias cur-

rents change when the threshold is exceeded; and (2) ac input

impedance decreases when the comparator is in its linear region.

During the time both transistors in the differential pair are con-

ducting, the ac input impedance drops by orders of magnitude.

Additionally, the input bias current switches from one input to

the other, depending upon whether or not the threshold is ex-

ceeded. As a result, the input currents follow approximately the

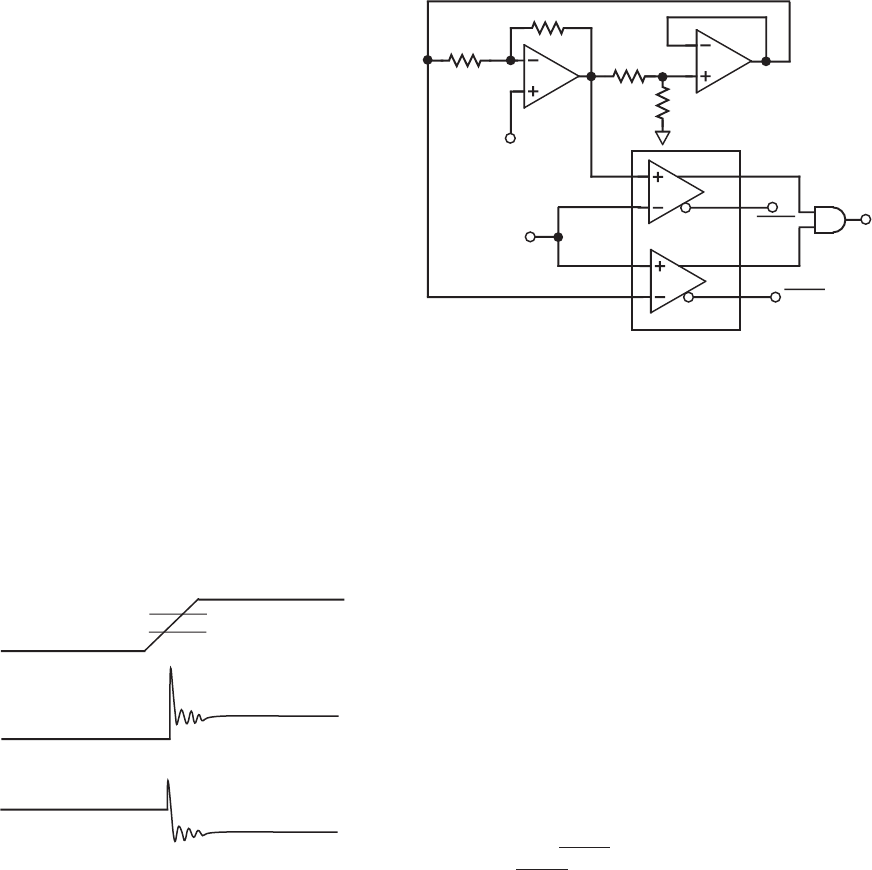

characteristic curves shown below.

{

SIGNAL

VOLTAGE

AT +INPUT

+INPUT

CURRENT

– INPUT

CURRENT

LINEAR

REGION

Threshold Input Currents

This characteristic will not cause problems unless a high imped-

ance threshold circuit or drive circuit is employed. A circuit

similar to that shown in the window comparator application can

eliminate this possible problem.

Window Comparator

Many applications require determining when a signal’s voltage

falls within, above, or below a particular voltage range. A simple

tracking window comparator can provide this data. Figure 1

shows such a window comparator featuring high speed, TTL

compatibility, and ease of implementation.

Two comparators are required to establish a “window” with up-

per and lower threshold voltages. The circuit shown uses the

AD9698 dual ultrafast TTL comparator. In addition to the cost

and space savings over a design using two single comparators,

the dual comparator on a single die produces better matching of

both dc and dynamic characteristics.