REV. B

–4–

AD724

PIN FUNCTION DESCRIPTIONS

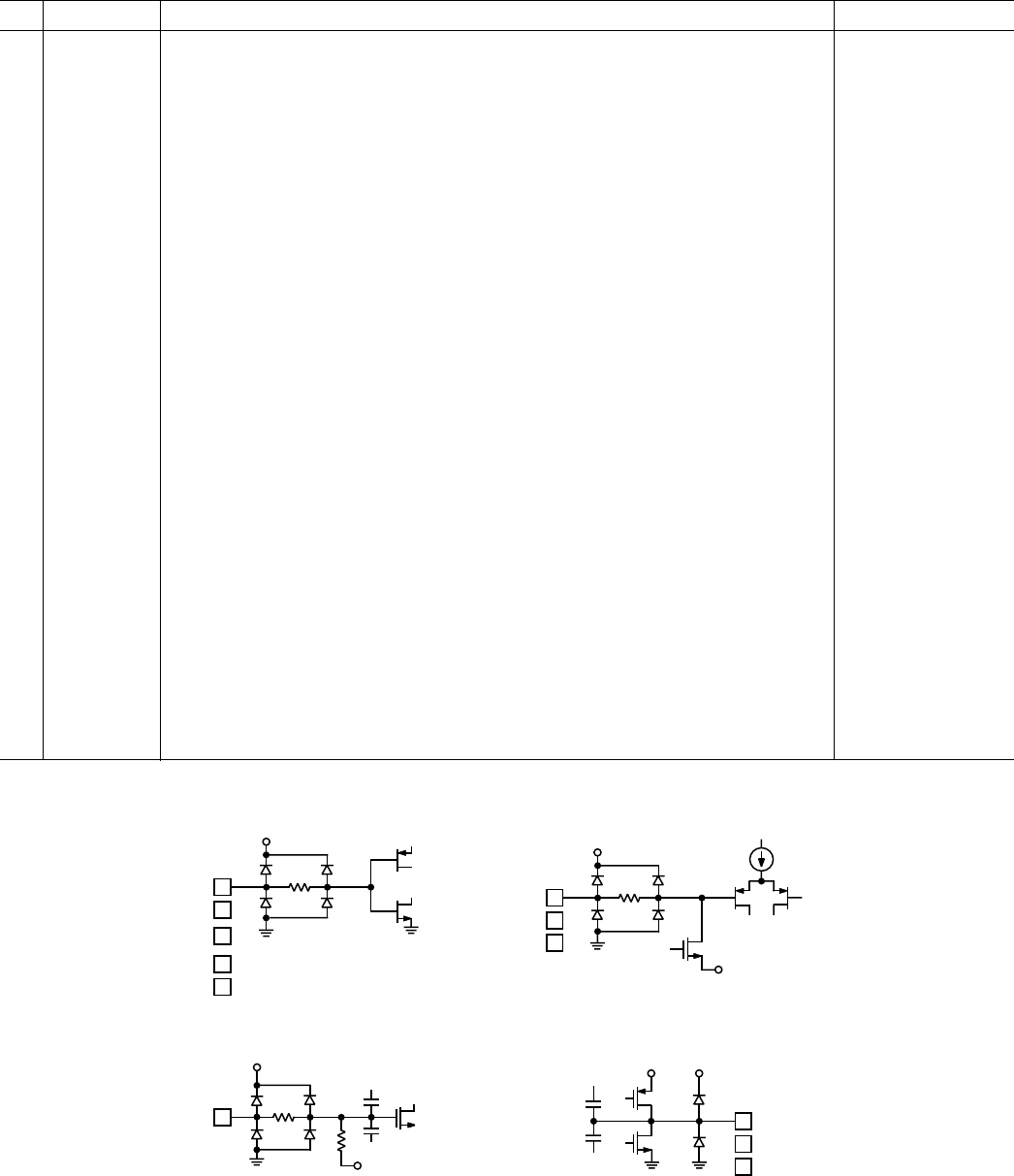

Pin Mnemonic Description Equivalent Circuit

1 STND A Logical HIGH input selects NTSC encoding. Circuit A

A Logical LOW input selects PAL encoding.

CMOS/TTL Logic Levels.

2 AGND Analog Ground Connection.

3 FIN FSC clock or parallel-resonant crystal, or 4FSC clock input. Circuit B

For NTSC: 3.579 545 MHz or 14.318 180 MHz.

For PAL: 4.433 619 MHz or 17.734 480 MHz.

CMOS/TTL Logic Levels for subcarrier clocks.

4 APOS Analog Positive Supply (+5 V ± 5%).

5 ENCD A Logical HIGH input enables the encode function. Circuit A

A Logical LOW input powers down chip when not in use.

CMOS/TTL Logic Levels.

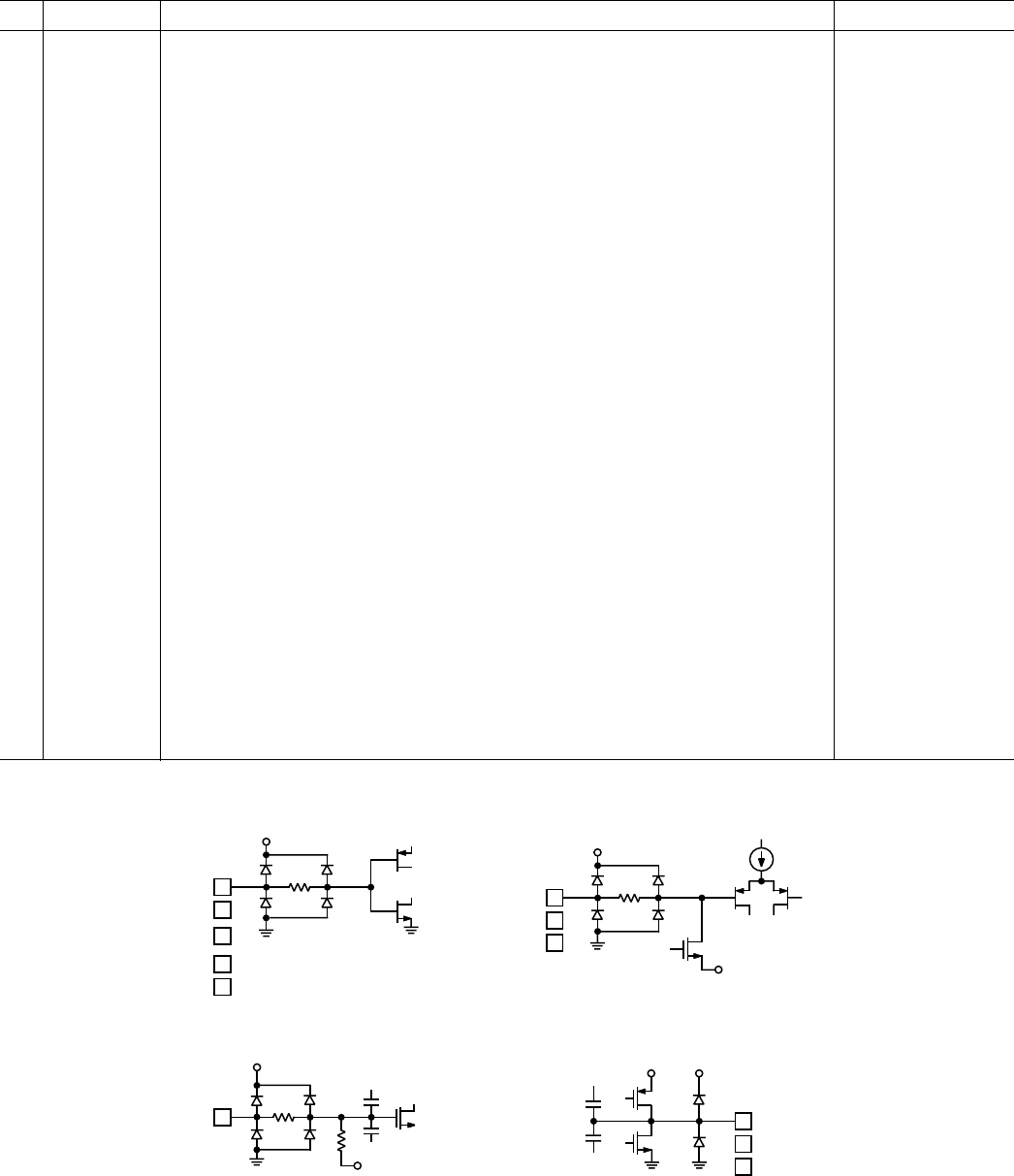

6 RIN Red Component Video Input. Circuit C

0 to 714 mV AC-Coupled.

7 GIN Green Component Video Input. Circuit C

0 to 714 mV AC-Coupled.

8 BIN Blue Component Video Input. Circuit C

0 to 714 mV AC-Coupled.

9 CRMA Chrominance Output.* Circuit D

Approximately 1.8 V peak-to-peak for both NTSC and PAL.

10 COMP Composite Video Output.* Circuit D

Approximately 2.5 V peak-to-peak for both NTSC and PAL.

11 LUMA Luminance plus SYNC Output.* Circuit D

Approximately 2 V peak-to-peak for both NTSC and PAL.

12 SELECT A Logical LOW input selects the FSC operating mode. Circuit A

A Logical HIGH input selects the 4FSC operating mode.

CMOS/TTL Logic Levels.

13 DGND Digital Ground Connections.

14 DPOS Digital Positive Supply (+5 V ± 5%).

15 VSYNC Vertical Sync Signal (if using external CSYNC set at > +2 V). CMOS/TTL Logic Levels. Circuit A

16 HSYNC Horizontal Sync Signal (or CSYNC signal). CMOS/TTL Logic Levels. Circuit A

*The Luminance, Chrominance and Composite Outputs are at twice normal levels for driving 75 Ω reverse-terminated lines.

5

1

12

15

16

DPOS

DGND

3

V

BIAS

DPOS

DGND

7

V

CLAMP

6

8

DPOS

DGND

10

9

11

APOS

AGND

DGND

DPOS

Circuit B Circuit D

Equivalent Circuits

Circuit A Circuit C