AD2S83

–5–

REV. D

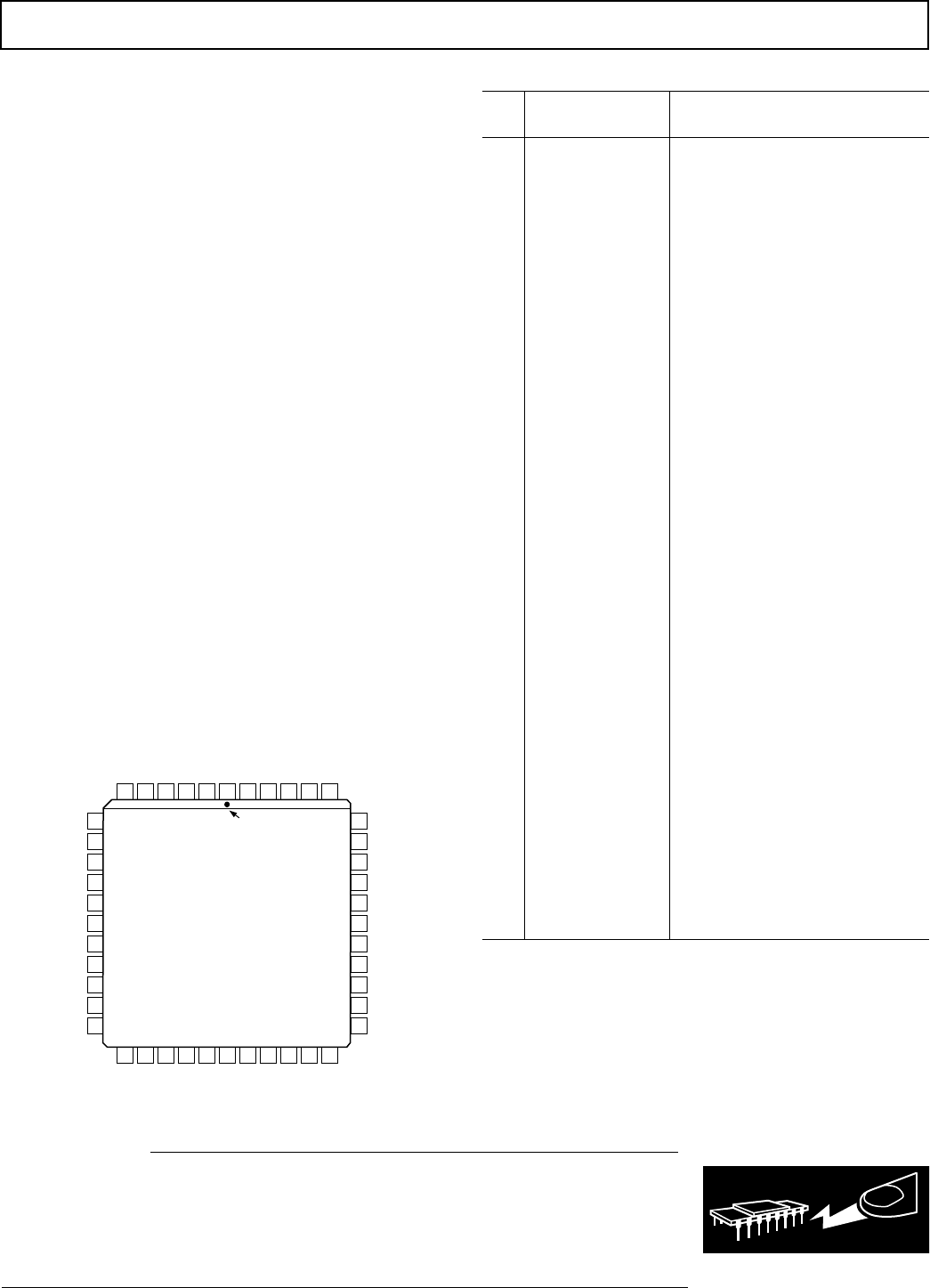

PIN FUNCTION DESCRIPTIONS

P

in

Nos. Mnemonic Description

1 DEMOD O/P Demodulator Output

2 REFERENCE I/P Reference Signal Input

3 AC ERROR O/P Ratio Multiplier Output

4 COS Cosine Input

5 ANALOG GND Power Ground

6 SIGNAL GND Resolver Signal Ground

7 SIN Sine Input

8+V

S

Positive Power Supply

10–25 DB1–DB16 Parallel Output Data

26 +V

L

Logic Power Supply

27 ENABLE Logic HI—Output Data Pins in

High Impedance State

Logic LO—Presents Active Data

to the Output Pins

28 BYTE SELECT Logic HI—Most Significant Byte to

DB1–DB8

Logic LO—Least Significant Byte

to DB1–DB8

30 INHIBIT Logic LO Inhibits Data Transfer

to Output Latches

31 DIGITAL GND Digital Ground

32, 33 SC2–SC1 Select Converter Resolution

34 DATA LOAD Logic LO DB1–DB16 Inputs

Logic HI DB1–DB16 Outputs

35 COMPLEMENT Active Logic LO

36 BUSY Converter Busy, Data not Valid

While Busy HI

37 DIRECTION Logic State Defines Direction of

Input Signal Rotation

38 RIPPLE CLOCK Positive Pulse When Converter Output

Changes from 1s to All 0s or Vice Versa

39 –V

S

Negative Power Supply

40 VCO I/P VCO Input

41 VCO O/P VCO Output

42 INTEGRATOR O/P Integrator Output

43 INTEGRATOR I/P Integrator Input

44 DEMOD I/P Demodulator Input

ABSOLUTE MAXIMUM RATINGS

1

(with respect to GND)

+V

S

2

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +13 V dc

–V

S

2

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –13 V dc

+V

L

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +V

S

Reference . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +13 V to –V

S

SIN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +13 V to –V

S

COS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +13 V to –V

S

Any Logical Input . . . . . . . . . . . . . . . . . . –0.4 V dc to +V

L

dc

Demodulator Input . . . . . . . . . . . . . . . . . . . . . . . +13 V to –V

S

Integrator Input . . . . . . . . . . . . . . . . . . . . . . . . . . +13 V to –V

S

VCO Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +13 V to –V

S

Power Dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . 800 mW

Operating Temperature

Industrial (AP, IP) . . . . . . . . . . . . . . . . . . . –40°C to +85°C

Storage Temperature . . . . . . . . . . . . . . . . . . –65°C to +150°C

Lead Temperature (Soldering, 10 sec) . . . . . . . . . . . . +300°C

CAUTION

1

Absolute Maximum Ratings are those values beyond which damage to the device

may occur.

2

Correct polarity voltages must be maintained on the +V

S

and –V

S

pins.

RECOMMENDED OPERATING CONDITIONS

Power Supply Voltage (+V

S

, –V

S

) . . . . . . . . . . ±12 V dc ± 5%

Power Supply Voltage V

L

. . . . . . . . . . . . . . . . . +5 V dc ± 10%

Analog Input Voltage (SIN and COS) . . . . . . . .2 V rms ± 10%

Analog Input Voltage (REF) . . . . . . . . . . . . . . 1 V to 8 V peak

Signal and Reference Harmonic Distortion . . . . . . . 10% (max)

Phase Shift Between Signal and Reference . . . ±10 Degrees (max)

Ambient Operating Temperature Range

Industrial (AP, IP) . . . . . . . . . . . . . . . . . . . . –40°C to +85°C

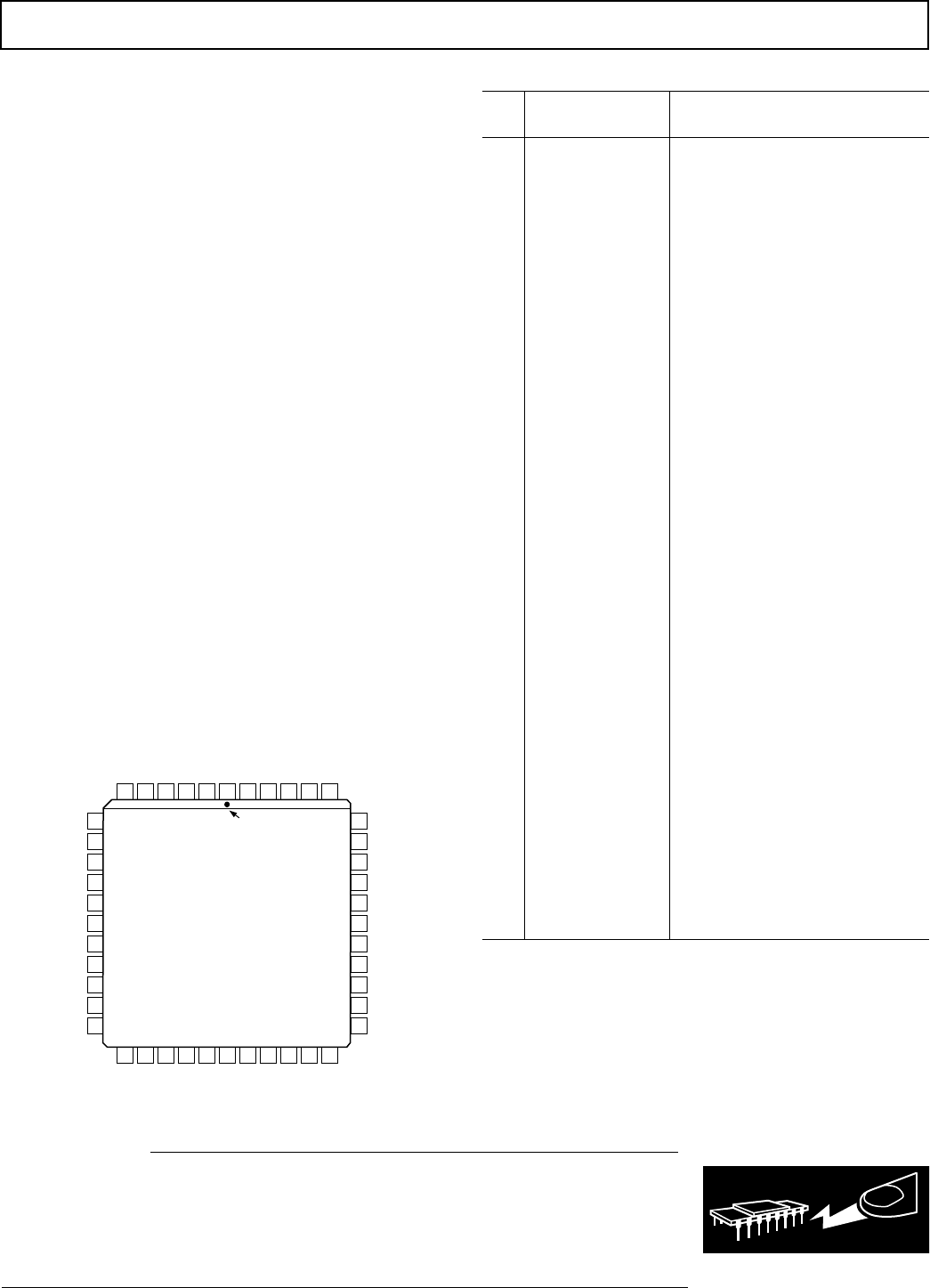

PIN CONFIGURATION

9

10

11

12

13

7

8

16

17

14

15

21443

4

5642414043

35

36

37

38

39

33

34

31

32

29

30

–V

S

RIPPLE CLOCK

DIRECTION

BUSY

COMP

DATA LOAD

SC1

DB14

DB11

DB12

DB13

DB15

SIN I/P

+V

S

NC

(MSB) DB1

DB2

DB3

DB4

NC = NO CONNECT

DB5

DB6

DB7

DB8

SC2

DIGITAL GND

INHIBIT

NC

SIGNAL GND

ANALOG GND

COS I/P

AC ERROR O/P

REF I/P

DEMOD O/P

DEMOD I/P

INTEGRATOR I/P

INTEGRATOR O/P

VCO O/P

VCO I/P

18

19

20 21 22 23 24 25

26

27 28

PIN 1

IDENTIFIER

TOP VIEW

(Not to Scale)

AD2S83

(LSB) DB16

+V

L

ENABLE

BYTE SELECT

DB10

DB9

ESD SENSITIVITY

The AD2S83 features an input protection circuit consisting of large “distributed” diodes and

polysilicon series resistors to dissipate both high energy discharge (Human Body Model) and fast, low

energy pulses (Charges Device Model).

Proper ESD protection are strongly recommended to avoid functional damage or performance

degradation. For further information on ESD precautions, refer to Analog Devices ESD Prevention

Manual.

WARNING!

ESD SENSITIVE DEVICE