FEATURES

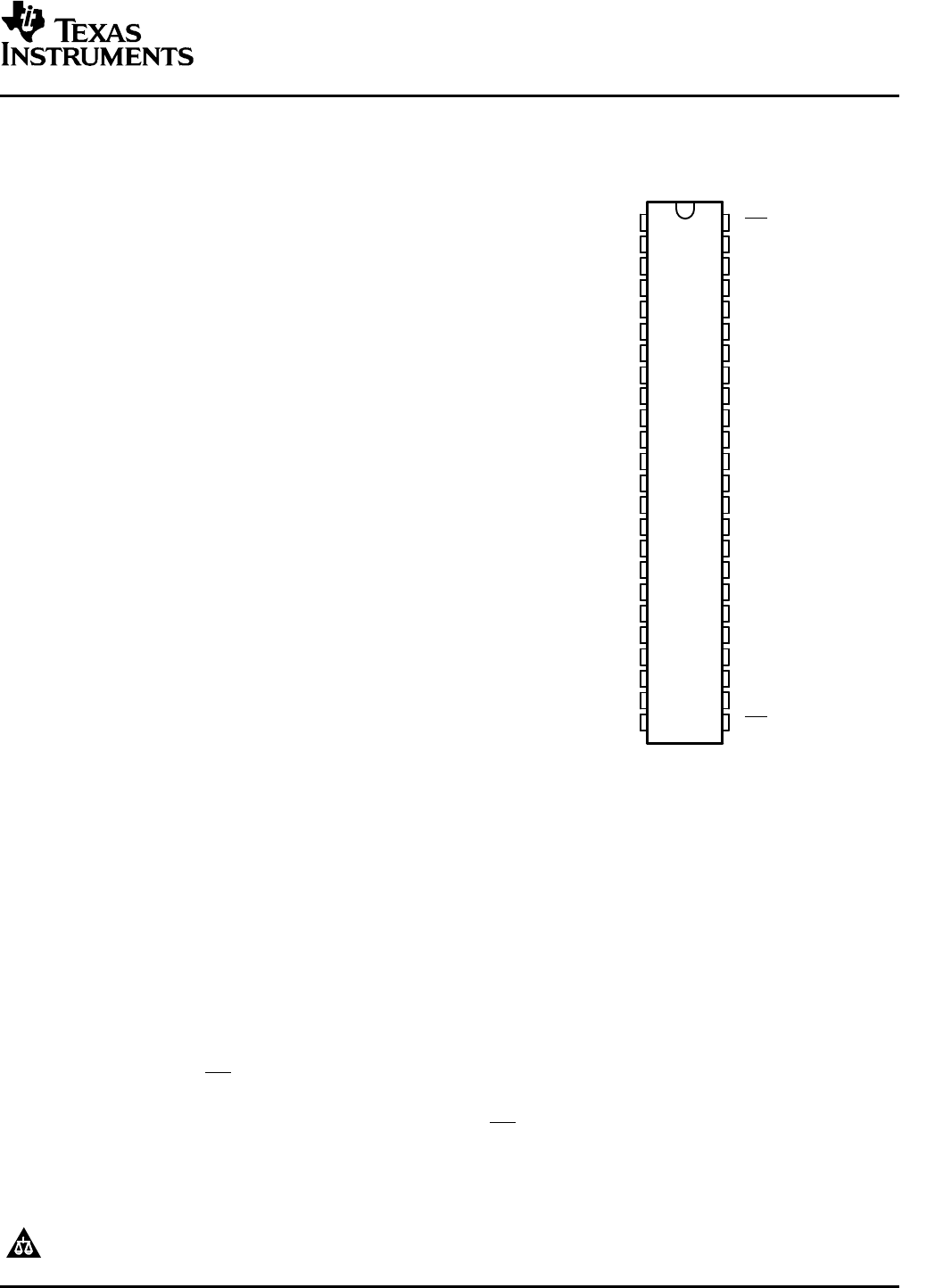

DL PACKAGE

(TOP VIEW)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

1DIR

1B1

1B2

GND

1B3

1B4

V

CC

1B5

1B6

GND

1B7

1B8

2B1

2B2

GND

2B3

2B4

V

CC

2B5

2B6

GND

2B7

2B8

2DIR

1OE

1A1

1A2

GND

1A3

1A4

V

CC

1A5

1A6

GND

1A7

1A8

2A1

2A2

GND

2A3

2A4

V

CC

2A5

2A6

GND

2A7

2A8

2OE

DESCRIPTION/ORDERING INFORMATION

SN74ABT16245A-EP

16-BIT BUS TRANSCEIVER

WITH 3-STATE OUTPUTS

SCBS807B – OCTOBER 2005 – REVISED JANUARY 2006

• Controlled Baseline

– One Assembly/Test Site, One Fabrication

Site

• Enhanced Diminishing Manufacturing

Sources (DMS) Support

• Enhanced Product-Change Notification

• Qualification Pedigree

(1)

• Member of the Texas Instruments

Widebus™ Family

• State-of-the-Art EPIC-IIB™ BiCMOS Design

Significantly Reduces Power Dissipation

• Typical V

OLP

(Output Ground Bounce) <1 V at

V

CC

= 5 V, T

A

= 25 ° C

• High-Impedance State During Power Up and

Power Down

• Distributed V

CC

and GND Pin Configuration

Minimizes High-Speed Switching Noise

• Flow-Through Architecture Optimizes PCB

Layout

• High-Drive Outputs (–32-mA I

OH

, 64-mA I

OL

)

• Latch-Up Performance Exceeds 500 mA Per

JESD 70

• ESD Protection Exceeds 2000 V Per

MIL-STD-883, Method 3015; Exceeds 200 V

Using Machine Model (C = 200 pF, R = 0)

• Shrink Small-Outline (DL) Package

(1) Component qualification in accordance with JEDEC and

industry standards to ensure reliable operation over an

extended temperature range. This includes, but is not limited

to, Highly Accelerated Stress Test (HAST) or biased 85/85,

temperature cycle, autoclave or unbiased HAST,

electromigration, bond intermetallic life, and mold compound

life. Such qualification testing should not be viewed as

justifying use of this component beyond specified

performance and environmental limits.

The SN74ABT16245A-EP is a 16-bit noninverting 3-state transceiver designed for synchronous two-way

communication between data buses. The control-function implementation minimizes external timing

requirements.

This device can be used as two 8-bit transceivers or one 16-bit transceiver. It allows data transmission from the

A bus to the B bus or from the B bus to the A bus, depending on the logic level at the direction-control (DIR)

input. The output-enable ( OE) input can be used to disable the device so that the buses are effectively isolated.

When V

CC

is between 0 and 2.1 V, the device is in the high-impedance state during power up or power down.

However, to ensure the high-impendance state above 2.1 V, OE should be tied to V

CC

through a pullup resistor;

the minimum value of the resistor is determined by the current-sinking capability of the driver.

The SN74ABT16245A-EP is characterized for operation from –55 ° C to 125 ° C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Widebus, EPIC-IIB are trademarks of Texas Instruments.

PRODUCTION DATA information is current as of publication date.

Copyright © 2005–2006, Texas Instruments Incorporated

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.