Data Sheet

FlashFlex51 MCU

SST89E52RD2/RD / SST89E54RD2/RD / SST89E58RD2/RD

SST89V52RD2/RD / SST89V54RD2/RD / SST89V58RD2/RD

29

©2006 Silicon Storage Technology, Inc. S71255-05-000 5/06

Symbol Function

SPIE If both SPIE and ES are set to one, SPI interrupts are enabled.

SPE SPI enable bit.

0: Disables SPI.

1: Enables SPI and connects SS#, MOSI, MISO, and SCK to pins P1.4, P1.5, P1.6, P1.7.

DORD Data Transmission Order.

0: MSB first in data transmission.

1: LSB first in data transmission.

MSTR Master/Slave select.

0: Selects Slave mode.

1: Selects Master mode.

CPOL Clock Polarity

0: SCK is low when idle (Active High).

1: SCK is high when idle (Active Low).

CPHA Clock Phase control bit. The CPHA bit with the CPOL bit control the clock and data

relationship between master and slave. See Figures 6-5 and 6-6.

0: Shift triggered on the leading edge of the clock.

1: Shift triggered on the trailing edge of the clock.

SPR1, SPR0 SPI Clock Rate Select bits. These two bits control the SCK rate of the device

configured as master. SPR1 and SPR0 have no effect on the slave. The relationship

between SCK and the oscillator frequency, f

OSC

, is as follows:

Symbol Function

SPIF SPI Interrupt Flag.

Upon completion of data transfer, this bit is set to 1.

If SPIE =1 and ES =1, an interrupt is then generated.

This bit is cleared by software.

WCOL Write Collision Flag.

Set if the SPI data register is written to during data transfer.

This bit is cleared by software.

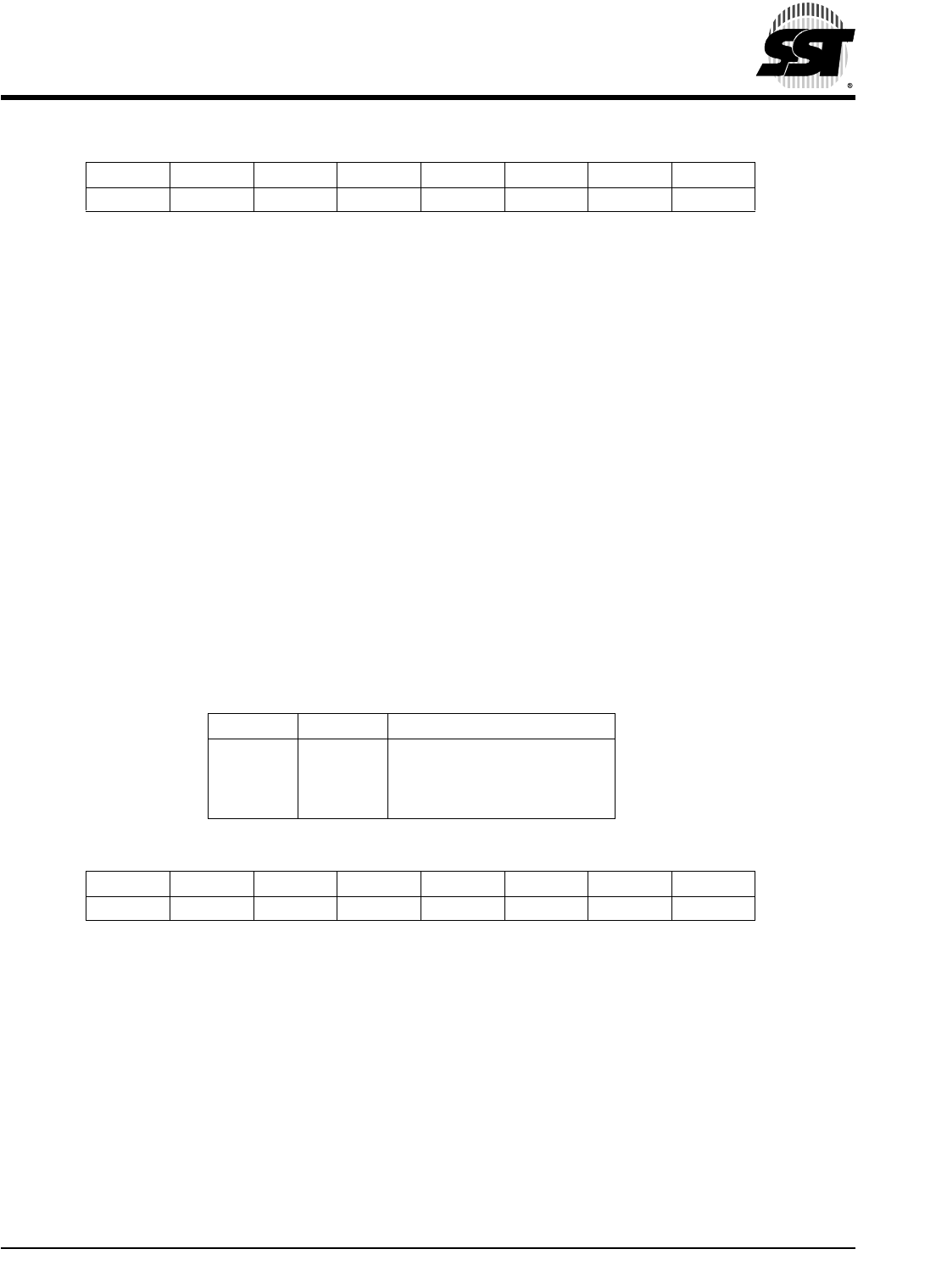

SPI Control Register (SPCR)

Location76543210Reset Value

D5H SPIE SPE DORD MSTR CPOL CPHA SPR1 SPR0 00H

SPR1 SPR0 SCK = f

OSC

divided by

0

0

1

1

0

1

0

1

4

16

64

128

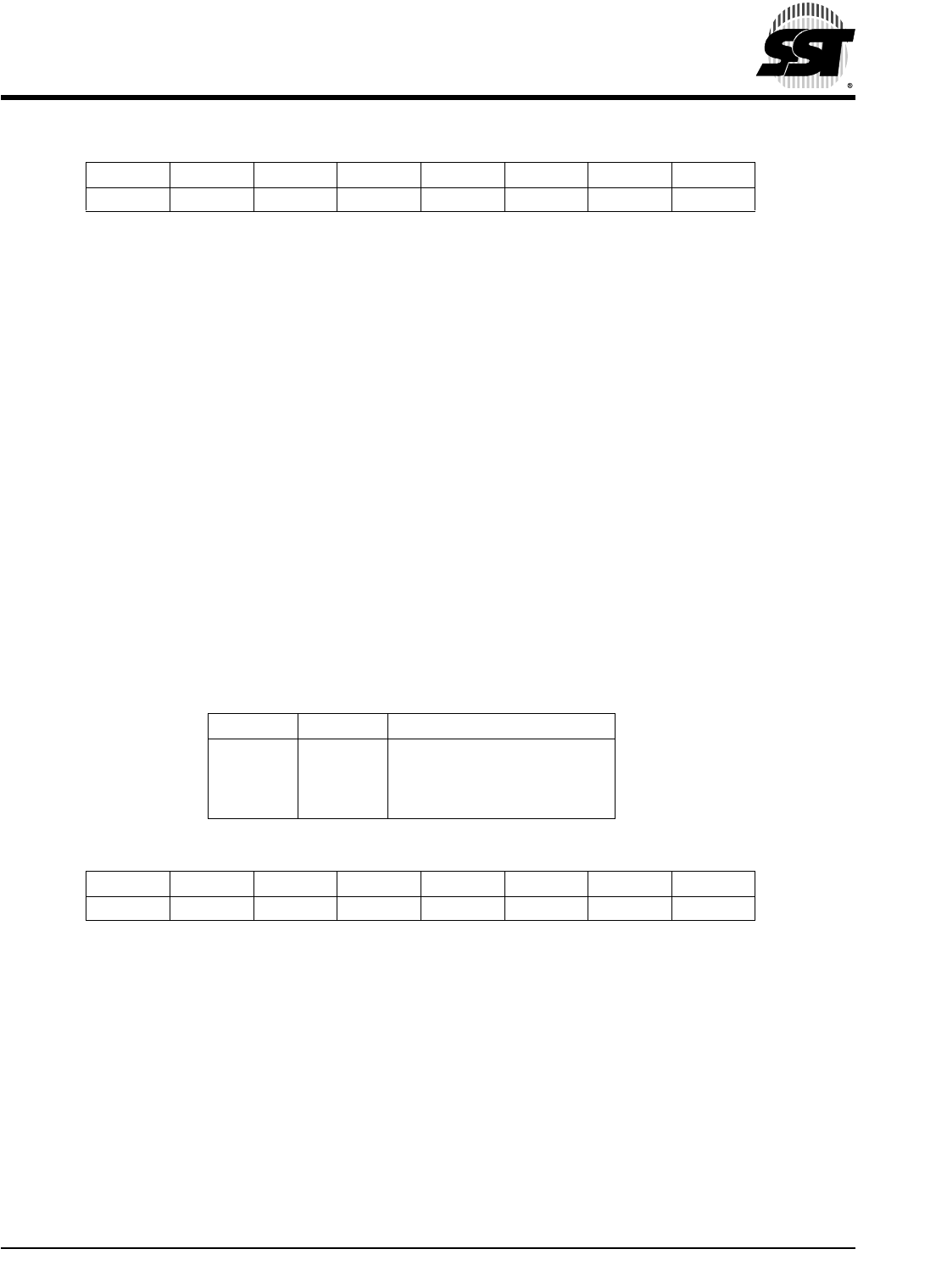

SPI Status Register (SPSR)

Location76543210Reset Value

AAHSPIFWCOL------00xxxxxxb