Data Sheet

FlashFlex51 MCU

SST89E52RD2/RD / SST89E54RD2/RD / SST89E58RD2/RD

SST89V52RD2/RD / SST89V54RD2/RD / SST89V58RD2/RD

21

©2006 Silicon Storage Technology, Inc. S71255-05-000 5/06

Symbol Function

IAPEN Enable IAP operation

0: IAP commands are disabled

1: IAP commands are enabled

SWR Software Reset

See Section 10.2, “Software Reset”

BSEL Program memory block switching bit

See Figures 3-1 through 3-3 and Table 3-2

Symbol Function

FIE Flash Interrupt Enable.

0: INT1# is not reassigned.

1: INT1# is re-assigned to signal IAP operation completion.

External INT1# interrupts are ignored.

FCM[6:0] Flash operation command

000_0001b Chip-Erase

000_1011b Sector-Erase

000_1101b Block-Erase

000_1100b Byte-Verify

1

000_1110b Byte-Program

000_1111b Prog-SB1

000_0011b Prog-SB2

000_0101b Prog-SB3

000_1001b Prog-SC0

000_1001b Prog-SC1

000_1000bEnable-Clock-Double

All other combinations are not implemented, and reserved for future use.

1. Byte-Verify has a single machine cycle latency and will not generate any INT1# interrupt regardless of FIE.

Symbol Function

SFAL Mailbox register for interfacing with flash memory block. (Low order address register).

Symbol Function

SFAH Mailbox register for interfacing with flash memory block. (High order address register).

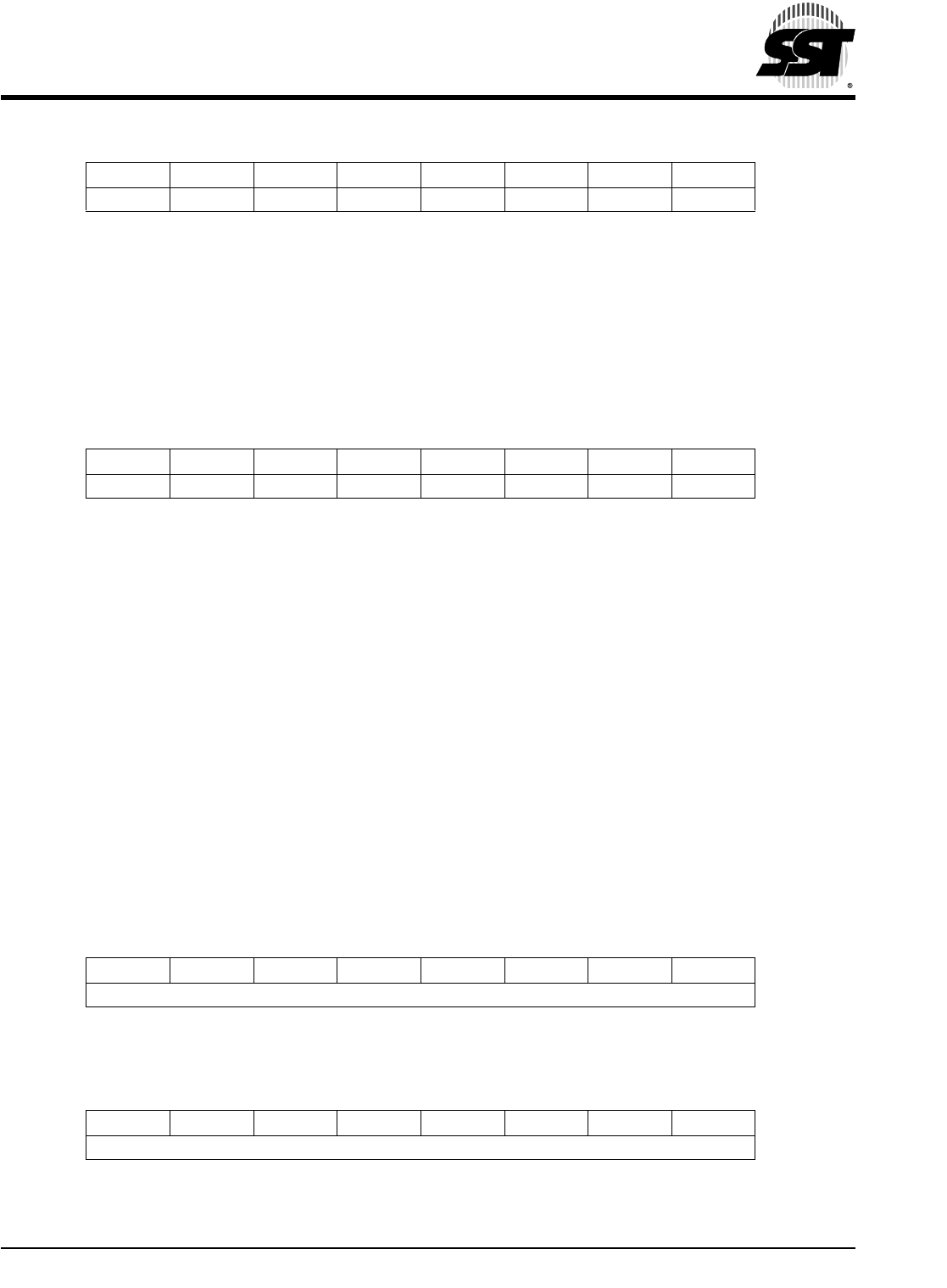

SuperFlash Configuration Register (SFCF)

Location76543210Reset Value

B1H-IAPEN----SWRBSELx0xxxx00b

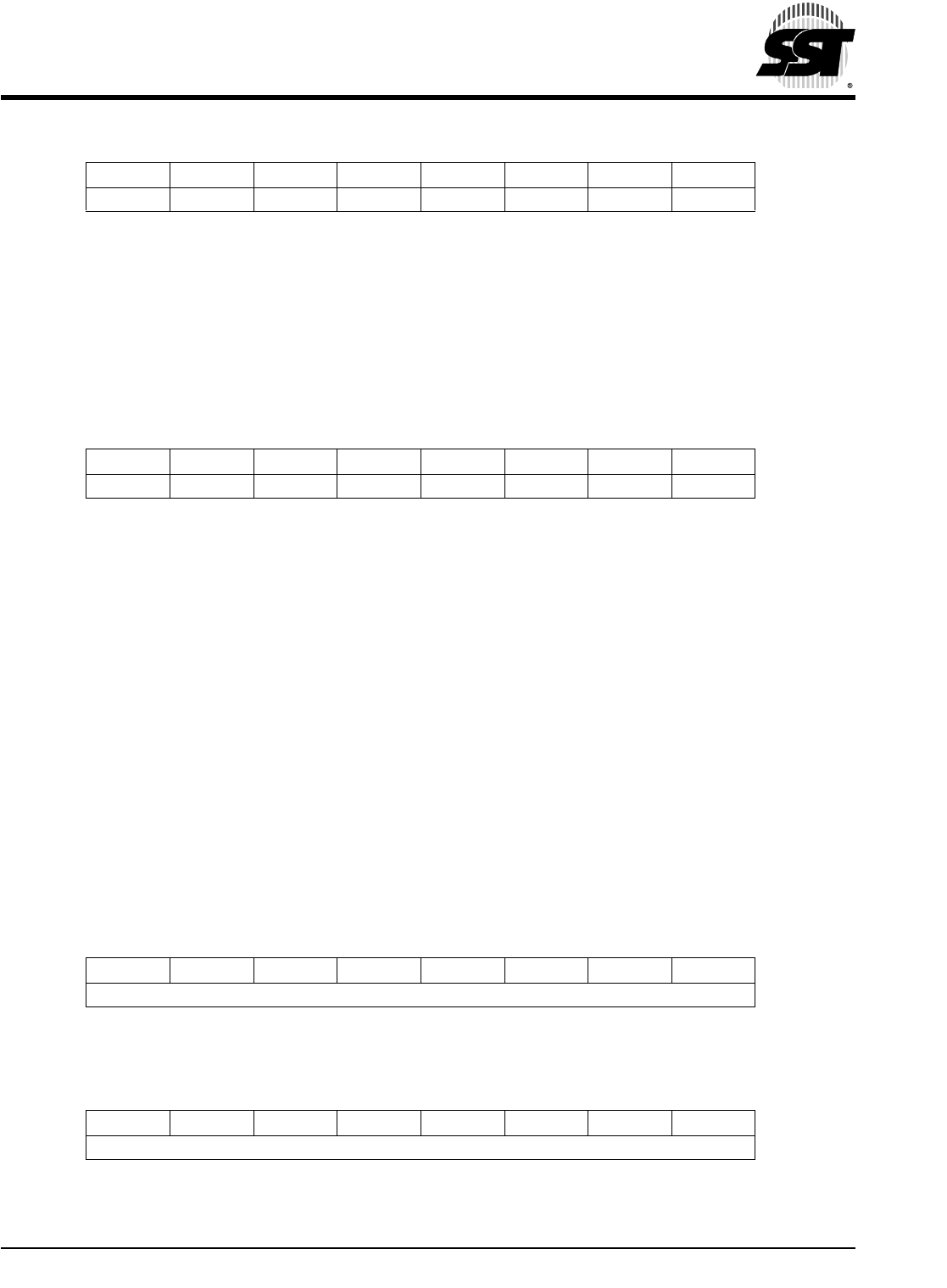

SuperFlash Command Register (SFCM)

Location76543210Reset Value

B2H FIE FCM6 FCM5 FCM4 FCM3 FCM2 FCM1 FCM0 00H

SuperFlash Address Registers (SFAL)

Location76543210Reset Value

B3H SuperFlash Low Order Byte Address Register 00H

SuperFlash Address Registers (SFAH)

Location76543210Reset Value

B4H SuperFlash High Order Byte Address Register 00H