10

Data Sheet

FlashFlex51 MCU

SST89E52RD2/RD / SST89E54RD2/RD / SST89E58RD2/RD

SST89V52RD2/RD / SST89V54RD2/RD / SST89V58RD2/RD

©2006 Silicon Storage Technology, Inc. S71255-05-000 5/06

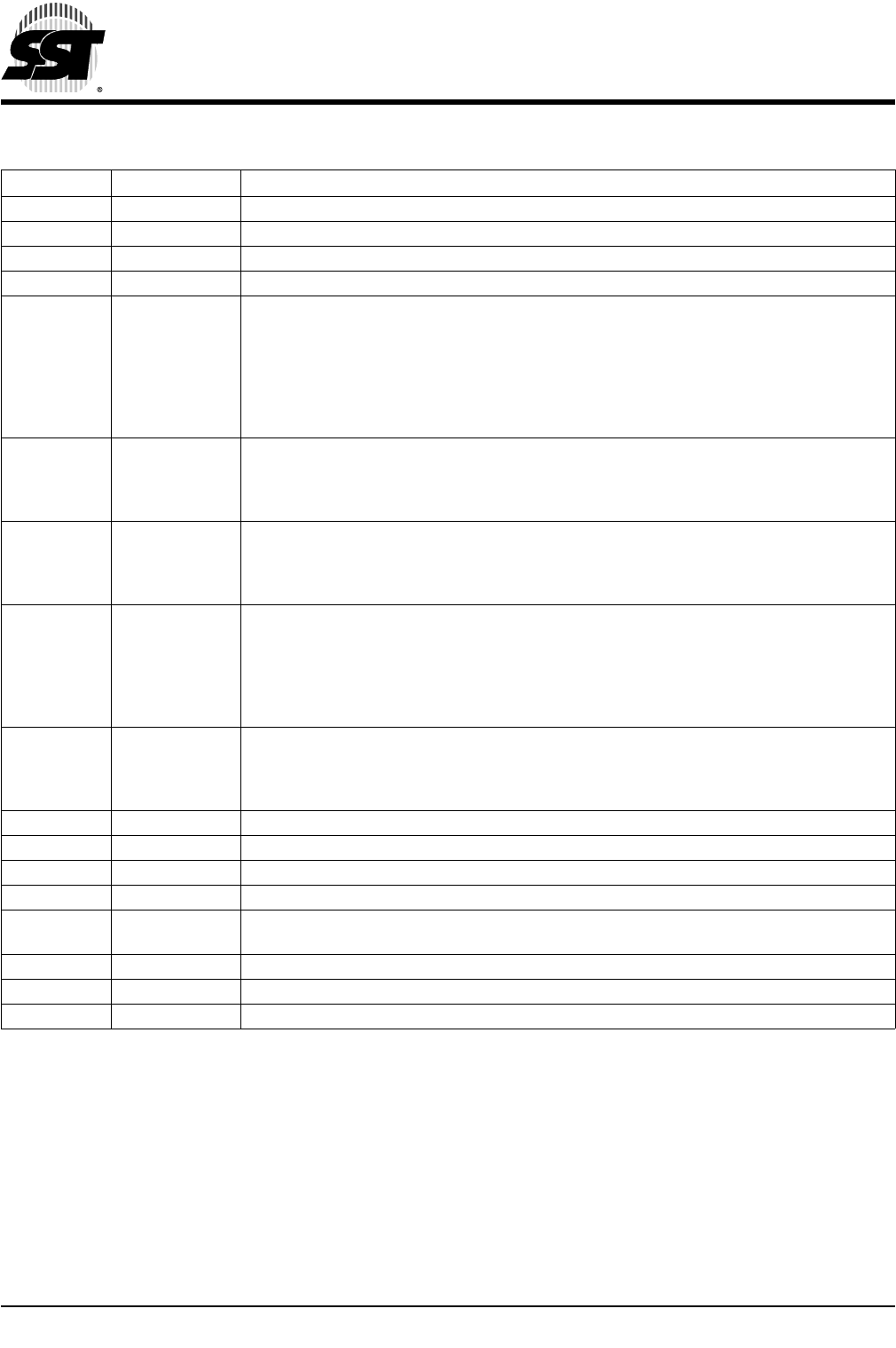

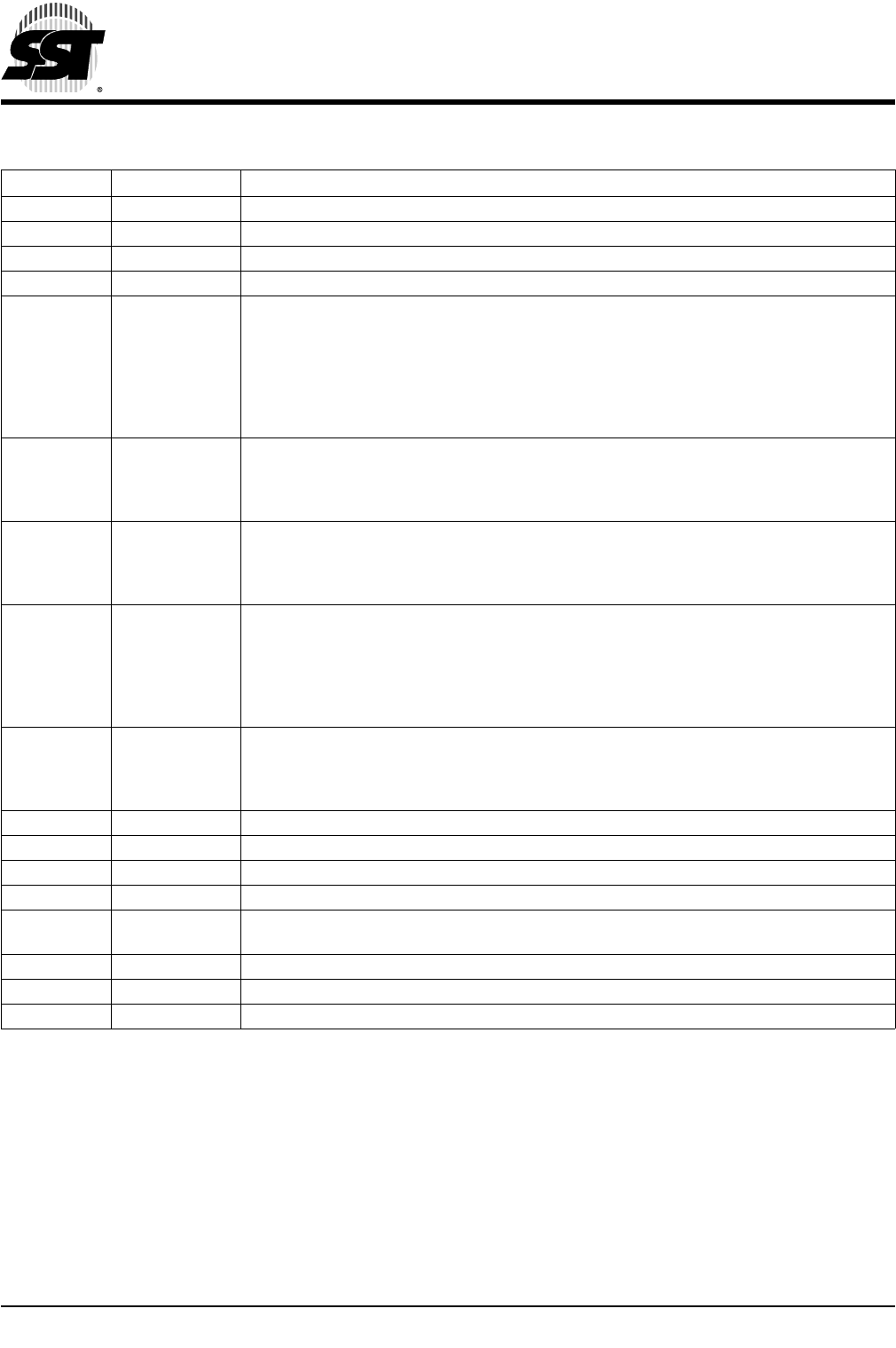

P3[4] I T0: External count input to Timer/Counter 0

P3[5] I T1: External count input to Timer/Counter 1

P3[6] O WR#: External Data Memory Write strobe

P3[7] O RD#: External Data Memory Read strobe

PSEN# I/O Program Store Enable: PSEN# is the Read strobe to External Program Store. When the

device is executing from Internal Program Memory, PSEN# is inactive (V

OH

). When the

device is executing code from External Program Memory, PSEN# is activated twice each

machine cycle, except when access to External Data Memory while one PSEN# activation

is skipped in each machine cycle. A forced high-to-low input transition on the PSEN# pin

while the RST input is continually held high for more than 20 machine cycles will cause the

device to enter External Host mode for programming.

RST I Reset: While the oscillator is running, a high logic state on this pin for two machine cycles

will reset the device. After a reset, if the PSEN# pin is driven by a high-to-low input transition

while the RST input pin is held high, the device will enter the External Host mode, otherwise

the device will enter the Normal operation mode.

EA# I External Access Enable: EA# must be driven to V

IL

in order to enable the device to fetch

code from the External Program Memory. EA# must be driven to V

IH

for internal program

execution. However, Security lock level 4 will disable EA#, and program execution is only

possible from internal program memory. The EA# pin can tolerate a high voltage

2

of 12V.

ALE/PROG# I/O Address Latch Enable: ALE is the output signal for latching the low byte of the address

during an access to external memory. This pin is also the programming pulse input

(PROG#) for flash programming. Normally the ALE

3

is emitted at a constant rate of 1/6 the

crystal frequency

4

and can be used for external timing and clocking. One ALE pulse is

skipped during each access to external data memory. However, if AO is set to 1, ALE is dis-

abled.

P4[3:0]

5

I/O with internal

pull-ups

Port 4: Port 4 is an 4-bit bi-directional I/O port with internal pull-ups. The port 4 output buff-

ers can drive LS TTL inputs. Port 4 pins are pulled high by the internal pull-ups when ‘1’s are

written to them and can be used as inputs in this state. As inputs, port 4 pins that are exter-

nally pulled low will source current because of the internal pull-ups.

P4[0] I/O Bit 0 of port 4

P4[1] I/O Bit 1 of port 4

P4[2] / INT3# I/O Bit 2 of port 4 / INT3# External interrupt 3 input

P4[3] / INT2# I/O Bit 3 of port 4 / INT2# External interrupt 2 input

XTAL1 I Crystal 1: Input to the inverting oscillator amplifier and input to the internal clock generator

circuits.

XTAL2 O Crystal 2: Output from the inverting oscillator amplifier

V

DD

I Power Supply

V

SS

I Ground

T2-1.0 1255

1. I = Input; O = Output

2. It is not necessary to receive a 12V programming supply voltage during flash programming.

3.ALE loading issue: When ALE pin experiences higher loading (>30pf) during the reset, the MCU may accidentally enter into modes

other than normal working mode. The solution is to add a pull-up resistor of 3-50 KΩ to V

DD

, e.g. for ALE pin.

4. For 6 clock mode, ALE is emitted at 1/3 of crystal frequency.

5. Port 4 is not present on the PDIP package.

TABLE 2-1: Pin Descriptions (Continued) (2 of 2)

Symbol Type

1

Name and Functions