Data Sheet

FlashFlex51 MCU

SST89E52RD2/RD / SST89E54RD2/RD / SST89E58RD2/RD

SST89V52RD2/RD / SST89V54RD2/RD / SST89V58RD2/RD

81

©2006 Silicon Storage Technology, Inc. S71255-05-000 5/06

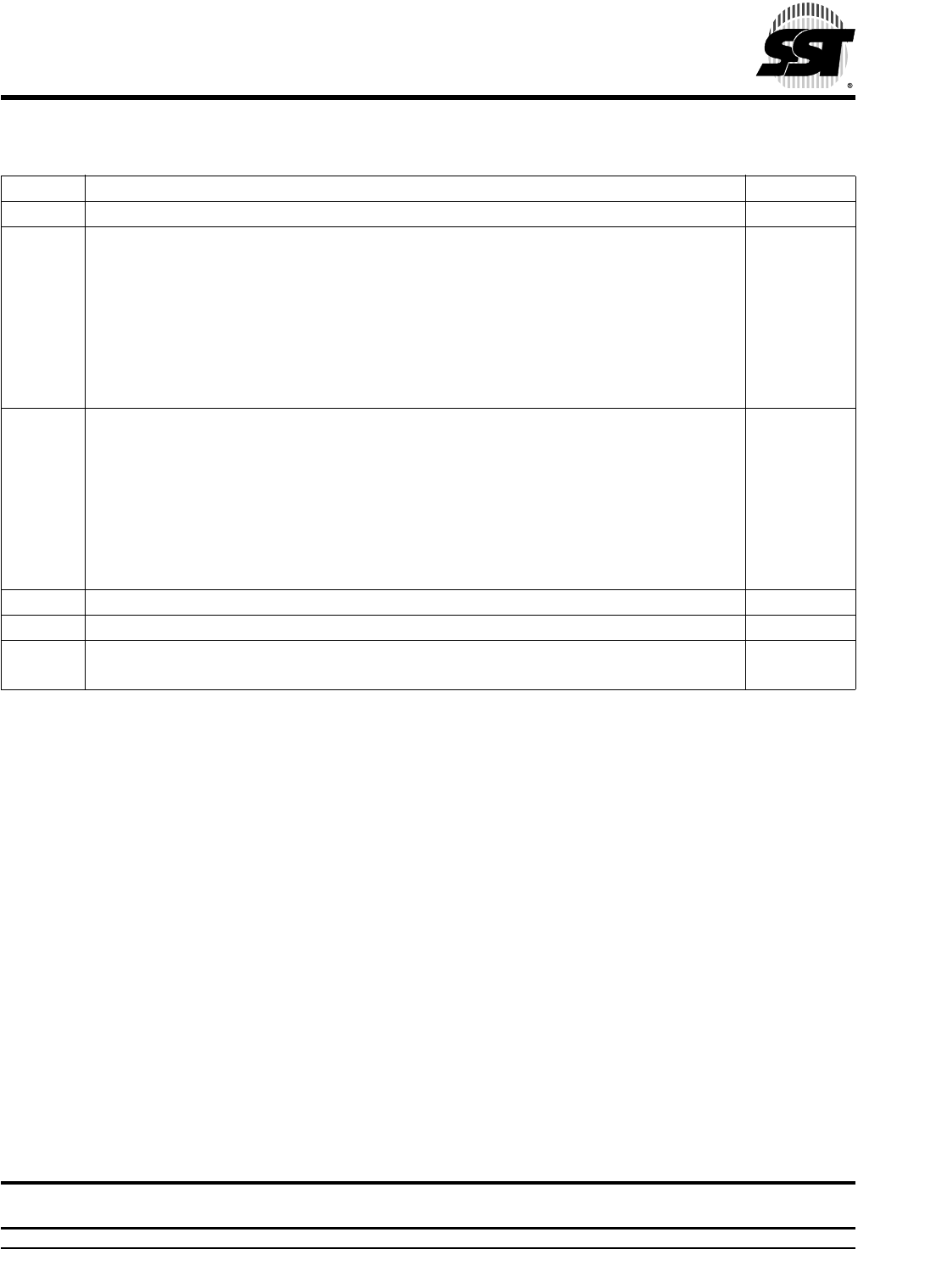

TABLE 16-1: Revision History

Number Description Date

00

• Initial Release

Mar 2004

01

• Changed MPNs of SST89E/V5xRD2 PDIP devices to SST89E/V5xRD

• Removed SST89E/V516RD2 devices and associated MPNs

• Removed all industrial temperature PDIP devices and associated MPNs

• Clarified Surface Mount Temperatures in “Absolute Maximum Stress Ratings” on

page 63

• Changes in Tables 14-6 and 14-7:

– Removed the minimum V

DD

=2V for I

DD

Power-down (also Figure 14-13)

– Removed the 12 MHz values for I

DD

Sep 2004

02

• Corrected MPN breakdown definition for “2” to read “Port 4 present”

• Corrected the SPI control Register definition for CPHA on page 29

• Added SST89E/V5xRD industrial temperature PDIP devices and associated MPNs

• Added RoHS compliance information on page 1 and in the “Product Ordering Infor-

mation” on page 76

• Corrected the solder temperature profile under “Absolute Maximum Stress Rat-

ings” on page 63

• Removed references to External Host Mode programming

Mar 2005

03

• Made changes to add WQFN package

Mar 2006

04

• Revised Figure 3-1 on page 11. Changed 7HHH to 1HHH.

Apr 2006

05

• Revised Figure 3-1 on page 11. Changed 8000H to 2000H.

• Changed document status from Preliminary Specification to Data Sheet.

May 2006

Silicon Storage Technology, Inc. • 1171 Sonora Court • Sunnyvale, CA 94086 • Telephone 408-735-9110 • Fax 408-735-9036

www.SuperFlash.com or www.sst.com