74

Data Sheet

FlashFlex51 MCU

SST89E52RD2/RD / SST89E54RD2/RD / SST89E58RD2/RD

SST89V52RD2/RD / SST89V54RD2/RD / SST89V58RD2/RD

©2006 Silicon Storage Technology, Inc. S71255-05-000 5/06

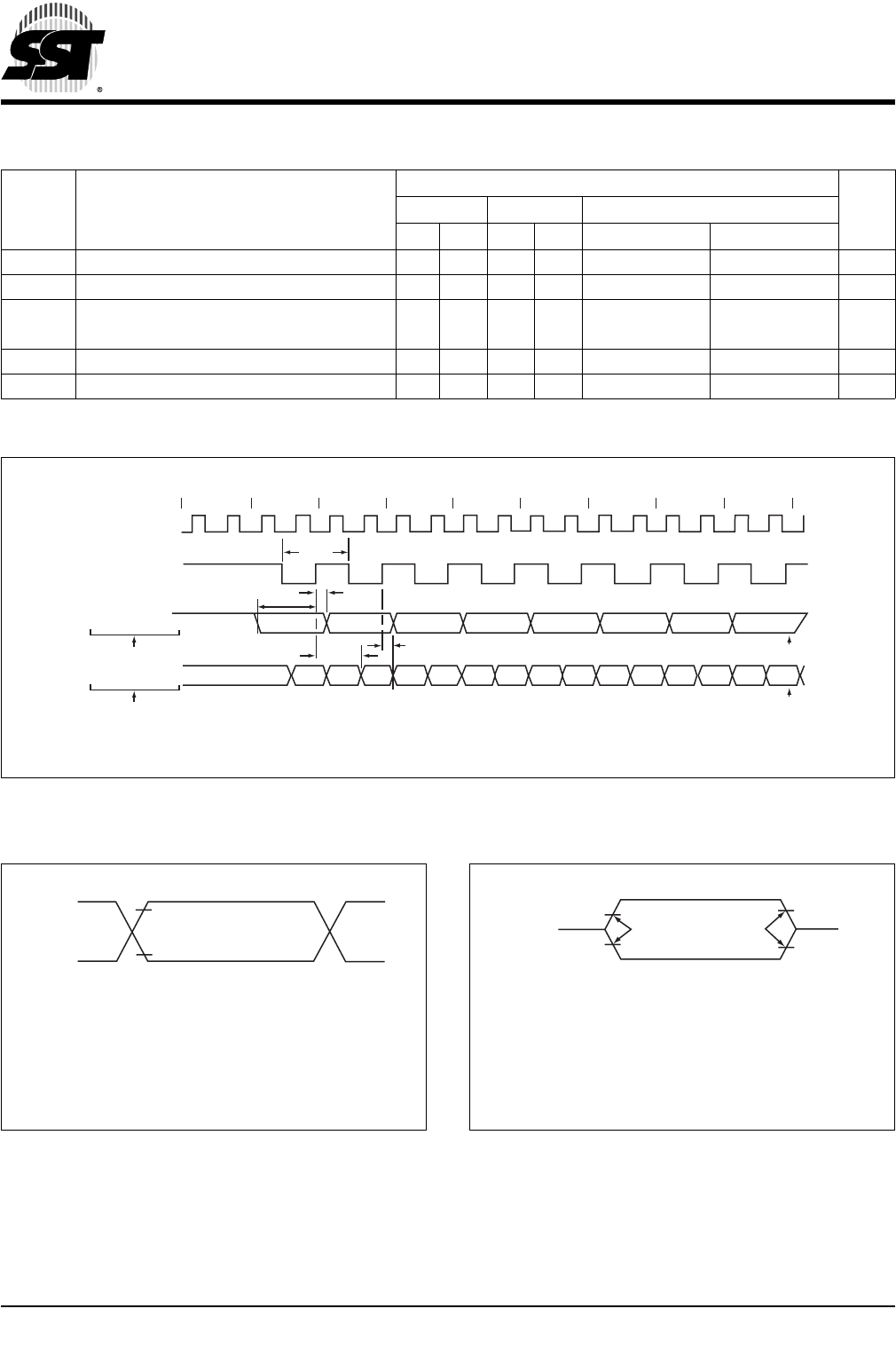

FIGURE 14-7: Shift Register Mode Timing Waveforms

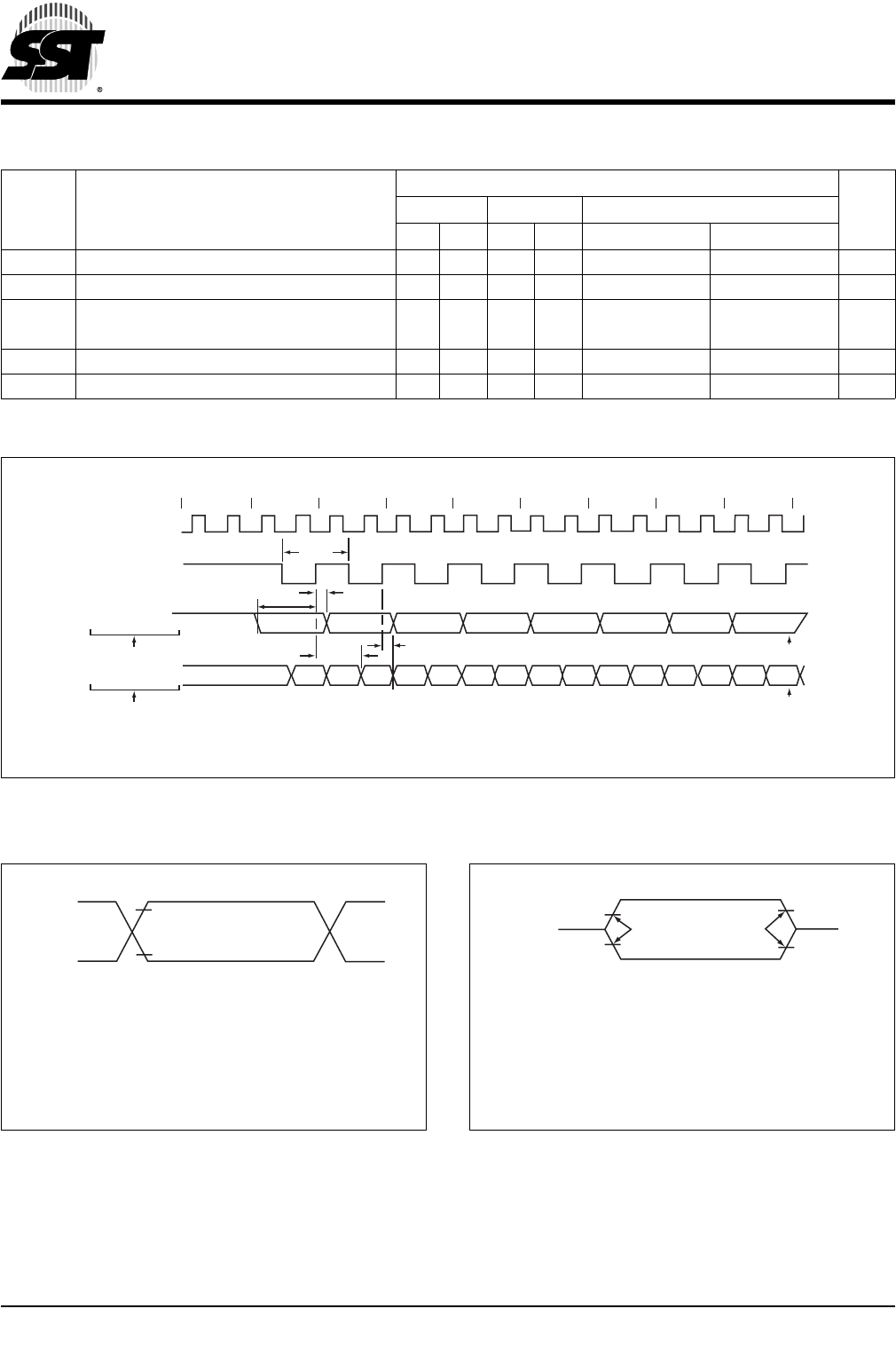

FIGURE 14-8: AC Testing Input/Output Test

Waveform

FIGURE 14-9: Float Waveform

TABLE 14-10: Serial Port Timing

Symbol Parameter

Oscillator

Units

12MHz 40MHz Variable

Min Max Min Max Min Max

T

XLXL

Serial Port Clock Cycle Time 1.0 0.3 12T

CLCL

µs

T

QVXH

Output Data Setup to Clock Rising Edge 700 117 10T

CLCL

- 133 ns

T

XHQX

Output Data Hold After Clock Rising Edge 50 2T

CLCL

- 117 ns

02T

CLCL

- 50 ns

T

XHDX

Input Data Hold After Clock Rising Edge 0 0 0 ns

T

XHDV

Clock Rising Edge to Input Data Valid 700 117 10T

CLCL

- 133 ns

T14-10.0 1255

1255 F39.0

ALE

0

INSTRUCTION

CLOCK

OUTPUT DATA

WRITE TO SBUF

VALID VALID VALID VALID VALID VALID VALID VALID

INPUT DATA

CLEAR RI

01 234 567

T

XLXL

T

QVXH

T

XHQX

T

XHDV

T

XHDX

SET TI

SET R I

1 2 3 4 5 6 7 8

V

LT

AC Inputs during testing are driven at V

IHT

(V

DD

-0.5V) for Logic "1" and

V

ILT

(0.45V) for a Logic "0". Measurement reference points for inputs and

outputs are at V

HT

(0.2V

DD

+ 0.9) and V

LT

(0.2V

DD

- 0.1)

V

HT

V

IHT

V

ILT

1255 F40.0

Note: V

HT

- V

HIGH

Test

V

LT

- V

LOW

Test

V

IHT

-V

INPUT

HIGH Test

V

ILT

- V

INPUT

LOW Test

For timing purposes, a port pin is no longer floating when a 100 mV

change from load voltage occurs, and begins to float when a 100 mV

change from the loaded V

OH

/V

OL

level occurs. I

OL

/I

OH

= ± 20mA.

V

LOAD

+0.1V

V

LOAD

-0.1V

V

OH

-0.1V

Timing Reference

Points

V

OL

+0.1V

V

LOAD

1255 F41.0